協(xié)處理器概述

ARM架構(gòu)通過支持協(xié)處理器來擴(kuò)展處理器的功能。ARM架構(gòu)的處理器支持最多16個協(xié)處理器,通常稱為CP0~CP15。下述的協(xié)處理器被ARM用于特殊用途:

CP15:提供系統(tǒng)控制功能,主要用于配置MMU、TLB和Cache等功能。

CP14:主要用于控制系統(tǒng)Debug功能。

CP10、CP11:兩個協(xié)處理器一起提供了對浮點(diǎn)運(yùn)算和向量操作的支持,這兩個協(xié)處理器主要用于控制和配置浮點(diǎn)功能和高級SIMD指令擴(kuò)展。

其他協(xié)處理器被ARM保留用于將來使用。

本文主要說說CP15協(xié)處理器。

CP15協(xié)處理器總覽

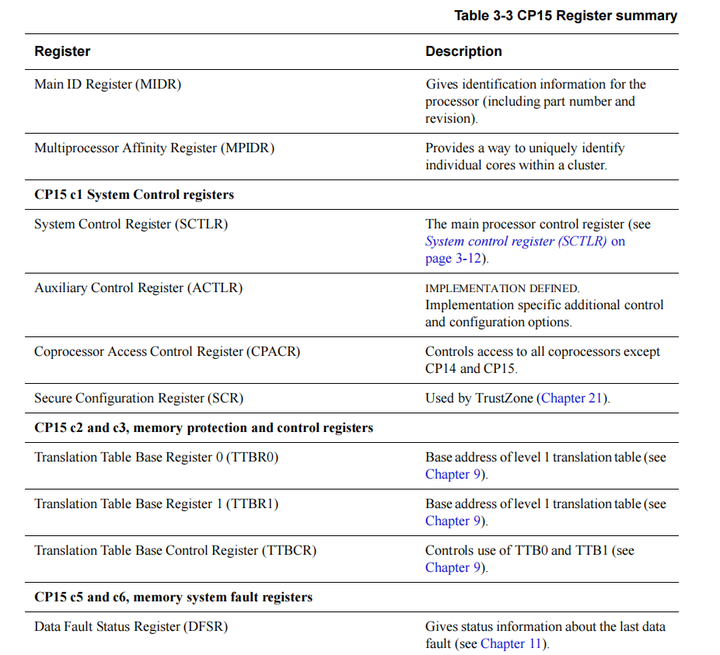

CP15是系統(tǒng)控制協(xié)處理器,主要用于對ARM處理器核心支持的許多特性功能進(jìn)行配置。CP15協(xié)處理器支持16個32位主寄存器(primary register),命名為c0~c15。c0~c15主寄存器各自又有多個32位的物理寄存器(physical register)。CP15協(xié)處理器的大多數(shù)寄存器不能在USR模式下訪問,只能在除USR模式外的其他模式下訪問。下面列出c0~c15中比較常用的寄存器:

| primary register | physical register | 描述 |

|---|---|---|

| c0 | MIDR | 主ID寄存器,用于記錄版本信息 |

| c0 | MPIDR | 多核處理器情況下,提供一種方法來唯一標(biāo)識集群中的各個核心 |

| c1 | SCTLR | 系統(tǒng)控制寄存器 |

| c1 | ACTLR | 輔助控制寄存器 |

| c1 | CPACR | 協(xié)處理器訪問控制寄存器,控制訪問除了CP14和CP15的協(xié)處理器 |

| c1 | SCR | 安全配置寄存器,被TrustZone使用 |

| c2、c3 | TTBR0 | 一級轉(zhuǎn)換頁表基址寄存器0 |

| c2、c3 | TTBR1 | 一級轉(zhuǎn)換頁表基址寄存器1 |

| c2、c3 | TTBCR | 頁表轉(zhuǎn)換控制寄存器 |

| c5、c6 | DFSR | 數(shù)據(jù)異常(Data Fault)狀態(tài)寄存器 |

| c5、c6 | IFSR | 指令異常(Instruction Fault)狀態(tài)寄存器 |

| c5、c6 | DFAR | 數(shù)據(jù)異常(Data Fault)地址寄存器 |

| c5、c6 | IFAR | 指令異常(Instruction Fault)地址寄存器 |

| c7 | branch predictor | cache和分支預(yù)測管理功能 |

| c7 | barrier | 數(shù)據(jù)和指令屏障操作 |

| c8 | TLB | TLB操作 |

| c9 | performance monitors | 性能監(jiān)視器 |

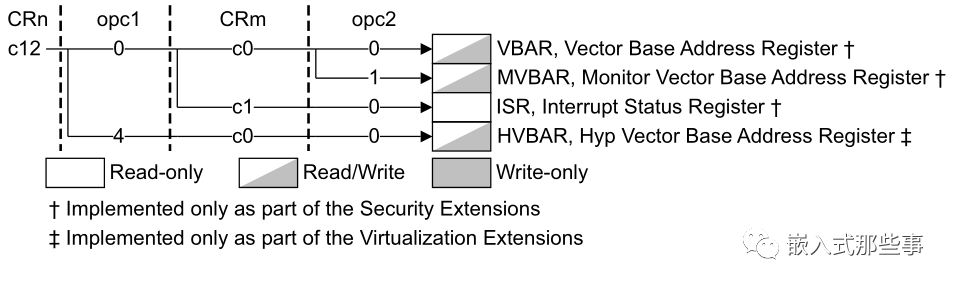

| c12 | VBAR | 提供非監(jiān)視模式處理異常的異常基地址 |

| c12 | MVBAR | 提供監(jiān)視模式處理異常的異常基地址 |

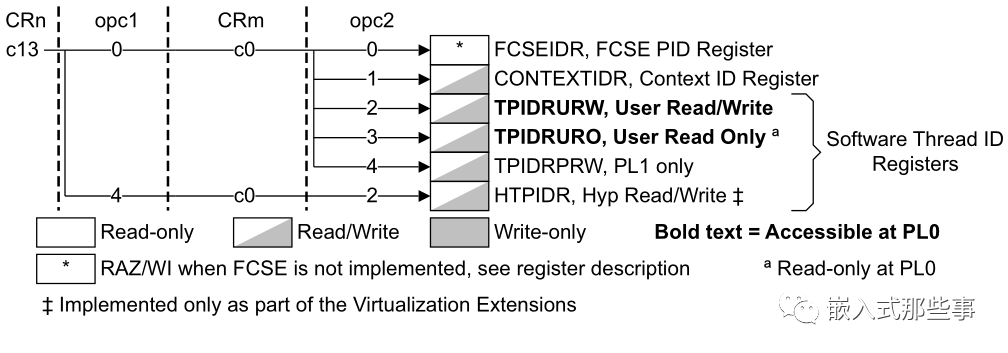

| c13 | CONTEXTIDR | 上下文ID寄存器 |

| c15 | CBAR | 配置基址寄存器,為GIC和本地時鐘類型外設(shè)提供基地址 |

在CP15協(xié)處理器中,c0~c15每個主處理器下面有多個物理寄存器,上述表格只列出了部分常用的物理寄存器。

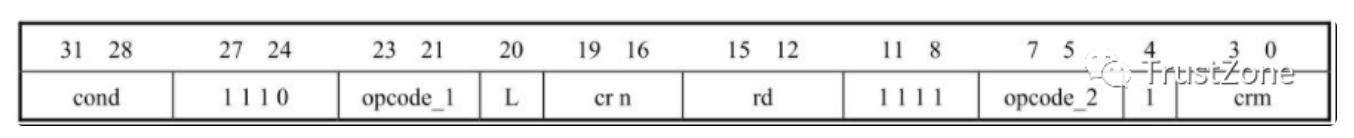

協(xié)處理器操作指令

ARMv7-A體系結(jié)構(gòu)的處理器提供了MRC和MCR指令用于對協(xié)處理器進(jìn)行讀寫操作。MRC指令用于將CP15協(xié)處理器中的寄存器數(shù)據(jù)讀取到ARM通用寄存器中。MCR指令用于將ARM通用寄存器中的數(shù)據(jù)寫入到CP15協(xié)處理器的寄存器中。

MRC

MRC指令的語法如下所示:

?

MRC{cond} coproc, opc1, Rt, CRn, CRm{, opc2}

?

cond為條件碼。

coproc為協(xié)處理器名稱,CP0~CP15協(xié)處理器分別對應(yīng)名稱p0~p15。

opc1為協(xié)處理器要執(zhí)行的操作碼,取指范圍為0~7。

Rt為ARM通用寄存器,用于存儲讀取到的協(xié)處理器寄存器數(shù)據(jù)。

CRn為協(xié)處理器寄存器,對于CP15協(xié)處理器來說,CRn取值范圍為c0~c15。

CRm為協(xié)處理器寄存器,對于CP15協(xié)處理器來說,通過CRm和opc2一起來確定CRn對應(yīng)的具體寄存器。

opc2為可選的協(xié)處理器執(zhí)行操作碼,取指范圍為0~7,當(dāng)不需要的時候要設(shè)置為0。

MRC指令使用示例如下:

?

# 讀取主ID寄存器 MIDR 的數(shù)據(jù)到 R0 中. MRC p15, 0, R0, c0, c0, 0

?

MCR

MCR指令的語法如下所示:

?

MCR{cond} coproc, opc1, Rt, CRn, CRm{, opc2}

?

cond為條件碼。

coproc為協(xié)處理器名稱,CP0~CP15協(xié)處理器分別對應(yīng)名稱p0~p15。

opc1為協(xié)處理器要執(zhí)行的操作碼,取指范圍為0~7。

Rt為ARM通用寄存器,用于存儲要寫入到協(xié)處理器寄存器中的數(shù)據(jù)。

CRn為協(xié)處理器寄存器,對于CP15協(xié)處理器來說,CRn取值范圍為c0~c15。

CRm為協(xié)處理器寄存器,對于CP15協(xié)處理器來說,通過CRm和opc2一起來確定CRn對應(yīng)的具體寄存器。

opc2為可選的協(xié)處理器執(zhí)行操作碼,取指范圍為0~7,當(dāng)不需要的時候要設(shè)置為0。

MCR指令使用示例如下:

?

# 將 R0 中的配置數(shù)據(jù)寫入到 SCTLR MCR p15, 0, R0, c1, c0, 0

?

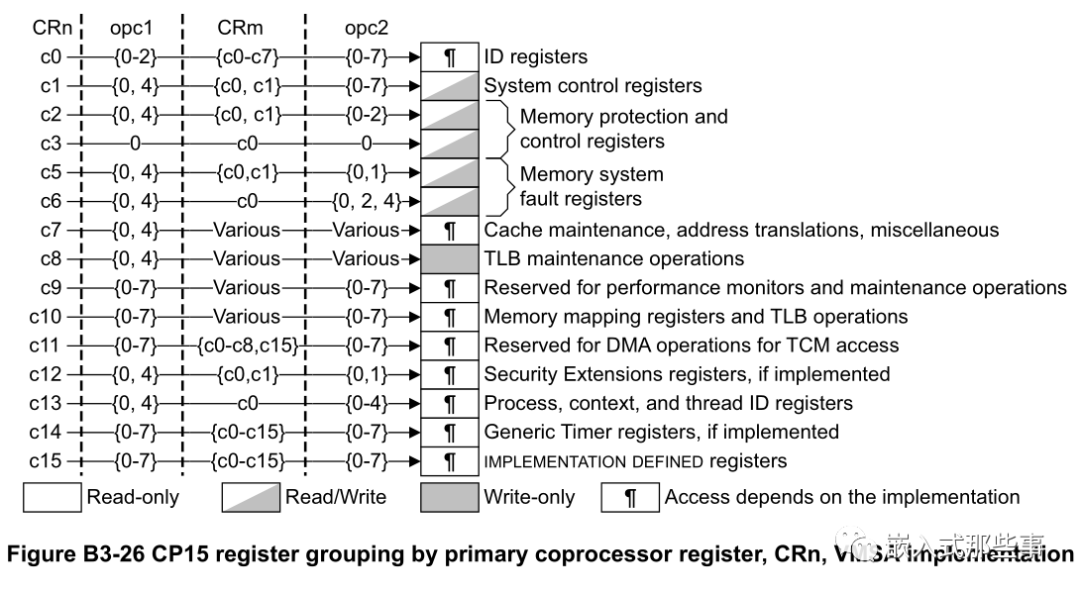

CP15協(xié)處理器主寄存器組成

CP15協(xié)處理器有c0~c15總共16個主寄存器,在每個主寄存器下面,又有多個物理寄存器。下圖總結(jié)了CP15協(xié)處理器的寄存器組織形式:

Snipaste_2023-09-18_20-14-06

上圖對于MRC和MCR指令所要使用到的一些參數(shù)都標(biāo)明了,對于想要訪問CP15協(xié)處理器相關(guān)寄存器,只需要看圖填寫好參數(shù)就行了。下面具體列一下c0~c15各個主寄存器的組成。

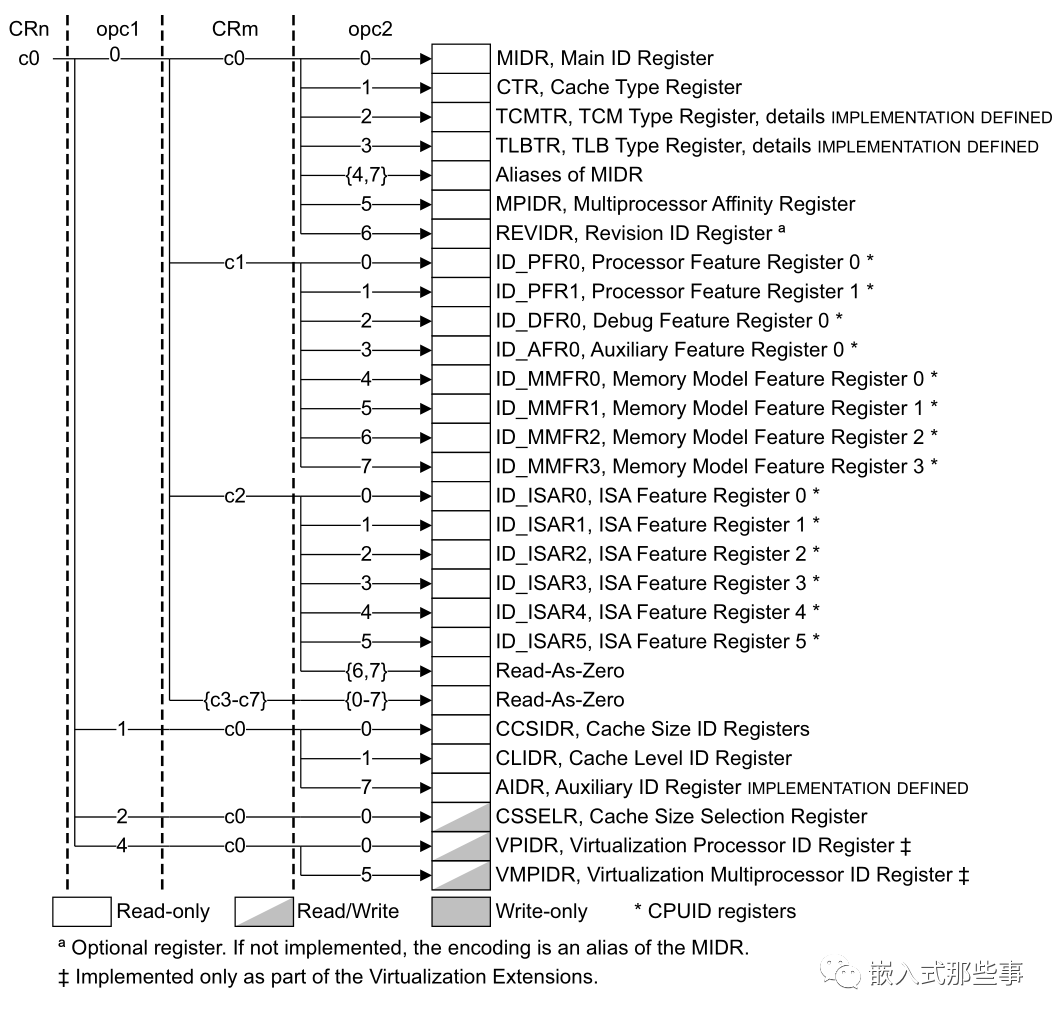

CP15協(xié)處理器c0寄存器組成

主寄存器c0主要提供ID相關(guān)的功能,c0寄存器的組成如下圖所示:

Snipaste_2023-09-18_20-26-50

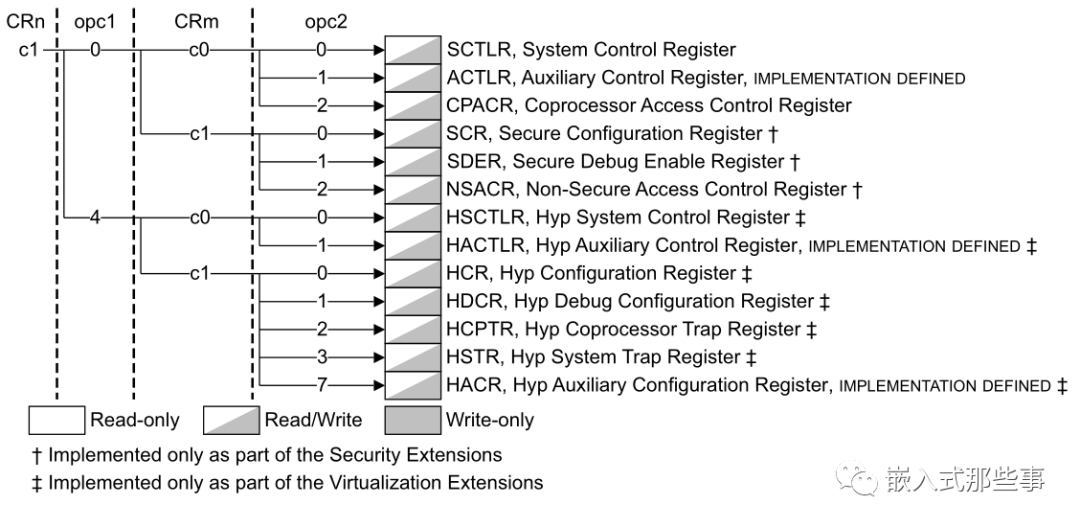

CP15協(xié)處理器c1寄存器組成

主寄存器c1主要提供系統(tǒng)控制相關(guān)的功能,c1寄存器的組成如下圖所示:

Snipaste_2023-09-18_20-31-13

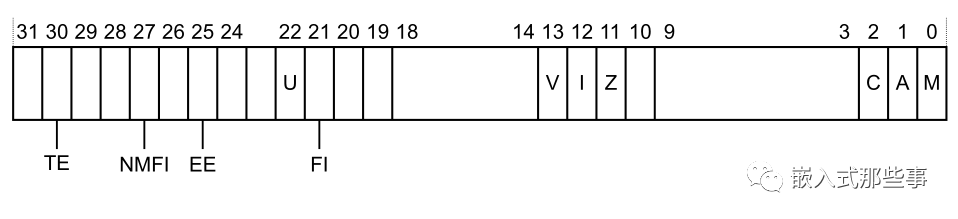

在CP15協(xié)處理器的寄存器中,系統(tǒng)控制寄存器SCTLR是被訪問的比較多的寄存器。對SCTLR寄存器的訪問需要在PL1或者更高的特權(quán)等級。SCTLR寄存器的位關(guān)系如下圖所示:

Snipaste_2023-09-18_20-40-41

| 位 | 標(biāo)志 | 說明 |

|---|---|---|

| 30 | TE | Thumb異常使能,控制在異常發(fā)生時(包括reset),將會進(jìn)入哪種指令集,0:ARM指令集,1:Thumb指令集 |

| 27 | NMFI | 不可屏蔽的FIQ支持,0:軟件可以通過寫CPSR.F位來屏蔽FIQ,1:軟件不可以通過寫CPSR.F位來屏蔽FIQ |

| 25 | EE | 在進(jìn)入異常處理時的大小端模式配置,0:小端,1:大端 |

| 22 | U | 表明是否使用對齊模式 |

| 21 | FI | FIQ配置使能 |

| 13 | V | 選擇異常向量表基址,0:0x00000000,1:0xffff0000 |

| 12 | I | 指令cache使能 |

| 11 | Z | 分支預(yù)測使能 |

| 2 | C | 數(shù)據(jù)cache使能 |

| 1 | A | 對齊檢查使能 |

| 0 | M | MMU使能 |

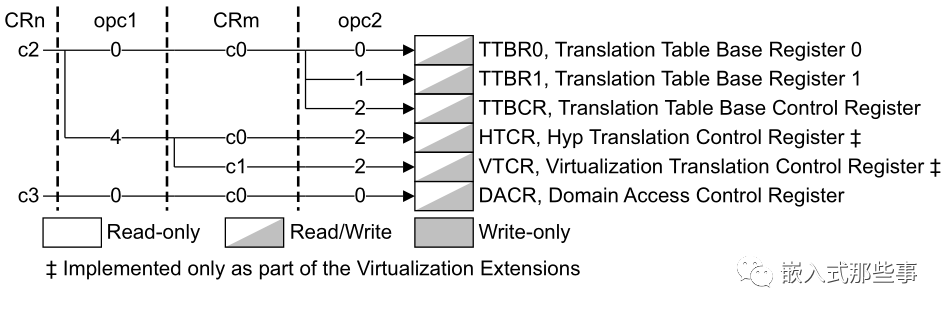

CP15協(xié)處理器c2 c3寄存器組成

主寄存器c2和c3主要提供內(nèi)存保護(hù)和內(nèi)存控制相關(guān)的功能,c2和c3寄存器的組成如下圖所示:

Snipaste_2023-09-18_21-24-50

CP15協(xié)處理器c4寄存器組成

在任何基于ARMv7實現(xiàn)的處理器中,協(xié)處理器CP15的c4寄存器沒有被使用。

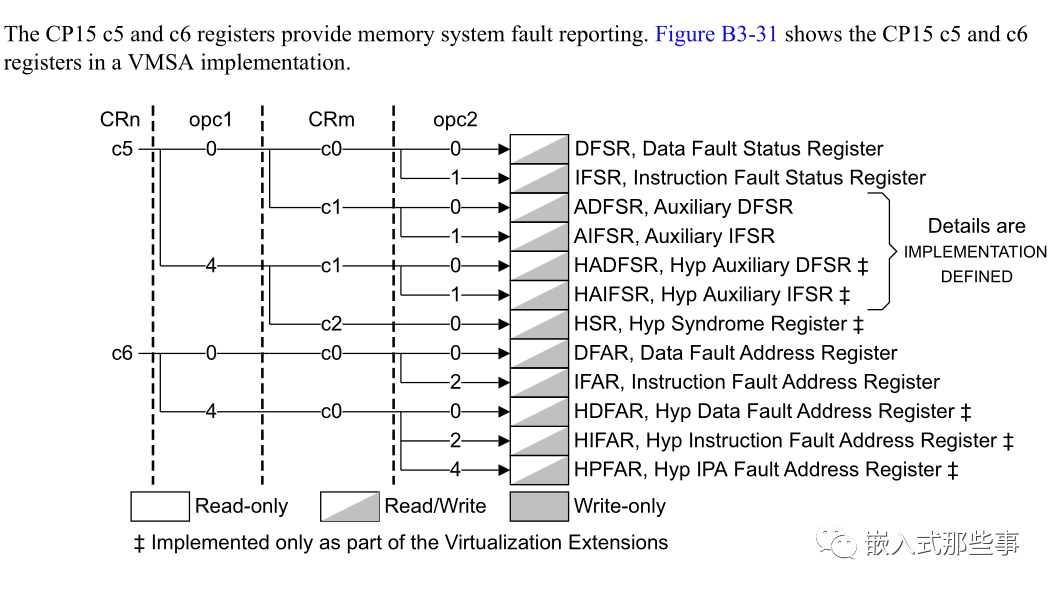

CP15協(xié)處理器c5 c6寄存器組成

主寄存器c5和c6主要提供內(nèi)存系統(tǒng)錯誤上報功能,c5和c6寄存器的組成如下圖所示:

Snipaste_2023-09-18_21-33-47

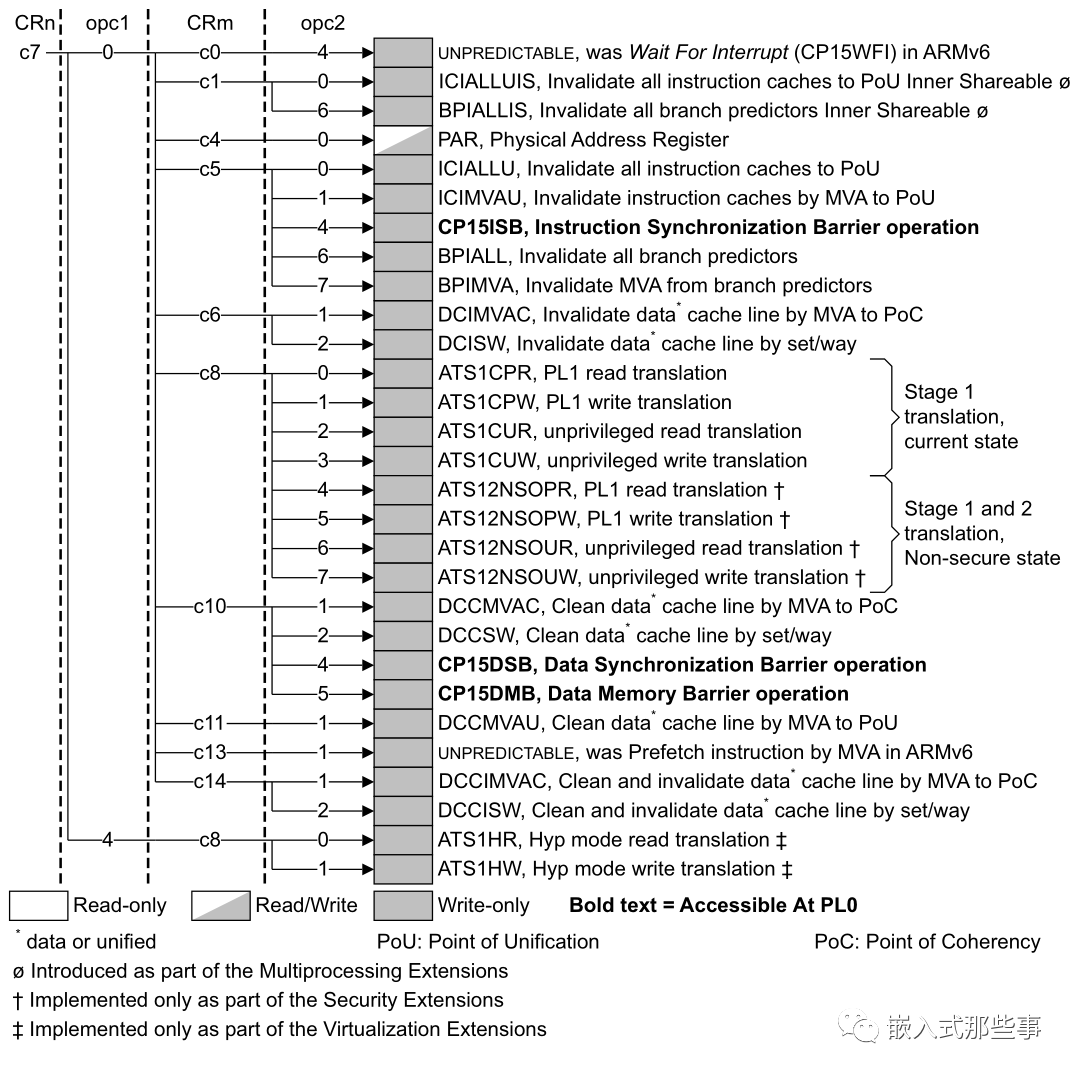

CP15協(xié)處理器c7寄存器組成

主寄存器c7主要提供cache維護(hù),地址轉(zhuǎn)換和內(nèi)存屏障操作相關(guān)的功能,c7寄存器的組成如下圖所示:

Snipaste_2023-09-18_21-36-48

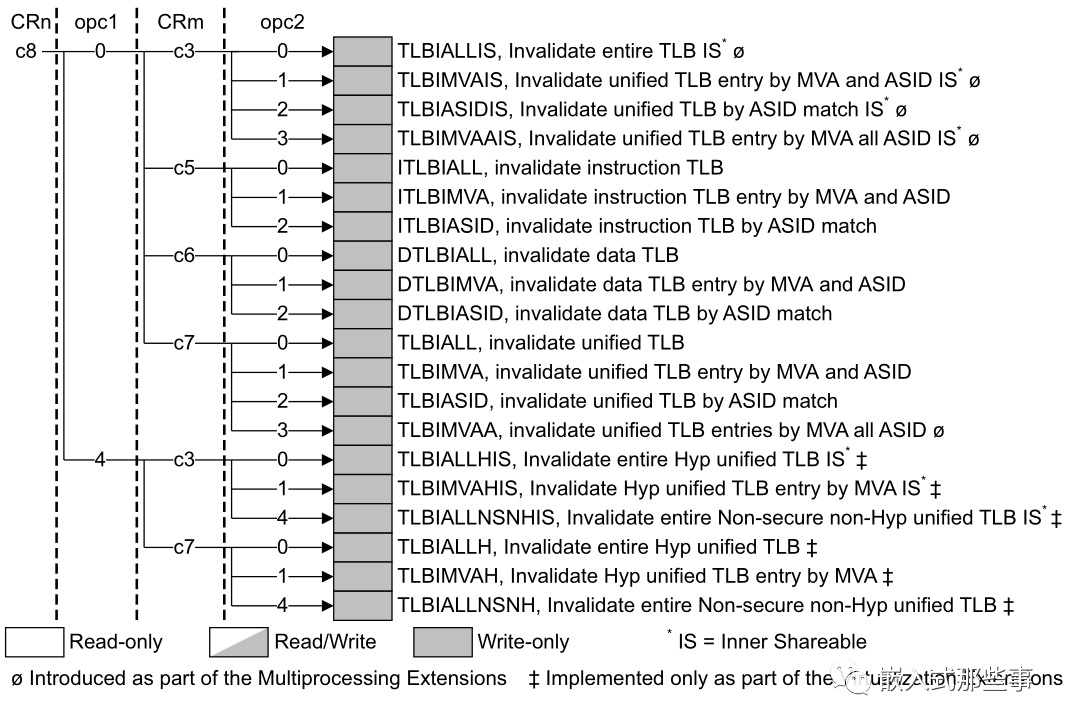

CP15協(xié)處理器c8寄存器組成

主寄存器c8主要提供TLB維護(hù)相關(guān)的功能,c8寄存器的組成如下圖所示:

Snipaste_2023-09-18_21-52-39

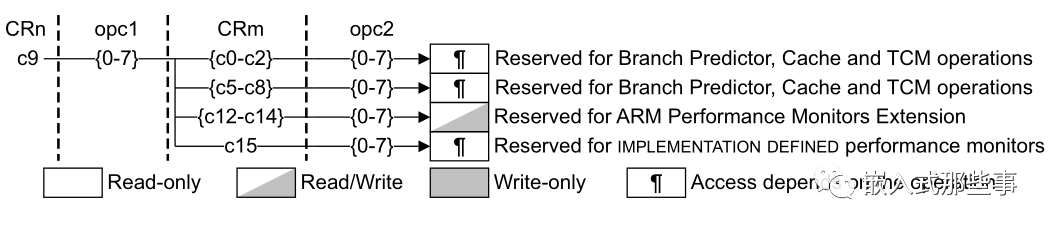

CP15協(xié)處理器c9寄存器組成

主寄存器c9保留用于分支預(yù)測,cache和TCM操作,c9寄存器的組成如下圖所示:

Snipaste_2023-09-18_22-01-45

CP15協(xié)處理器c10寄存器組成

主寄存器c10主要提供內(nèi)存重映射和TLB控制相關(guān)的功能,c10寄存器的組成如下圖所示:

Snipaste_2023-09-18_20-05-48

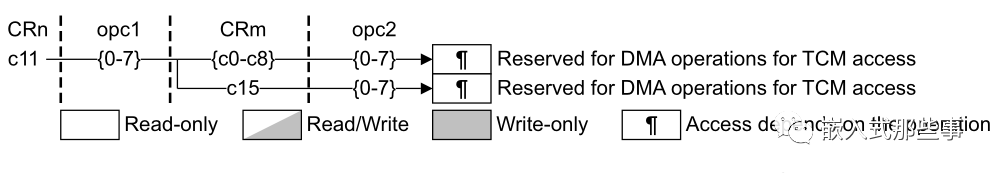

CP15協(xié)處理器c11寄存器組成

主寄存器c11保留用于TCM DMA操作,c11寄存器的組成如下圖所示:

Snipaste_2023-09-19_20-50-17

CP15協(xié)處理器c12寄存器組成

主寄存器c12提供安全擴(kuò)展功能,c12寄存器的組成如下圖所示:

Snipaste_2023-09-19_20-57-07

CP15協(xié)處理器c13寄存器組成

主寄存器c13提供進(jìn)程ID、上下文ID和線程ID處理功能,c13寄存器的組成如下圖所示:

Snipaste_2023-09-19_21-02-11

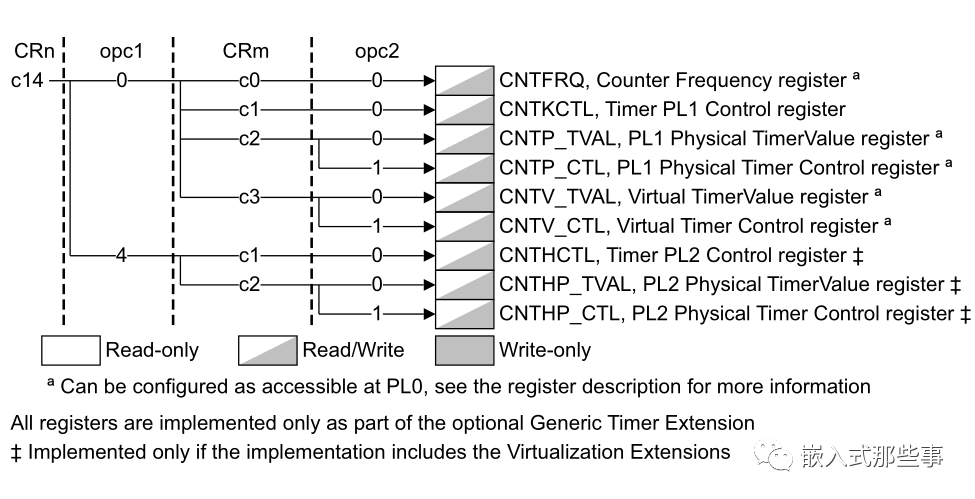

CP15協(xié)處理器c14寄存器組成

主寄存器c14保留用于通用定時器功能,c14寄存器的組成如下圖所示:

Snipaste_2023-09-19_21-55-42

CP15協(xié)處理器c15寄存器組成

主寄存器c15由處理器實現(xiàn)決定。

這里只是簡單的將CP15各個主寄存器的組成列出來了,方便在使用MRC和MCR指令配置CP15主寄存器時,查看指令各個參數(shù)的設(shè)置,以及對照配置的具體寄存器,至于寄存器的具體內(nèi)容由于篇幅原因就不列出來了,CP15寄存器的細(xì)節(jié)可以參考ARMv7AR手冊的B3.17章節(jié)內(nèi)容。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評論