隨著微電子技術的發展,采用現場可編程門陣列(FPGA)進行數字信號處理得到了飛速發展。由于FPGA具有現場可編程的特點,可以實現專用集成電路,因此越來越受到硬件電路設計工程師們的青睞。

目前,在自動化監測與控制儀器和裝置中,大多以8位或16位MCU為核心部件。然而伴隨著生產技術的進步和發展,對監測與控制的要求也在不斷提高,面對日益復雜的監測對象和控制算法,傳統的MCU往往不堪重負。把FPGA運用到這些儀表和設備中,可以減少這些儀器、設備的開發周期,大幅度提升這些儀器的性能,減少總成本和體積。

??? 在低阻值、高精度線圈電阻測試儀中關鍵部分用FPGA硬件電路來實現,可以節省系統的面積開銷、減少所用的芯片數和PCB板塊數,提升系統性能,并降低成本。

??? 低阻值、高精度測試儀系統結構介紹

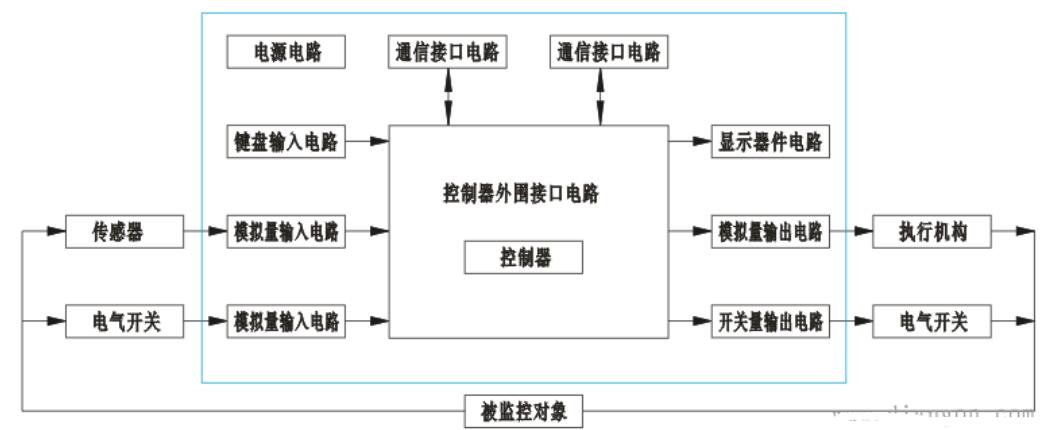

??? 系統的待測體是一個繞有三組銅線圈的機構,外形尺寸大約是7×7×6(mm),外形結構較復雜。由于系統要通過測量待測線圈的阻值,來確定線圈的圈數,因此,要求有比較高的測量精度。按照工廠流水線作業的要求,待測體電阻值均在5Q以下,測量精度在±0.01Ω以內,反應速度在0.8s以內。整個測試系統由數據采樣模塊、數據處理模塊和顯示輸出模塊組成,系統的原理框圖如圖1所示。

???

??? 數據采樣部分

??? 由于本系統要對微小電阻進行精確測量,因此采用四引線制測量法,配以高精度、低溫漂的恒流源。本系統的A/D轉換芯片采用Intersil公司的三位半A/I)轉換器ICL7107,恒流源產生的10mA電流流經待測線圈,產生一個與線圈阻值成正比的壓降。此壓降通過三位半A/D轉換器直接轉換為七段碼形式的十進制數據流,直接送至顯示輸出部分,由LED數碼管顯示輸出。

??? 數據處理部分

??? 這部分有三個功能:

??? (1)將A/D轉換器輸出的七段碼形式的數據轉換為BCD碼;

??? (2)將轉換好的的BCD碼數據進行相減,實現電阻值求差功能;

??? (3)將轉換好的BCD碼數據與設定的上下限進行比較,第2步得到的電阻差值與基準比較值進行比較,實現比較功能。

??? 本文著重介紹這一部分的原理以及實現。針對數據處理部分,這一部分功能可以采用三種方案來實現:

??? (1)采用ALU和7485系列芯片來實現,這種方案需要6個ALU單元(3片處理4位BCD減法的單元和3片處理借位的單元)和18片74LS85芯片(作為數字比較器),占用相當大的系統面積,并且看起來非常繁瑣功能復雜,不直觀。時間延遲大,測量誤差也比較大。

??? (2)完全采用數字組合邏輯電路來實現,這一方案設計門檻比較低,但是占用的系統面積、功耗和測量誤差比第一種方案大的多,達到較難以實現的地步。

??? (3)采用FPGA來實現,把本部分要實現的功能完全集成在一塊FPGA上,與上述兩個方案比較,大大節省面積,系統功能讓人一目了然,而且儀器穩準度更高,反應速度更快

??? 顯示輸出部分

??? 該部分有LED顯示燈(紅、綠)和LED數碼管組成,根據輸入顯示相應結果。

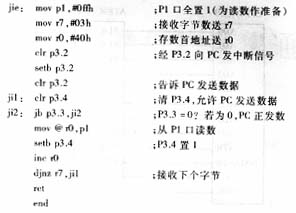

??? FPGA實現的數據處理功能

??? 測試儀中通過待測線圈的壓降通過三位半A/I)轉換器ICL7107后,一輸出的數據(samplel、sample2)均為七段碼形式的十進制三位數(個、十、百位),要求與兩個可調的上下限(BCD碼撥碼輸入)進行比較,若在比較限度內則亮綠燈(greenl、green2),否則亮紅燈(rerll、red2)。另外,兩個采樣值相減,若其差值(sub)在固定范圍以內則亮綠燈(green3),否則亮紅燈(red3)。所有的綠燈亮,總控的綠燈(greerl)才亮,否則,總控紅燈(red)亮。設計方案按照TOP—DOwN的思想對系統進行整體功能劃分,再以BOTTOM—uP方式進行設計輸入,使系統具有層次感(hierarchy),各個功能模塊內包含小的模塊,也便于模塊的重復調用,最后進行芯片的功能、性能等各項模擬。各模塊功能及結構圖介紹如下:

??? datachange(數據轉換)模塊

??? 將輸人為七段碼的數據轉換為BcD碼,輸出轉換后的數據,直接送到顯示輸出部分,在LED數碼管上顯示出來,如圖2所示。

???

??? suball(減法)模塊

??? 系統數據處理的核心部分,包括3個子模塊,來實現采樣的兩個12位BCD碼數之間的相減。其中的核心子模塊為4位BcD減法模塊,通過借位,將此模塊串接,實現模塊復用。將差值送到顯示輸出部分,在LED數碼管上顯示出來,如圖3所示。

??? compareall(比較)模塊

??? 實現轉換后數據(A、B)同設定的上下限(圖中為upperl、lower。1和upper2、lower2)進行比較;減法模塊得出的差值(sub),與設定的基準值c進行比較。最后輸出比較結果,將結果送到顯示輸出部分,以LED顯示燈形式來顯示結果,如圖4所示。

??? lamp模塊

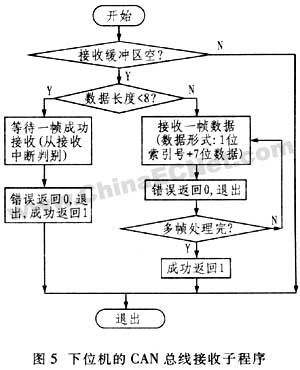

??? 總控顯示燈選擇模塊,根據輸入的結果來決定輸出燈的顏色,如圖5所示。

???

??? 具體算法流程如圖6所示。

??? 仿真驗證

??? 數據處理模塊采用verilog語言編寫,用Maxplus II進行功能仿真,設定upperl與upperl2值均為400(即上限4.0Ω),lowerl與lower2值均為300(即下限3.0Ω),基準比較值C為025(即電阻差值最大限度為0.25),采用六組不同區間數據作為采樣輸入,仿真結果如圖7所示。

??? 波形顯示該算法完全正確,功能達到設計要求。我們采用Altera公司Cyclone系列的EPlC3芯片,進行FPGA仿真,并將其應用于實際系統中,完全達到預期效果。為了檢驗系統的精確度,采用精密數字微歐計進行校驗,該儀表測量準確度達0.1%,分辨率最高可達1mΩ。

??? 本文提出的設計方法,從實際應用來看,節省了面積開銷,儀器穩準度更高,反應速度更快,并且降低了系統整體電路的復雜度,提高了系統集成度。經軟件仿真和實際功能驗證.證明設計可靠、設計方案可行,在實際應用中有較大的實用價值。

電子發燒友App

電子發燒友App

評論