碼流分析儀可用作數(shù)字電視設(shè)備的調(diào)試工具,如檢測(cè)MPEG編碼器、復(fù)用器、調(diào)制解調(diào)器等設(shè)備的輸入輸出碼流是否符合MPEG-2/數(shù)字電視廣播(DVB)標(biāo)準(zhǔn)等。作為標(biāo)準(zhǔn)檢驗(yàn)設(shè)備,碼流分析儀是整個(gè)數(shù)字電視系統(tǒng)的不可缺少的重要設(shè)備。實(shí)際使用中的數(shù)字電視集成系統(tǒng)是一項(xiàng)龐大、復(fù)雜的系統(tǒng)工程,從前端到后端,無(wú)論哪個(gè)環(huán)節(jié)出了差錯(cuò),都將導(dǎo)致整個(gè)系統(tǒng)的癱瘓,為了迅速有效地找出故障源,需要在各測(cè)試點(diǎn)使用碼流分析儀。如圖1所示,可以在測(cè)試點(diǎn)1-4插入碼流分析儀,組成對(duì)傳輸(TS)碼流互聯(lián)層的監(jiān)控、測(cè)試和報(bào)警。

國(guó)外碼流分析儀的研究工作開展比較早,在MPEG-2標(biāo)準(zhǔn)制定的同時(shí),就有碼流分析儀問世,惠普、WG、RS和泰克等公司都推出了各自的碼流分析儀。這幾家公司的產(chǎn)品各有特點(diǎn),而其核心都是基于PC硬件平臺(tái)。雖然性能較穩(wěn)定,但產(chǎn)品價(jià)格均比較昂貴,操作不便。隨著應(yīng)用范圍和規(guī)模的擴(kuò)大,在一個(gè)應(yīng)用場(chǎng)合下,可能會(huì)需要對(duì)較多的測(cè)試點(diǎn)進(jìn)行長(zhǎng)時(shí)間的實(shí)時(shí)碼流分析、監(jiān)控、系統(tǒng)信息采集和報(bào)警管理工作,昂貴的基于PC的測(cè)試設(shè)備顯然無(wú)法滿足這種要求。

為了解決這一缺陷,國(guó)內(nèi)外主要生產(chǎn)廠商都轉(zhuǎn)向選擇在便攜式工控機(jī)上開發(fā)。便攜式工控機(jī)雖然沒有復(fù)雜的外設(shè)連線,但是也存在設(shè)備體積較大和硬件成本昂貴,功能受限于PC硬件和操作系統(tǒng)平臺(tái)穩(wěn)定性等問題。另外,市場(chǎng)上還有一種手持式的測(cè)試儀,有較好的移動(dòng)性,但是也無(wú)法滿足以較低的成本完成實(shí)時(shí)監(jiān)控的要求。針對(duì)中國(guó)目前的應(yīng)用現(xiàn)狀和發(fā)展?fàn)顩r,我們提出以通用的FPGA和RTOS為基礎(chǔ)、基于嵌入式硬件平臺(tái)的設(shè)計(jì)方法,該模塊可以實(shí)現(xiàn)穩(wěn)定和長(zhǎng)期的可靠工作,具有很好的性價(jià)比,可以在現(xiàn)實(shí)應(yīng)用場(chǎng)合廣泛應(yīng)用。

碼流分析功能設(shè)計(jì)

功能設(shè)計(jì)將完全符合以下標(biāo)準(zhǔn):MPEG-2;ISO/IEC 13818-2(System);DVB;ETS 300 468( DVB SI);EN 50083-9(DVB SPI,ASI);ETR 154(Implementation guidelines for MPEG2 systems);ETR 290(Measurement Guidelines);ETR 211( DVB SI Recommendation)。

作為一種測(cè)試儀器,無(wú)論是軟件還是硬件都要保證穩(wěn)定可靠。同時(shí)考慮采用網(wǎng)絡(luò)通信技術(shù),容許用戶通過任何一臺(tái)計(jì)算機(jī)的網(wǎng)絡(luò)瀏覽器訪問圖形化的用戶界面,將碼流分析結(jié)果以最直觀的方式顯示給用戶。嵌入式測(cè)試設(shè)備的設(shè)計(jì)目標(biāo)根據(jù)實(shí)際需要提出,設(shè)計(jì)目的是TS碼流系統(tǒng)監(jiān)測(cè)設(shè)備,在操作和使用的問題上要方便,故障的監(jiān)測(cè)和定位要快速準(zhǔn)確,模塊化的設(shè)計(jì)要求結(jié)構(gòu)緊湊,接口簡(jiǎn)單。針對(duì)這種需要,設(shè)計(jì)目標(biāo)至少要實(shí)現(xiàn)以下功能:

1.對(duì)碼流數(shù)據(jù)進(jìn)行同步字節(jié)提取和包序錯(cuò)誤檢查,并進(jìn)一步對(duì)數(shù)據(jù)根據(jù)ETR290標(biāo)準(zhǔn)進(jìn)行三個(gè)優(yōu)先級(jí)別的語(yǔ)法錯(cuò)誤的檢查;對(duì)數(shù)據(jù)流進(jìn)行實(shí)時(shí)監(jiān)測(cè),及時(shí)紀(jì)錄出錯(cuò)的時(shí)間和錯(cuò)誤的情況;同時(shí)還可根據(jù)用戶的需要制訂硬件觸發(fā)模式,選擇不同的監(jiān)測(cè)項(xiàng)目。

2.實(shí)時(shí)統(tǒng)計(jì)各路PID的當(dāng)前帶寬占用情況,當(dāng)前的TS包的總數(shù)量和傳輸碼率。

3.將TS包中的PSI/SI信息提取并拼接成段,分析段頭部的信息并存儲(chǔ)在特定的數(shù)據(jù)結(jié)構(gòu)中。

4.提取TS流中的PCR信息,計(jì)算其傳輸?shù)拈g隔,同時(shí)作PCR抖動(dòng)的分析,出現(xiàn)錯(cuò)誤及時(shí)報(bào)錯(cuò)。

5.從PES 段中提取PES頭信息以及各路視音頻的基本信息。

6.分析視音頻數(shù)據(jù),根據(jù)TS流中的PCR、PTS和視音頻數(shù)據(jù)來(lái)分析其解碼時(shí)各路視音頻傳輸流標(biāo)準(zhǔn)目標(biāo)解碼器中緩沖器模型的情況,當(dāng)緩沖器出現(xiàn)排空和上溢的錯(cuò)誤時(shí)及時(shí)報(bào)錯(cuò)。 < 這些功能將滿足運(yùn)營(yíng)環(huán)境的現(xiàn)場(chǎng)監(jiān)測(cè)要求。實(shí)際應(yīng)用中這些分析的結(jié)果需要以某種方式提交給用戶觀察。因此,以下的信息顯示是必須的。

1.基本信息:主要向用戶提供關(guān)于TS流的最基本的信息,如TS流的傳輸速率、同步錯(cuò)誤、TS包長(zhǎng)度、視音頻比例、PSI表的簡(jiǎn)要信息等。

2.實(shí)時(shí)監(jiān)測(cè):本界面按照DVB ETR290標(biāo)準(zhǔn)規(guī)定的3級(jí)檢錯(cuò)內(nèi)容而設(shè)計(jì)。

3.節(jié)目信息:顯示描述一個(gè)節(jié)目?jī)?nèi)容的PMT、SDT和EIT的具體信息。

4.帶寬信息:基于PID的帶寬統(tǒng)計(jì)信息。

5.復(fù)用結(jié)構(gòu):TS流中最基本的節(jié)目復(fù)用信息。

6.PSI/SI信息:將2進(jìn)制形式的PSI/SI信息翻譯成文字,以樹的形式顯示,TS流的層次結(jié)構(gòu)一目了然。

7.PCR分析:分析PCR傳送的間隔和抖動(dòng)。

硬件結(jié)構(gòu)

如圖2所示,本設(shè)計(jì)方案選用Altera公司的FPGA――根據(jù)實(shí)際的設(shè)計(jì)容量可以選擇具體的型號(hào)和系列。這里我們將討論輸入輸出、過濾邏輯和控制系統(tǒng)的設(shè)計(jì)思想。

FPGA與TS接口連接的2個(gè)數(shù)據(jù)總線接口TS IN 和TS OUT都是標(biāo)準(zhǔn)的DVB_SPI(EN 50083-9)接口。TS IN 接收外部的TS碼流,送入碼流過濾邏輯系統(tǒng)做進(jìn)一步處理。TS OUT接口將從TS IN收到的碼流環(huán)出,這樣在進(jìn)行碼流分析的同時(shí)就不會(huì)對(duì)傳輸碼流造成任何影響。DVB_SPI接口是LVDS電平信號(hào),可在FPGA上直接接入(參考ALTERA的硬件手冊(cè))。

如果采用DVB_ASI接口,也可以通過Altera提供的IP核來(lái)實(shí)現(xiàn)串/并和并/串轉(zhuǎn)換。所以,原則上除去傳輸變壓器和保護(hù)電路無(wú)需其他接口邏輯芯片。DVB標(biāo)準(zhǔn)的輸入接口有ASI和SPI兩種,兩者的定義和標(biāo)準(zhǔn)不盡相同。針對(duì)輸入接口的不同需要對(duì)輸入信號(hào)進(jìn)行調(diào)整和統(tǒng)一。要從ASI接口的信息中提取TS碼流同步信號(hào),調(diào)整信號(hào)脈沖的占空比使ASI的輸出接口信號(hào)和SPI的相類似。另外,ASI接口輸出有平滑和突發(fā)2種數(shù)據(jù)串?dāng)?shù)模式。為了滿足突發(fā)模式的工作需要,可以將FPGA?片內(nèi)的RAM BLOCK定義成FIFO進(jìn)行高速緩存,使接口滿足不同速率的突發(fā)輸入,最高應(yīng)該可以滿足27MHz并行突發(fā)方式(ASI接口216MHz)的輸入要求。

在FPGA的碼流過濾邏輯單元部分需要設(shè)計(jì)一些重要的硬件控制模塊。MPEG2標(biāo)準(zhǔn)規(guī)定了各壓縮級(jí)別TS碼流的速率。經(jīng)過TS碼流復(fù)用后實(shí)際應(yīng)用中傳輸?shù)拇写a流速率可能>200MHz。因此考慮到NIOS的工作主頻和加載操作系統(tǒng)后的實(shí)際工作效率,我們需要將輸入碼流降低后輸入分析系統(tǒng)。故而硬件中設(shè)計(jì)多種硬件觸發(fā)機(jī)制和硬件過濾器來(lái)滿足這種需求。

根據(jù)ETR290的標(biāo)準(zhǔn)定義,碼流分析功能不是并行處理的模式,而是有先后次序的相對(duì)關(guān)系。根據(jù)不同的優(yōu)先級(jí),先完成同步和連續(xù)性的分析,然后提取PSI信息,最后根據(jù)解析后的PSI信息對(duì)不同PID的節(jié)目TS流進(jìn)行解碼,分析詳細(xì)的PES流信息。輸入信息量的控制可以通過軟件控制的方式實(shí)現(xiàn)。FPGA過濾邏輯設(shè)計(jì)了各種TS流的PID過濾器,將這些豐富的PID過濾器有機(jī)地組合在一起。控制模塊可以通過寫入命令來(lái)控制這些PID過濾器的工作方式和組合結(jié)構(gòu)。

根據(jù)分析流程控制要求,當(dāng)分析不同的信息部分時(shí)控制模塊可以按需要發(fā)送命令改變硬件組合,保證輸入的碼流只與當(dāng)前分析工作有關(guān)。這樣可以完成對(duì)輸入碼流流量的控制而不影響完成設(shè)計(jì)要求。當(dāng)然,這樣設(shè)計(jì)是以犧牲分析實(shí)時(shí)性為代價(jià)的平衡措施,但是獲得的好處也是可預(yù)見的。

Altera公司的FPGA上提供了純軟件設(shè)計(jì)的CPU內(nèi)核NIOS模塊。針對(duì)該內(nèi)核Altera同時(shí)提供了相應(yīng)的編譯器和調(diào)試工具。在NIOS內(nèi)核上我們可以移植一個(gè)小的操作系統(tǒng)。在這個(gè)實(shí)時(shí)操作系統(tǒng)上實(shí)現(xiàn)多任務(wù)調(diào)度和復(fù)雜的計(jì)算。該公司還提供用于FPGA設(shè)計(jì)的其他功能模塊如:UART、TIMER等。軟件支持方面提供了在NIOS內(nèi)核上工作的TCP/IP協(xié)議等。

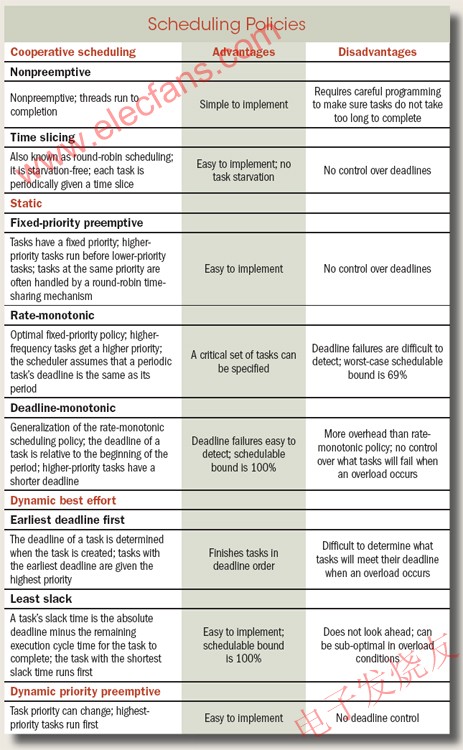

這些資源很方便的滿足了設(shè)計(jì)要求,利用它們實(shí)現(xiàn)分析結(jié)果的輸出要求。我們可以根據(jù)不同的應(yīng)用場(chǎng)合選擇采用不同的通訊接口如RS232/RS485、以太網(wǎng)等。同時(shí),我們可以進(jìn)一步在操作系統(tǒng)上設(shè)計(jì)SNMP協(xié)議,使碼流分析模塊能夠在網(wǎng)絡(luò)環(huán)境和現(xiàn)有的管理系統(tǒng)進(jìn)行連接。這有利于網(wǎng)絡(luò)管理和控制。同樣,在操作系統(tǒng)上設(shè)計(jì)簡(jiǎn)單的WEB SERVER功能也是可行的。用戶通過瀏覽器可以馬上得到分析結(jié)果而無(wú)需安裝任何分析軟件。這些功能設(shè)計(jì)為用戶的實(shí)際應(yīng)用提供了方便,用戶可以根據(jù)不同的現(xiàn)場(chǎng)環(huán)境選擇不同的控制方法。 軟件設(shè)計(jì)基于一個(gè)實(shí)時(shí)操作系統(tǒng)。目前,有很多商業(yè)化的RTOS供選擇,同時(shí),也有Altera的第三方開發(fā)商提供的可在NIOS上運(yùn)行的操作系統(tǒng)。本文介紹另外一種完整的嵌入式的實(shí)時(shí)內(nèi)核μC/OS-II以及應(yīng)用程序結(jié)構(gòu)。μC/OS-II源代碼絕大部分是用C語(yǔ)言寫的,匯編部分只有200行左右。這說(shuō)明該實(shí)時(shí)內(nèi)核可以方便的移植到幾乎所有的嵌入式應(yīng)用類CPU上。事實(shí)上它已經(jīng)被成功的移植在DSP、16/32位MCU上。通過針對(duì)堆棧指針、出入堆棧管理、中斷控制等匯編的修改,可以將μC/OS-II移植到NIOS的平臺(tái)上。如圖3所示,軟件設(shè)計(jì)基于μC/OS-II操作系統(tǒng),設(shè)計(jì)給出了多進(jìn)程設(shè)計(jì)的軟件設(shè)計(jì)結(jié)構(gòu)。

下面簡(jiǎn)單分析不同進(jìn)程的主要功能:

1.TS流處理進(jìn)程。該進(jìn)程完成TS輸入,輸出和內(nèi)存管理的功能。類似于通信系統(tǒng)的物理層,面對(duì)硬件系統(tǒng)的傳輸控制。一般情況下,完成從FIFO中讀取數(shù)據(jù)存儲(chǔ)在SRAM的不同部分中,并提交地址指針。同時(shí)將需要輸出的碼流從SRAM中讀取,按要求寫入輸出FIFO中。在特殊情況下,根據(jù)輸入碼流速率和內(nèi)存情況,調(diào)整輸入數(shù)據(jù)量。

2.MPEGII系統(tǒng)層分析器。根據(jù)MPEG2系統(tǒng)層標(biāo)準(zhǔn)對(duì)輸入碼流的PSI信息進(jìn)行分析。對(duì)提取的各種表格和PID信息進(jìn)行分類存儲(chǔ)。同時(shí)按照SNMP定義的數(shù)據(jù)結(jié)構(gòu)類型重組數(shù)據(jù),根據(jù)需要刷新數(shù)據(jù),將結(jié)果提交給ETR290錯(cuò)誤事件觸發(fā)進(jìn)程。

3.ETR290錯(cuò)誤監(jiān)測(cè)進(jìn)程。按照ETR290的標(biāo)準(zhǔn)進(jìn)行三個(gè)優(yōu)先級(jí)分析和統(tǒng)計(jì)。根據(jù)系統(tǒng)時(shí)鐘分析實(shí)時(shí)信息如PCR抖動(dòng)延時(shí),信息插入間隔等。將分析結(jié)果的數(shù)據(jù)存儲(chǔ)成數(shù)據(jù)結(jié)構(gòu)提交給通信模塊。通過預(yù)先設(shè)計(jì)的故障模式實(shí)現(xiàn)故障提示和報(bào)警。故障模式通過軟件設(shè)定可以是單個(gè)ETR290的錯(cuò)誤產(chǎn)生一個(gè)報(bào)警,也可以是一組錯(cuò)誤產(chǎn)生一個(gè)報(bào)警。太多的錯(cuò)誤報(bào)警會(huì)導(dǎo)致信息堵塞,因此,將相關(guān)的錯(cuò)誤組合成一個(gè)高級(jí)的報(bào)警信息將有利于問題的判斷。

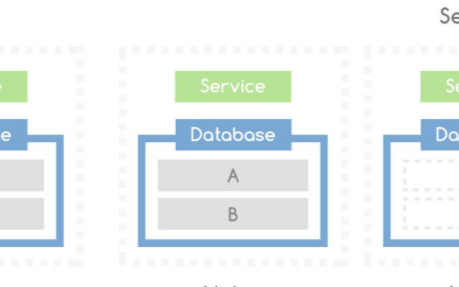

4.通信服務(wù)進(jìn)程。按照TCP/IP協(xié)議和SNMP協(xié)議完成以太網(wǎng)的傳輸控制設(shè)計(jì)。數(shù)據(jù)輸出按照標(biāo)準(zhǔn)的SNMP協(xié)議將統(tǒng)計(jì)信息數(shù)據(jù)庫(kù)和分析數(shù)據(jù)庫(kù)輸送到服務(wù)器端。同時(shí),通過TCP或UDP協(xié)議進(jìn)行控制命令通信。SNMP傳輸?shù)慕y(tǒng)計(jì)信息數(shù)據(jù)可以利用外掛的分析軟件進(jìn)行語(yǔ)義分析。不過要求同時(shí)傳輸硬件本地時(shí)鐘信息作為參考信息。也可以通過控制臺(tái)窗口直接顯示分析數(shù)據(jù)。一旦在通信服務(wù)中添加WEB SERVER功能,則可通過瀏覽器在本地直接顯示分析結(jié)果。

本文結(jié)論

嵌入式的碼流分析設(shè)計(jì)是完全可行和有效的。目前大部分功能已經(jīng)實(shí)現(xiàn)。FPGA的設(shè)計(jì)采用VHDL語(yǔ)言結(jié)構(gòu),分析軟件采用C++語(yǔ)言,RTOS操作系統(tǒng)也可在不同的硬件之間移植;因此,設(shè)計(jì)可以在不同的硬件平臺(tái)上實(shí)現(xiàn)。這為成本的控制留下了靈活的空間。本設(shè)計(jì)目標(biāo)不是取代傳統(tǒng)的碼流分析設(shè)備,而是作為一種補(bǔ)充。目前設(shè)計(jì)的實(shí)時(shí)分析能力有限,分析數(shù)據(jù)刷新在500ms左右。但是,提高FPGA的工作頻率和性能,選用高速SDRAM就可以迅速提高工作性能。所以,性能的提升和功能的擴(kuò)展都有廣闊的前景。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論