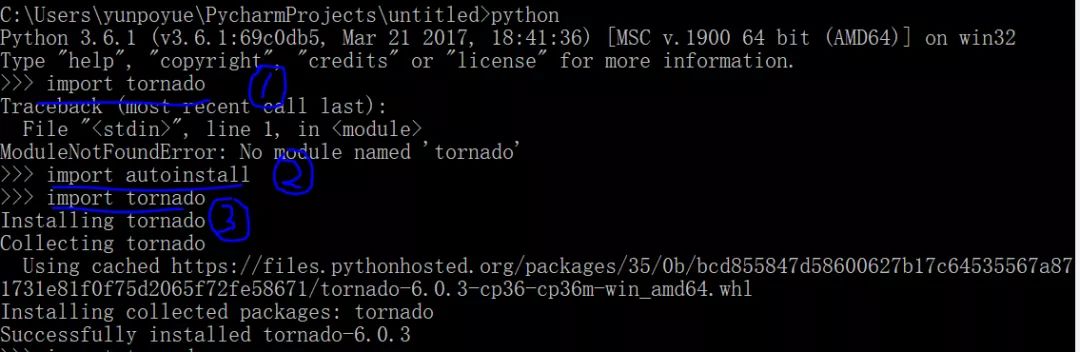

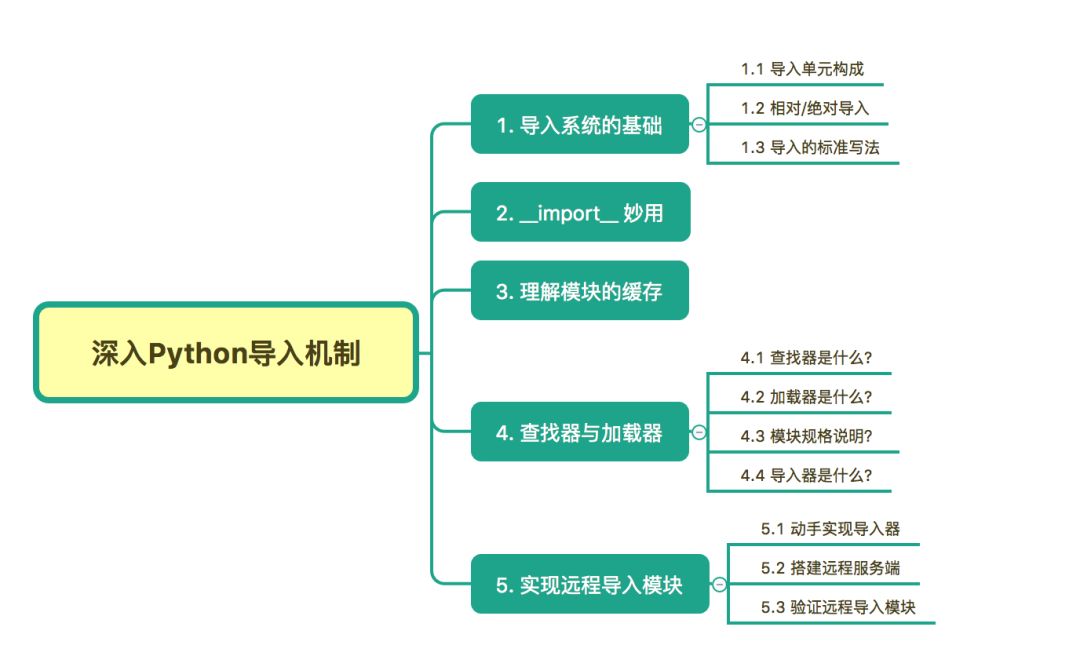

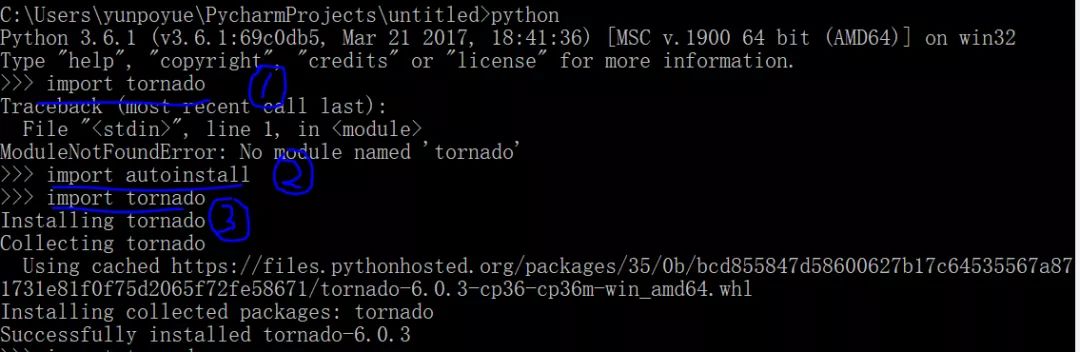

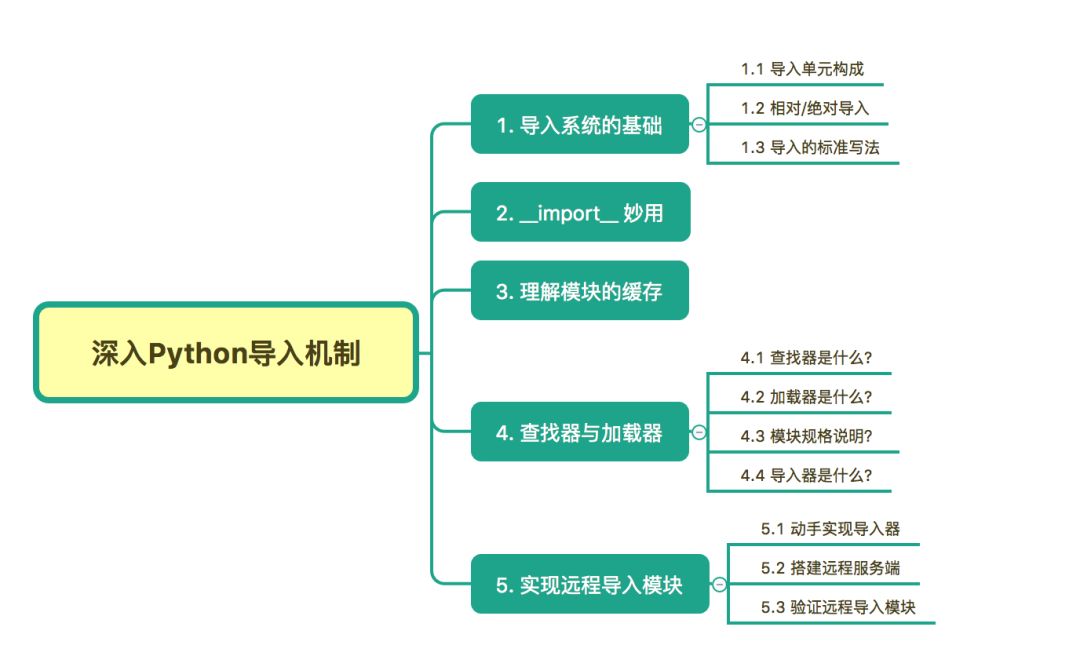

在寫 Python 項目的時候,我們可能經常會遇到導入模塊失敗的錯誤:ImportError: No module named xxx或者ModuleNotFoundError: No module

2020-11-21 11:46:39 2655

2655

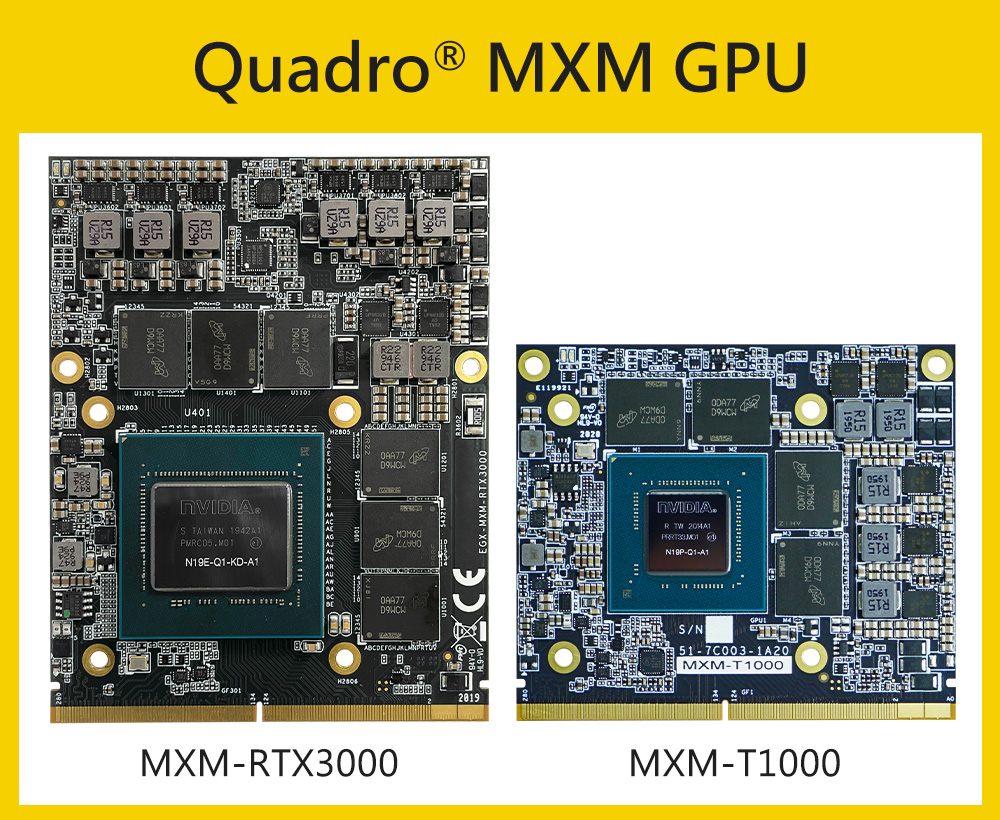

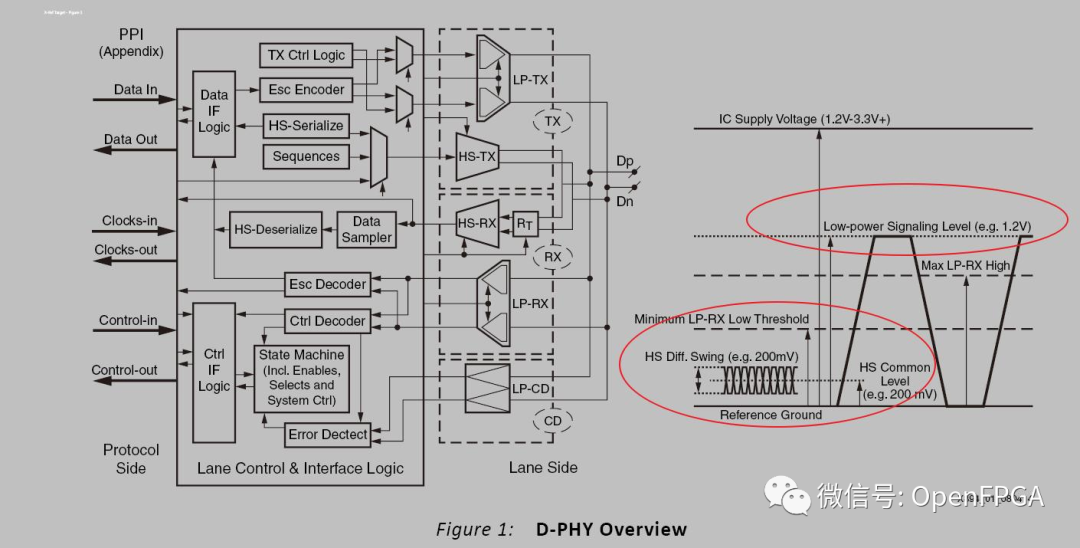

MIPI 接口現在非常流行,國產FPGA目前基本都帶MIPI接口,而AMD-Xilinx是從U+系列開始支持MIPI電平,從國內使用情況來看,7系列FPGA是使用最廣的器件,所以這次使用的FPGA是7系列FPGA使用電阻網絡實現MIPI電平的例子。

2023-04-24 09:30:06 3711

3711

SMC/NVRAM/PRAM到底是什么?如何重置?

2021-09-27 06:12:37

XILINX MIG(DDR3) IP的AXI接口與APP接口的區別以及優缺點對比

2021-11-24 21:47:04

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

支持所有Xilinx器件下載 包括FPGA CPLD ISP Configuration PROM 下載接口電壓:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

下載方案:HS2 二代高速下載方案,下載速度:最大 30Mhz通信方式:USB,下載接口:JTAG 14P 標準接口,支持開發環境:ISE、Vivado,工作電壓:5V(USB 供電),工作電流:56mA@5V,工作溫度:-40℃~+85℃

2023-03-28 13:06:17

我們有一個基于ZYNQ XC7Z030全定制SOC的定制板。該板具有用于PCI Express的7系列FPGA集成模塊。Xilinx是否有可以在PCI Express根端口主機PC上運行的Linux內核模塊驅動程序,以與上述PCI Express端點設備進行交互?蘇雷什P.

2020-08-05 14:13:35

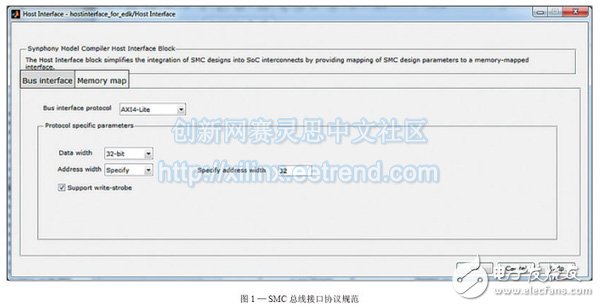

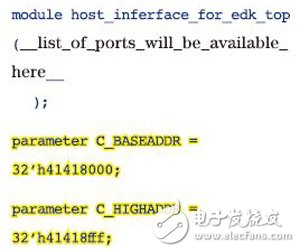

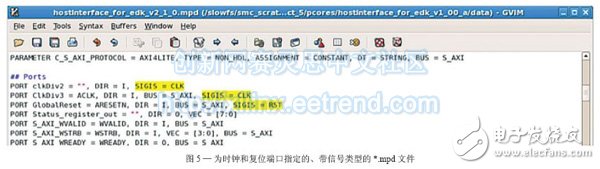

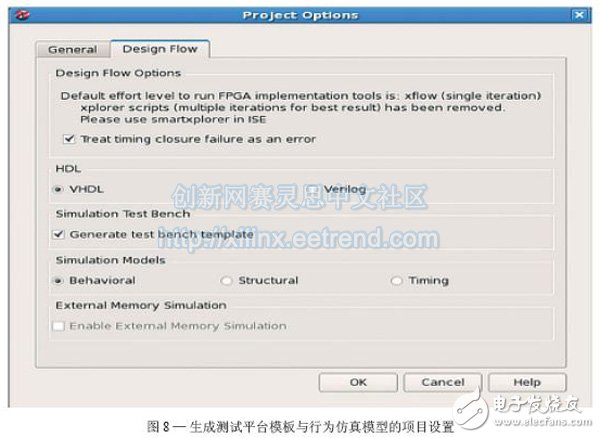

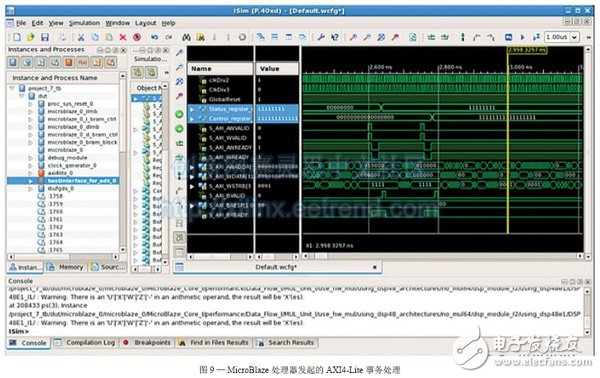

Xilinx的嵌入式系統開發環境EDK

2012-08-17 09:21:44

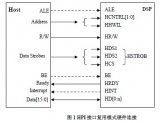

論文以Compaq、Microsoft 等公開的 USB 主機控制器接口規范為基礎,遵循USB 主機的協議規范,開發了獨立于操作系統的USB 主機底層驅動程序,并在S3C2410 平臺上得到了驗證。下面詳細論述主機控制器接口規范及 驅動程序實現。

2020-03-31 06:57:20

本應用指南介紹了如何確定采用主機端口接口在主機COU與TI公司之間傳輸數據所需CPU周期數的方法。

2014-09-23 15:59:26

使用fw 10.20。在做SMC和DIQ cals之后,我想出了增益和端口功率方面的一些錯誤。附加的.csa和.png文件是我正在嘗試測量的子集,手動完成設置,因此我的程序沒有進入圖片。如果您查看

2018-10-16 06:26:50

我買了個ESP8266模塊,搭建了開發環境,導入了一個工程,編譯出錯,如圖請問高手,如何解決?謝謝!

2022-11-15 19:52:21

你好,我用SIM7600CE GSM模塊作為設備,PIC32作為主機,GSM模塊有USB接口(4個虛擬端口),我想和任何一個虛擬端口通信,我在MLA中沒有找到多端口環境的源代碼。

2020-03-09 06:59:18

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

),I2C接口,USART接口,SPI接口和普通的IO。 USB3.0-XILINX-DDR3模塊主要特性●USB傳輸通道已經封裝為透明數據傳輸通道。上位機為C語言的 .dll動態庫,可以被各種編程語言調用

2019-01-15 10:40:28

),I2C接口,USART接口,SPI接口和普通的IO。 USB3.0-XILINX-DDR3模塊主要特性●USB傳輸通道已經封裝為透明數據傳輸通道。上位機為C語言的 .dll動態庫,可以被各種編程語言調用

2018-10-15 10:04:55

),I2C接口,USART接口,SPI接口和普通的IO。 USB3.0-XILINX-DDR3模塊主要特性●USB傳輸通道已經封裝為透明數據傳輸通道。上位機為C語言的 .dll動態庫,可以被各種編程語言調用

2018-10-22 11:21:03

達330Mbytes/s),I2C接口,USART接口,SPI接口和普通的IO。 USB3.0-XILINX-DDR3模塊主要特性●USB傳輸通道已經封裝為透明數據傳輸通道。上位機為C語言的 .dll動態庫,可以被

2018-10-12 11:38:37

),I2C接口,USART接口,SPI接口和普通的IO。 USB3.0-XILINX-DDR3模塊主要特性●USB傳輸通道已經封裝為透明數據傳輸通道。上位機為C語言的 .dll動態庫,可以被各種編程語言調用

2019-01-08 14:28:08

),I2C接口,USART接口,SPI接口和普通的IO。 USB3.0-XILINX-DDR3模塊主要特性●USB傳輸通道已經封裝為透明數據傳輸通道。上位機為C語言的 .dll動態庫,可以被各種編程語言調用

2019-01-22 14:17:09

cc2564modx藍牙主機控制器接口(HCI)模塊

2016-02-25 14:35:04

labview連接SMC100A signal generator 產生波形,labview的程序模塊。

2016-10-19 10:12:57

的PCIExpress?Gen3兼容接口的正確解決方案。NVMe SSD存儲簡介NVM Express(NVMe)定義了主機控制器通過PCI Express以SSD形式訪問的接口。NVM Express僅使用兩個

2020-09-03 16:07:35

接口進行仿真驗證),提前規避和發現一些不滿足AXI總線規范的設計問題。本文就跟大家分享如何使用Xilinx AXI VIP對自己的設計搭建仿真驗證環境的方法。本文參考的Xilinx官方文檔為

2022-10-09 16:08:45

如何利用Xilinx FPGA和存儲器接口生成器簡化存儲器接口?

2021-05-06 07:23:59

半主機是什么?如何構建用于非半主機環境的應用程序?

2021-12-02 06:32:54

教你如何搭建Xilinx開發環境本教程將向你介紹如何搭建Xilinx開發環境,需要具備什么樣的條件,注意哪些問題,及如何搭建最完美的開發環境!詳細資料下載:[hide][/hide]

2012-02-29 09:23:19

有這樣的設備嗎:一臺主機,帶FPGA協處理器,通過PXIe總線連接一個收發一體的射頻模塊,可以在主機上開發軟件,實現與射頻模塊的通信。模塊要求有點高:IO接口:支持IO數據輸入輸出,支持數字通道;自

2022-07-18 15:03:11

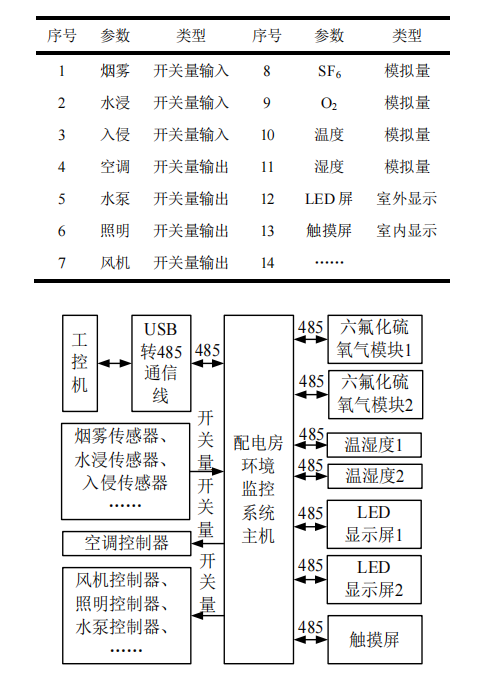

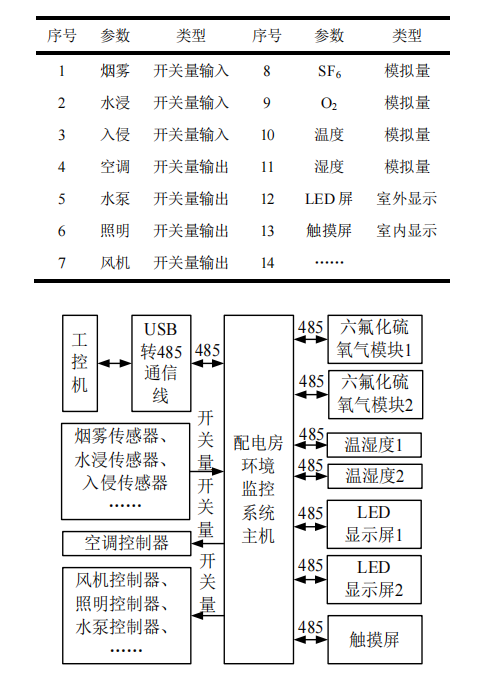

環境監控系統主機,以I/O和RS485通信等形式采集配電房各種開關量模擬量輸入,控制各種對象,同時采用標準RJ45接口設計了統一接口。應用結果表明,采用單片機進行主機設計并采用RJ45接口解決了上述

2024-01-09 16:27:13

微信同號***QQ 2168848469蘇州工控產品回收公司長期高價回收SMC氣缸,SMC電磁閥,SMC磁性開關,SMC滑臺氣缸,夾爪氣缸,導桿氣缸,SMC壓力開關,比例閥、 回收三菱PLC,三菱模塊,三菱觸摸屏,三菱伺服驅動器,三菱伺服馬達,三菱張力控制器 ,數量不限,有貨的老板聯系

2021-09-02 15:35:21

最近在學習FPGA,因為Xilinx家的芯片國內用的最多,故使用了XC6SLX16。但在安裝Xilinx ISE時發現無法導入license,網絡上尋找了下方法,實測可行,故在這分享給大家。以下

2021-05-17 08:00:00

大家好,這是一個請求而不是一個問題。Xilinx能否以適合Altium導入的方式提供VC709的設計文件?目前只有“Allegro二進制PCB設計文件(* .brd)”可供下載。但是,如果您

2019-09-06 10:43:21

串行外設接口(Serial Peripheral Interface Master) Xilinx提供***************************? Resource Summary? ****************************

Macrocells???? Product Terms??? Regi

2008-05-20 10:39:45 37

37 系列型號:1SMC5333B、1SMC5334B、1SMC5335B、1SMC5336B、1SMC5337B、1SMC5338B、1SMC5339B、1SMC5340B、1SMC

2022-07-27 10:46:17

USB接口控制器參考設計,xilinx提供VHDL代碼 usb xilinx vhdl

;? This program is free software; you can redistribute

2009-06-14 09:05:40 45

45 使用EMIF將Xilinx FPGA與TI DSP平臺接口:本應用指南使用外部存儲器接口 (EMIF) 實現了 Xilinx FPGA 到 Texas Instruments 數字信號處理器 (DSP) 平臺的幾種連接。指南目錄本手冊包含以下章節

2009-11-01 15:00:09 68

68 利用XILINX解決方案快速創建存儲器接口設計

2010-01-08 23:05:26 39

39 Xilinx® FPGA提供可簡化接口設計的IO模塊和邏輯資源。盡管如此,這些IO模塊以及額外的邏輯仍需設計人員在源RTL代碼中配置,驗證,執行,并正確連接到系統的其它部分,然后仔細

2010-04-25 10:31:15 45

45 SMC真空常用產品概述

2010-11-15 23:19:17 640

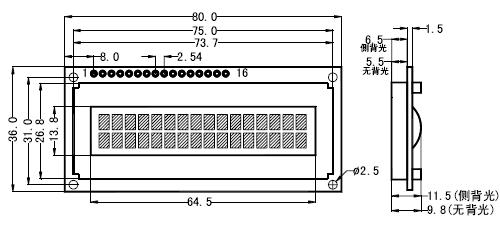

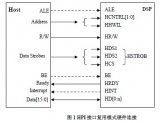

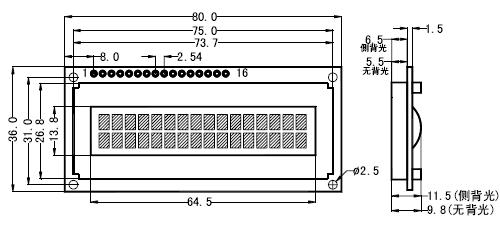

640 SMC1602液晶顯示屏的封裝尺寸及接口說明

SMC1602液晶顯示屏接口信號說明

2008-11-01 10:11:16 5043

5043

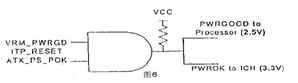

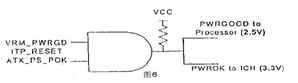

主機的電源接口

主機的電源接口一般為20PIN的接口。其中PS-ON(綠色)端和PWOK(灰色)端

2009-02-12 10:13:53 6829

6829

主機電源的主要輸出接口 電源的主要輸出接口是指電源給主板、顯卡、硬盤、光驅、軟驅等設備提供

2009-12-26 14:46:12 6212

6212 主機,什么是主機

在TCP/IP網絡環境里,主機基本上是網絡上某個IP地址的節點。比較起來,路由器是互連網絡的設備。

2010-04-06 17:29:16 1657

1657 摘要:通過分析920T核ARM 處理器的高速片上系統總線AHB時序及其靜態存儲控制器SMC接口模型,研究IBM PC/AT和IEEE PC/104

2010-07-21 15:57:32 1780

1780

通過將第三方IP集成到NI LABVIEW軟件中,您可以使用許多為XILINX現場可編程門陣列(FPGA)精調過的算法實現高性能,并且提高代碼重用度。LABVIEW FPGA模塊為導入外部IP提供了兩個方法:組件級知識產權(CLIP)節點和結合XILINX核心生成器的IP集成節點。本技

2011-03-15 13:25:58 90

90 一、配置Modelsim ISE的Xilinx的仿真庫 1、編譯仿真庫: A、先將Modelsim安裝目錄C=Modeltech_6.2b下面的modelsim.ini改成存檔格式(取消只讀模式); B、在DOS環境中,進入Xilinx的根目錄,然后依次進入

2011-03-30 10:19:07 307

307 文章給出了接口的軟硬件設計方案, 并具體敘述了軟件設計中FAT16 文件系統的使用。該方案已成功用于基于DSP 的地震電纜測試儀的研發實踐中, 這對于DSP 與USB 主機結合的相關應用具有較

2011-12-05 16:57:13 46

46 Avnet公司的DVI I/O FMC模塊提供數字視頻接口,直接連接到Xilinx Spartan-6或 Virtex-6 FMC使能的基板,數字DVI視頻源為模塊提供視頻內容,而模塊提供數字DVI和DisplayPort輸出,用來顯示FPGA驅動的

2012-10-16 10:49:52 2474

2474 FPGA 設計人員在滿足關鍵時序余量的同時力爭實現更高性能,在這種情況下,存儲器接口的設計是一個一向構成艱難而耗時的挑戰。Xilinx FPGA 提供 I/O 模塊和邏輯資源,從而使接口設計變

2013-03-14 15:16:07 71

71 Xilinx FPGA系列入門教程(二)——Xilinx FPAG開發環境的配置

2016-01-18 15:30:20 32

32 易飛揚即日宣布40G QSFP GEN2光模塊導入批量生產。與市場流行的40G QSFP通用光模塊的主要差異是:GEN2光模塊帶有多通道光功率的DDM 實時監測功能。

2016-03-11 15:48:06 1343

1343 Xilinx FPGA工程例子源碼:USB接口控制器參考設計VHDL代碼(Xilinx)

2016-06-07 14:54:57 21

21 Xilinx FPGA工程例子源碼:Xilinx DDR2存儲器接口調試代碼

2016-06-07 14:54:57 27

27 Xilinx FPGA工程例子源碼:基于XILINX的SPARTAN板的VGA接口顯示程序

2016-06-07 15:07:45 8

8 FMC-HDMI-CAM FMC? 模塊可為支持 ?Xilinx FMC? 功能的基線板提供高清視頻接口。 ?HDMI? 視頻源可向該模塊提供視頻內容。該模塊還提供一個顯示 ?FPGA? 導向型視頻

2017-02-08 20:39:11 781

781 藍牙模塊主機和從機透傳。主從藍牙模塊通信是指兩個藍牙模塊互相通信,一個為主機,一個為從機,它們相互之間通信,第一個模塊為從機模塊,第二個模塊是主機模塊?

2017-09-09 08:26:10 33

33 與CPU之間,通過USB接口進行數據傳輸。USB接口是wifi模塊芯片內部的固件程序與主機上的操作系統進行數據通信的橋梁。USB接口的作用就是數據傳輸。wifi模塊

2017-09-30 16:27:43 32

32 本項目開發了一個使用 Xilinx 公司的 SPARTAN3A-DSP FPGA 作為目標開發板,采集數字和模擬傳感器數據,并將傳感器數據采用 I2C 接口與上級無線傳感器網絡進行通信的環境監測系統

2018-03-21 16:46:00 3012

3012

本文首先介紹了什么是SMC磁性開關及SMC磁性開關技術說明和使用注意事項,其次介紹了SMC磁性開關技術指標檢測與用途,最后介紹了smc磁性開關型號及選型及選型注意事項。

2018-02-09 15:03:30 37523

37523 瑞薩電子 e2 studio 開發環境教程 – 導入篇

2018-07-23 00:16:00 2649

2649 在本演示中,Intelliprop演示了在Xilinx Zynq UltraScale + MPSoC中實現的NVMe主機加速器。

2018-11-26 06:18:00 5658

5658 了解在Xilinx工作的感受。員工提供有關我們的文化,工作環境和產生影響的機會的觀點。

2019-01-08 07:11:00 2178

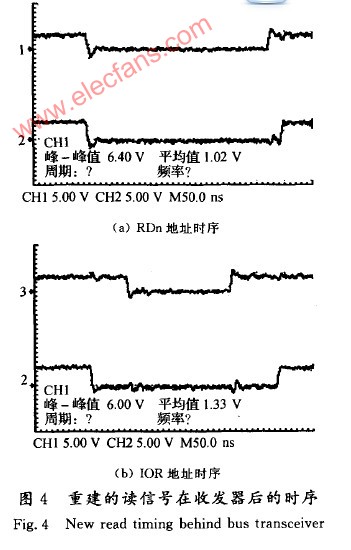

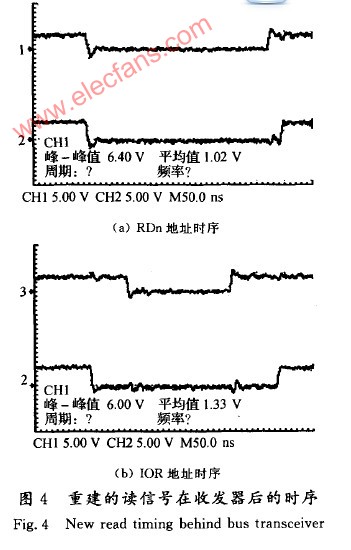

2178 數據傳輸,是WiFi模塊芯片內部的固件程序與主機上的操作系統進行數據通信的橋梁。USB接口的作用主要就是數據傳輸。在WiFi模塊接收數據時就會引發USB接口的讀數據操作。 目前WiFi模塊的通信接口方面,采用USB接口的模塊比較多,能夠滿足大多數外設的速率要求,被廣泛地應用

2020-03-27 10:09:56 2050

2050 HPI 接口是TI 為處理器之間直接互連通訊定義的一種異步接口,大多數TI DSP 芯片上都有HPI 接口。HPI 接口是從(Slave)端口,接在主機的擴展內存總線上,DSP 不能通過HPI

2019-07-01 09:14:33 6853

6853

惠而浦(Whirlpool)是全球最大的家電制造商,每年銷售額達到210億美元,旗下有9.2萬名員工和65個制造研發中心,最近在波蘭LODZ廠房導入3部MiR200自主機器人(AMR),讓員工專心處理高附加價值的事務。而同為惠而浦全球三大智能制造示范工廠之一的合肥工廠,或也即將導入該機器人。

2019-12-04 11:31:45 454

454 本文檔的主要內容詳細介紹的是SMC1602A顯示模塊的使用說明書。

2019-12-04 17:15:29 18

18 隨著USB接口的越來越普及,現在幾乎所有的接口都可以轉換成USB接口,本文主要介紹一下Xilinx FPGA的JTAG接口轉換成USB接口的方案。

2020-01-24 17:34:00 15016

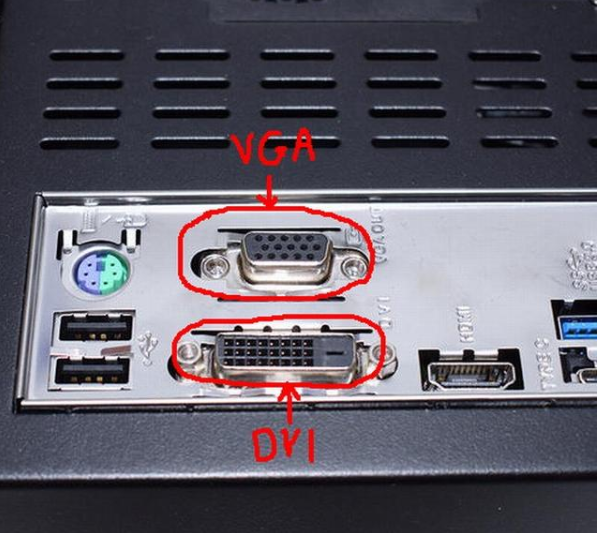

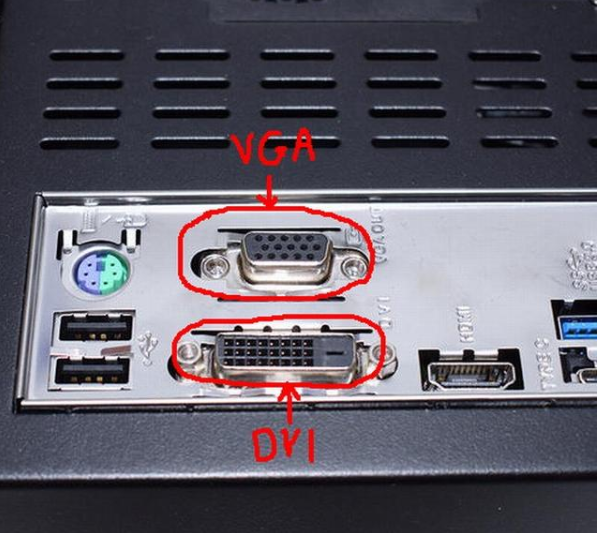

15016 大家好,我是波仔,今天來跟大家一起分享一下主機與顯示器連接的這兩種接口的區別。

2020-06-24 09:47:39 18926

18926

日常生活中我們離不開顯示器,如電視、電腦等。隨著顯示技術的發展進步,很多消費者對這類概念仍較為模糊,容易被不良商家所誤導消費。所以,消費者選購主機和顯示器時,需要考慮主機的顯卡接口是否與顯示器接口相匹配,想追求高清的顯示效果,接口類型就必須了解。

2020-07-24 17:02:49 1788

1788 分析SMC電源故障:無電源掉網,說明US1無電,或者欠電.測量抓手SMC入端的US1電壓,電壓值為23.8V,在電壓穩定時不出故障,當有設備工作不穩定時電壓會更低.

2020-08-07 16:46:59 2469

2469

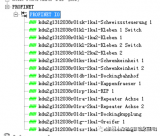

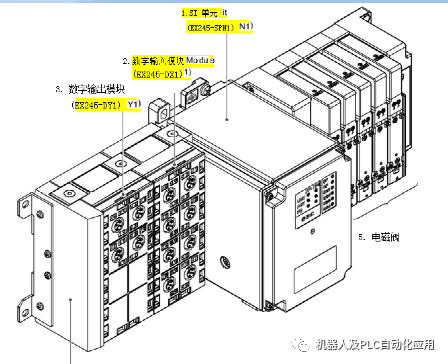

組態一個PROFINET網絡下的SMC閥導EX245模塊,SMC EX245網絡閥導分,銅纜和光纜口的模塊。

2020-09-08 11:09:29 2658

2658

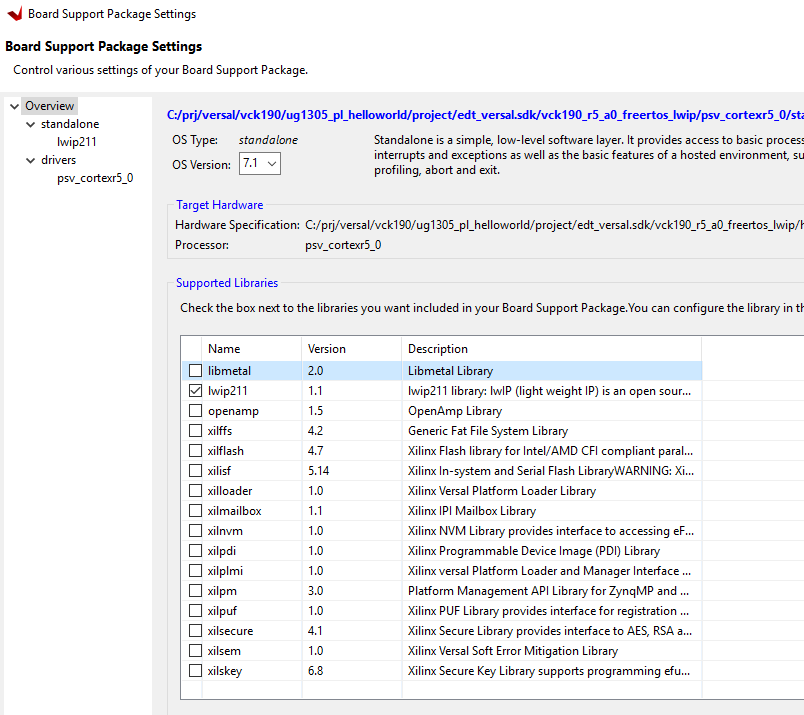

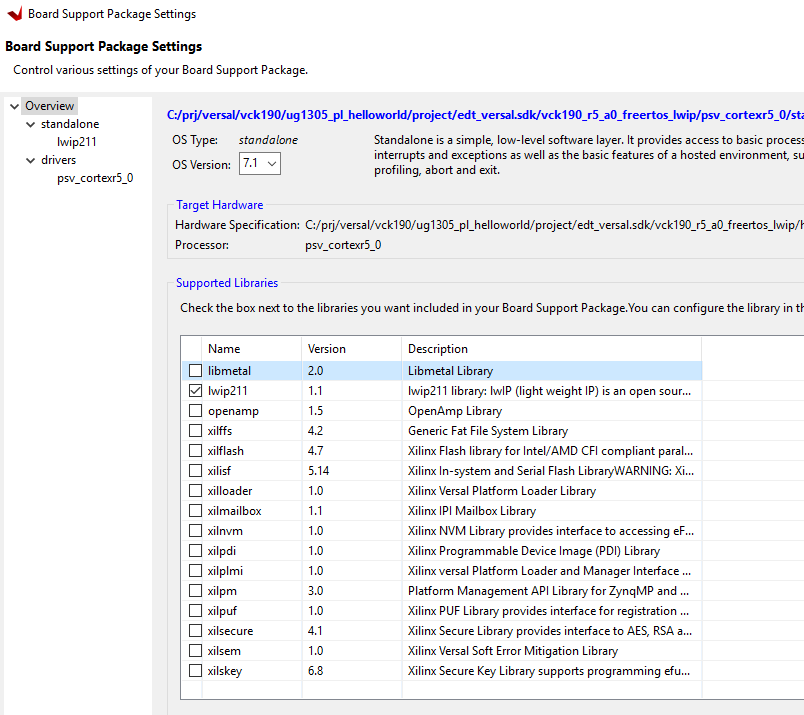

Xilinx的SoC在業界應用非常廣泛。對應的開發工具SDK也很成熟。在SDK里,每一個baremetal工程,對應一個BSP工程,它包含一些Xilinx提供的公共模塊,比如硬件的驅動

2020-10-09 12:22:48 3198

3198

? ? 組態一個PROFINET網絡下的SMC閥導EX245模塊 SMC EX245網絡閥導分,銅纜和光纜口的模塊 以組態SMC銅口模塊為例: 只設置激活US1電源監控 插槽1使用診斷模塊 插槽

2021-01-02 11:21:00 1881

1881

分析SMC電源故障:無電源掉網,說明US1無電,或者欠電.測量抓手SMC入端的US1電壓,電壓值為23.8V,在電壓穩定時不出故障,當有設備工作不穩定時電壓會更低.

2021-01-18 13:42:46 2392

2392

的SMC-SI-EX245單元使用10個閥導,首先是先導閥壓力故障,將先導閥壓力反饋短接后變成中間到末位的幾個電磁閥輪番報錯. 下面我們介紹一下SMC-SI-EX245系列模塊: SMC的SI 單元

2021-02-09 11:44:00 3465

3465

什么是 MPO接口光模塊? MPO接口光模塊指的是接口類型為MPO的光模塊,必須搭配MPO接口的跳線才能使用。MPO接口分為公頭和母頭,必須搭配使用。一般光模塊的接口類型為MPO公頭,所以使用MPO

2021-09-07 18:03:24 10933

10933 使用 from module import * 默認情況下會導入 module 里的所有變量,若你只想從模塊中導入其中幾個變量,可以在 module 中使用 __all__ 來控制想要被其他模塊導入的變量。

2022-03-14 16:33:00 842

842 組態一個PROFINET網絡下的SMC閥導EX245模塊

2022-10-10 16:27:05 1847

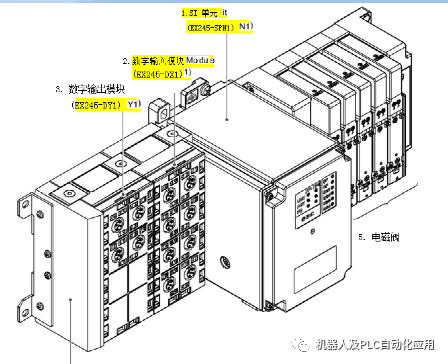

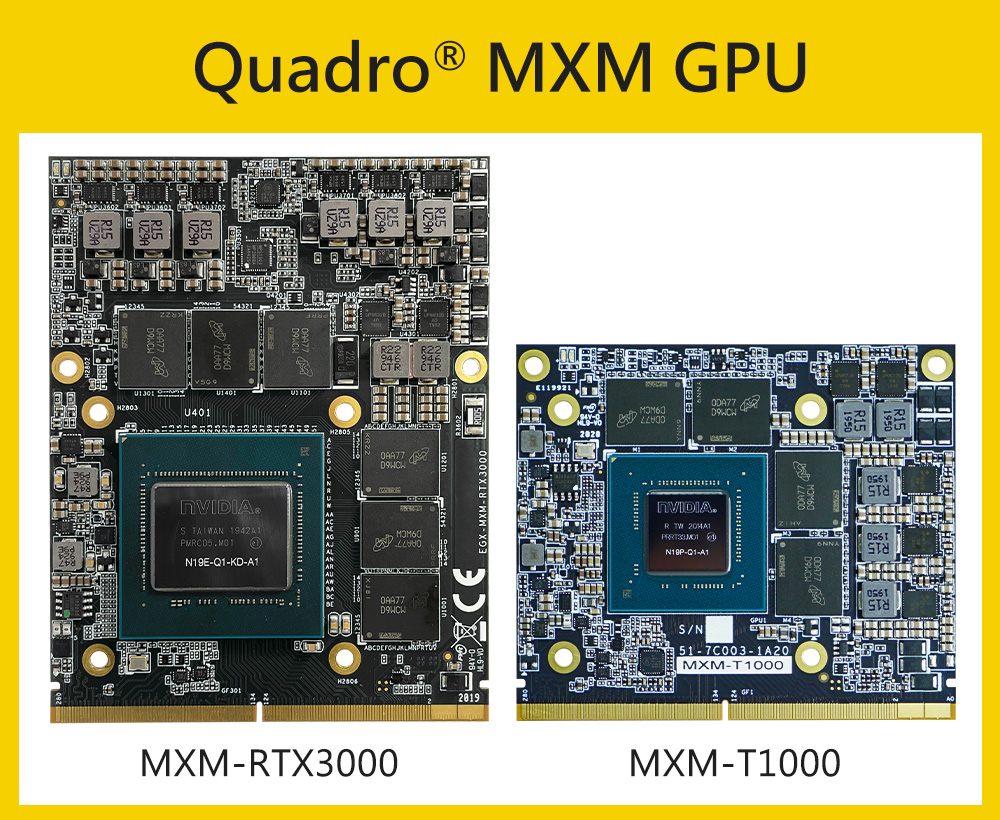

1847 中的高度影響力,無論從簡單的環境感知運用如定位、量測、識別、分撿等,到更具智能的視覺引導自動化功能,因應不同的使用環境及應用,在GPU規格要求上也有所差異,新導入的兩款Quadro? MXM GPU系列模塊,將使 GM-1000在MXM GPU 模塊的選擇性更加全面與完整。

2022-10-14 11:04:28 304

304

APM32E103VET6_SMC_SMC驅動8080并口屏時屏幕無法點亮

2022-11-09 21:04:05 2

2 APM32F407VGT6_SMC_SMC訪問外部SRAM時讀寫出錯

2022-11-09 21:04:06 0

0 python可以通過點號或字典,獲取模塊屬性。

已經導入的模塊存放在sys.modules字典,通過getattr獲取模塊屬性

2023-02-21 11:27:25 559

559 無包文件**init**.py下,python通過import module導入模塊時,先搜索程序運行主目錄。

程序運行主目錄為運行的py文件所在目錄,而不是執行python.exe時所在目錄。

模塊搜索路徑sys.path參考:python模塊基礎

2023-02-21 14:15:05 753

753 講一講Xilinx家的MIPI方案。 這里以普通7系列作為討論的對象, X家高端的KU+/MPSOC+有已經可以直接支持MIPI接口的IO了。

2023-04-19 14:04:08 2966

2966

電子發燒友網站提供《決定一個主機接口技術.pdf》資料免費下載

2023-08-18 09:48:02 0

0 import 語句的基本語法格式如下: import 模塊名 # 導入一個模塊 import 模塊1,模塊2… # 導入多個模塊 import 模塊名 as 模塊別名 # 導入模塊并使用新名

2023-09-11 17:31:50 723

723 rom…import導入 基本語法格式如下: from 模塊名 import 成員1,成員2,… 如果希望導入一個模塊中的所有成員,則可以采用如下方式: from 模塊名 import

2023-09-11 17:35:52 645

645 import () 動態導入 import 語句本質上就是調用內置函數 import (),我們可以通過它實現動態導入 實操代碼: 使用 import () 動態導入指定的模塊

2023-09-11 17:38:27 723

723 所謂的模塊 導入,是指在一個模塊中使用另一個模塊的代碼的操作,它有利于代碼的復用。 也許你看到這個標題,會說我怎么會發這么基礎的文章? 與此相反。恰恰我覺得這篇文章的內容可以算是 Python

2023-11-02 11:45:50 300

300

Python是一種強大的編程語言,它支持模塊化編程,使得開發者可以將代碼分解為可重用且獨立的模塊。模塊是一個包含函數、類和變量等定義的文件,我們可以使用import語句將這些模塊導入到我們的程序

2023-11-22 14:46:41 454

454 在Python中使用math模塊需要先導入該模塊。math模塊提供了許多數學函數和數值常量,可以在數學計算和統計分析等方面派上用場。下面將詳細介紹如何導入math模塊以及如何使用它的各種功能。 要使

2023-11-22 14:49:12 581

581 在Python中,import語句用于導入代碼所需的模塊或包。模塊是Python代碼的集合,而包是包含模塊和其他包的文件夾。在本文中,我將詳細說明如何使用import語句導入包。 導入包的方法有兩種

2023-11-22 14:59:06 294

294 監控系統主機,以I/O和RS485通信等形式采集配電房各種開關量模擬量輸入,控制各種對象,同時采用標準RJ45接口設計了統一接口。應用結果表明,采用單片機進行主機設計并采用RJ45接口解決了上述配電房環境監控系統存在的問題,具有很好的推廣價值。

2023-12-20 16:36:59 222

222

本周帶來的是一款USB外設/主機控制模塊"USBModuleV12",模塊集成全功能USB主機控制器MAX3421E,該控制器支持USB2.0規范,能夠實現對USB設備的高效控制

2024-03-05 08:29:36 73

73

電子發燒友App

電子發燒友App

評論