1、引言

隨著圖像處理、工業控制、無線通信等領域的飛速發展,對數據采集系統的速度、精度等性能要求也越來越高。這些要求都對數據采集系統的設計和實現提出了新的挑戰。目前數據采集系統的設計方案通常分為以下幾類:

1)以微處理器單一控制芯片和A/D轉換器形式為主,該設計方案簡單,在對性能要求不高的應用場合為了降低成本甚至可以采用集成A/D轉換器的微處理器。

2)采用通用計算機配置數據采集卡的方式,通常需要開發計算機端應用程序,可以完成復雜的計算,但不同的采集卡相應的驅動程序不同,如果需求改變需要更換采集卡時,相應的應用程序也需要重新開發。因此,該設計方案通用性差,實時性不高。

3)以ARM和FPGA或DSP和FPGA組合方式作為采集系統的核心,ARM處理器適合控制領域,DSP處理器適合信號處理領域,FPGA器件由于其自身特點,適合高速并行采集與處理領域,具有ARM或者DSP等處理器無法比擬的優勢。這類組合方式結合各自特點,處理能力強,應用范圍廣。

ARM和FPGA之間的數據交換采用雙口RAM芯片來實現FIFO功能。系統中ARM處理器作為系統控制核心,負責控制整個系統工作時序、并將數據通過網絡上傳到服務器中進行存儲。FPGA負責A/D轉換器的模式配置,數據傳輸。該組合方式結合ARM在控制方面和FPGA在采集方面的優勢,具有通用性強、配置靈活的特點。

2、系統設計

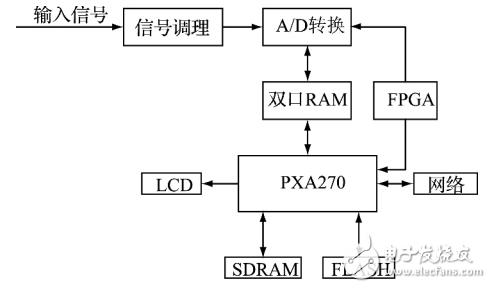

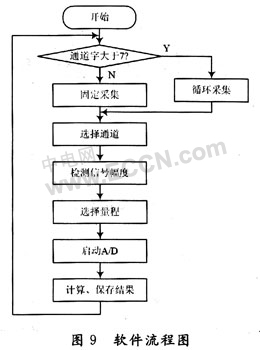

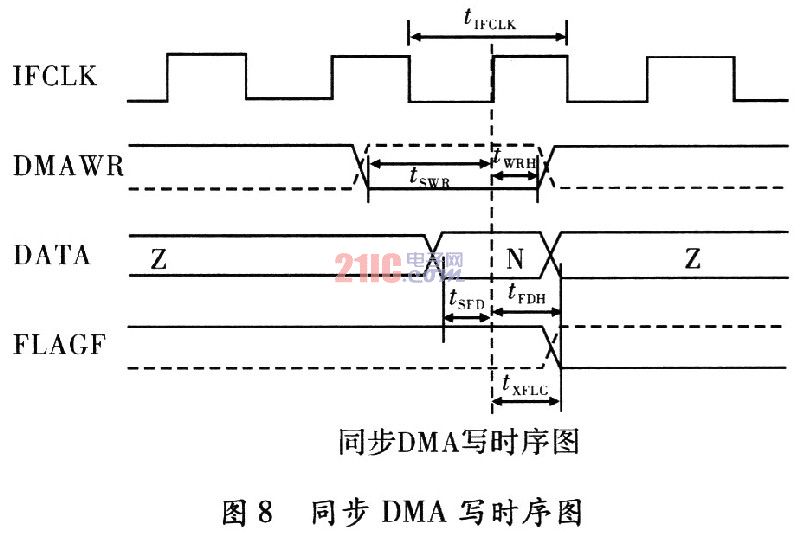

本系統硬件主要由信號調理電路、模數轉換器ADS1278、FPGA器件CyCLOnE系列EP1C6、雙口RAMIDT7205和處理器PXA270及外圍電路組成,系統結構框圖如圖1所示。輸入信號經過信號調理電路后,進入A/D轉換器進行數據轉換,將模擬信號轉換成23位尾數和一符號位的數據,FPGA配置A/D轉換器并將轉換的數據按照順序存儲到雙口RAM中,當轉換數據存儲滿后中斷ARM處理器,ARM處理器將數據從雙口RAM讀出進行運算,并通過網絡接口將采集數據傳輸到服務器。

圖1 ?系統結構

2.1、24位A/D轉換芯片ADS1278

ADS1278是德州儀器(TI)公司推出的采樣率高達128KS/S、24位8通道同步采樣Σ-ΔADC。支持多種工作模式,內部集成線性相位數字濾波器,數據輸出接口支持SPI或可選幀同步,便于與FPGA互連。可滿足國防、航天和醫療應用。

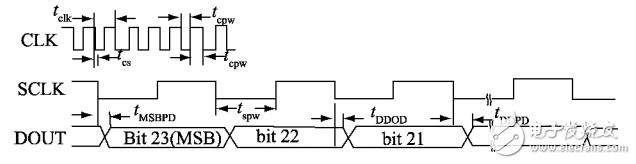

ADS1278轉換器內部集成的數字濾波器通過奈奎斯特采樣將輸入信號抽取為長度為1比特的高分辨率數字信號。8通道輸入信號分別進入獨立的8個A/D轉換器,它內部由高階斬波器、數字濾波器、調制器組成,可將輸入模擬信號經過高階濾波器后得到數字信號。圖2為ADS1278的SPI格式下,時鐘和數據時序圖。

圖2 ?SPI格式下時序

2.2、ARM與FPGA的接口設計

本系統核心采用ARM和FPGA的組合方式,在ARM和FPGA之間采用3片雙口RAMIDT7205進行24BIT數據傳輸,其中,FPGA器件控制A/D轉換,并將轉換數據按照一定順序存儲到雙口RAM中,當數據存儲完后將中斷ARM,ARM將雙口RAM中的數據進行讀取,比使用FIFO傳輸的方案降低了成本、提高了數據傳輸的吞吐量。

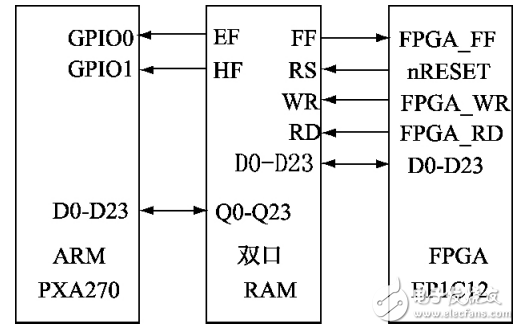

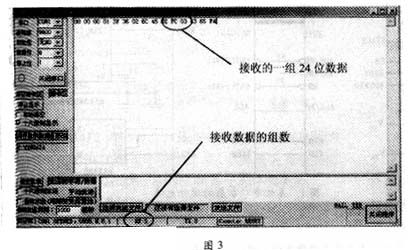

本系統中FPGA的設計作用如下:復位并配置ADS1278的工作模式,FPGA內部設置一個地址加法器控制將A/D轉換器的數據寫入雙口RAM中,當雙口RAM寫滿后,大小24KB,地址加法器復位。ARM與FPGA的接口方式有很多種,如IIC、SPI等串行接口或總線等并行接口,串行接口由于本身的局限性限制了其在大數據量、實時數據的傳輸的應用,而總線的形式更合理一些,穩定性較之更好一點。但ARM與FPGA通過地址、數據、控制總線直接連接的方式在大數據傳輸時會影響系統的效率,因此,在ARM與FPGA之間采用雙口RAM進行連接的方式,ARM與FPGA異步工作,提供了系統的效率。其接口如圖3所示。

圖3 ?ARM與FPGA的接口

FPGA的控制信號WR、RD、nRESET與雙口RAMIDT7205的復位信號RS、讀寫信號WR和RD連接,數據總線D0~D23與雙口RAM的數據總線連接,FPGA通過內部地址加法器依次將將A/D轉換器的數據串并轉換后寫入雙口RAM中。雙口RAM的EF、HF信號分別與PXA270的GPIO0和GPIO1連接,接受數據寫滿后產生的中斷。PXA270提供6個分區的靜態存儲器BAnK0~BAnK5,設計將雙口RAM的存儲空間映射到PXA270的BAnK3上。

3、驅動程序設計

為了實現ARM與FPGA通過雙口RAM的數據傳輸,需要設計嵌入式LInux下的驅動程序。當FPGA將數據寫到雙口RAM中,根據雙口RAM中數據的狀態中斷ARM處理器進行數據讀取。這一過程主要需要中斷和總線驅動程序配合。

在中斷驅動程序中,通過REquEST_IRq()函數為雙口RAM的中斷分配中斷請求(IRQ)號,當處理器檢測到這一IRQ號對應的中斷產生時,將啟動該IRQ對應的中斷服務例程[9]。IRQ號與中斷處理例程是一一對應的,在系統/PORC/InTERRuPTS文件中可以為設備選擇IRQ號。FP-GA將A/D轉換的數據寫入雙口RAM后,當數據寫滿后會中斷ARM處理器,ARM會響應中斷處理例程,讀取雙口RAM中的數據。中斷處理例程首先要清除PXA270的中斷寄存器相應的位,需要通過對狀態寄存器相應位進行寫操作,這是為了能夠繼續響應雙口RAM產生的中斷。然后是設置數據傳輸標志位,當主程序中檢測到標志位,進而調用總線驅動程序進行數據傳輸,這種工作方式可以避免中斷處理例程的冗長,提高系統傳輸效率。

由于應用程序工作在用戶空間,它無法完成對總線的操作,而驅動程序工作在內核空間,可完成對總線的操作,因此,在總線驅動程序中,必須支持應用程序對總線的操作,以完成數據的傳輸。傳統的LInux應用程序需要通過總線驅動程序完成對總線空間的訪問方法是通過2個函數完成用戶空間與內核空間之間的數據傳遞,其中內核空間向用戶空間傳輸數據使用COPy_FROM_uSER函數,用戶空間向內核空間傳輸數據使用COPy_TO_uSER函數。COPy_FROM_uSER,COPy_TO_uSER等。這種方法雖然能完成2個空間的數據傳輸,但是效率不高,最好的方法是將內核空間能訪問的物理地址直接映射到用戶空間,LInux內核提供了REMAP_PAGE_RAnGE函數,應用程序對該用戶空間的地址訪問相當于直接對物理地址的訪問。本文的總線驅動程序就是直接映射的方法,來完成快速的讀寫。

下面是驅動程序代碼段,它使用REMAP_PAGE_RAnGE()函數在驅動程序中完成MMAP系統調用中物理空間到虛擬空間的映射,REMAP_PAGE_RAnGE()函數原型如下:

InTREMAP_PAGE_RAnGE(vMA_AREA_STRuCT*vMA,un-SIGnEDLOnGFROM,unSIGnEDLOnGTO,unSIGnEDLOnGSIzE,PG-PROT_TPROT);

REMAP_PAGE_RAnGE()函數的調用需要初始化。

虛擬內存空間指針vMA、起始地址、物理地址、映射區域字節數等參數。首先計算物理地址,然后通過右移PAGE_SHIFT位,本系統使用PXA270的BAnK3的物理空間,起始地址0x0C000000,大小為4KB映射到虛擬空間。驅動程序中,還需要判斷虛擬內存大小和偏移了指定距離后物理內存的大小,如果虛擬內存過大,應該返回并提示映射超出允許的內存空間。

調用REMAP_PAGE_RAnGE()函數過程如下:REMAP_PAGE_RAnGE(vMA,vMA->vM_START,0x0C000000+vMA->vM_PGOFF<<PAGE_SHIFT,vMA->vM_EnD-vMA->vM_START,PGPROT_nOnCACHED(vMA->vM_PAGE_PROT));

應用程序中調用MMAP系統就是對MMAP()函數的參數初始化。MMAP()函數原型如下:

void*MMAP(vOID*START,SIzE_TLEnGTH,InTPROT,InTFLAGS,InTFD,OFF_TOFFSET);

首先將文件描述符FD指定的設備文件與START處開始的內存空間關聯,通常將START設為0,MMAP()函數返回實際關聯的內存地址。LEnGTH為內存映射的字節長度,PROT為內存保護類型,FLAG為映射類型,MAP_SHARED標識符表示與其他所有映射這個對象的進程共享內存區域。本設計調用MMAP()函數過程如下:

BASE=(unSIGnEDLOnG*)MMAP(0,0X100,PROT_READ|PROT_WRITE,MAP_SHARED,FD,0);

4、系統實驗結果分析

本系統中,FPGA外部晶振頻率采用32.768MHz,經過內部16分頻器后得到2.048MHz時鐘頻率作為ADS1278的工作時鐘。ADS1278完成8通道24位精度的采樣傳輸大約需24μS,采樣數據被FPGA寫入雙口RAM基本在采樣結束后同步完成。當雙口RAM數據被寫滿后,中斷ARM處理器進行數據讀取,ARM的工作頻率為520MHz,外部總線時鐘頻率為104MHz,配置PXA270外部BAnK3的MSC寄存器為0x7FF4滿足系統對雙口RAM時序讀寫的需要。

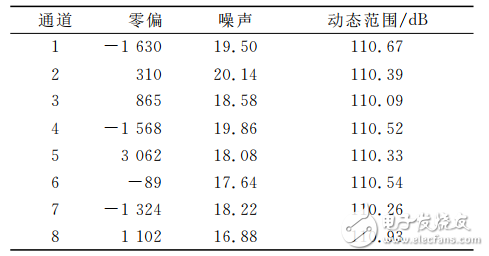

為了提高采集精度,首先需要對A/D轉換器進行零偏校準,零偏校準后,通過動態范圍計算公式20×LG(信號電壓/噪聲電壓)得到各通道實際動態范圍如表1所示。其中零偏電壓以轉換后的數字形式給出。從表1中動態范圍一列中可以看出,系統各通道實現的動態范圍都接近A/D轉換器24位采樣精度時的理想動態范圍111DB,測量結果表明本文設計的系統可充分發揮A/D轉換器高精度、大動態范圍的特性。

表1?各通道參數

系統測量加速度信號各通道顯示界面如圖4所示,從圖中可以看出,加速度信號實時、連續地顯示驗證了本文提出的采用雙口RAM作為ARM與FPGA之間的數據傳輸方式及相應的總線、中斷驅動程序的正確性和可行性。該方案也可應用于電力頻率測量等其他高精度采集領域。

圖4系統采集顯示界面

5、結論

充分利用ARM和FPGA各自的優勢,設計一種ARM和FPGA組合的高精度數據采集系統,采用雙口RAM設計了ARM與FPGA之間的數據傳輸方式,解決了使用傳統FIFO芯片成本高、容量小的問題,提高了ARM與FPGA傳輸吞吐量。編寫了LInux下設備的驅動程序,采用中斷方式及用戶空間對內核空間的直接訪問方式進行數據傳輸,大大提高了系統傳輸的效率。設計的基于雙口RAM的ARM與FPGA采集系統具有成本低、精度高、動態范圍大等特點,是高精度采集處理的一種高效可行的解決方案。

電子發燒友App

電子發燒友App

評論