?

身處市場(chǎng)領(lǐng)先地位的SoC(系統(tǒng)單芯片)設(shè)計(jì)團(tuán)隊(duì)認(rèn)為,“慣常的業(yè)務(wù)”已不復(fù)重現(xiàn)。強(qiáng)大的技術(shù)與商務(wù)力量(似乎獨(dú)立于EDA供應(yīng)商的路線圖)都在將SoC設(shè)計(jì)方法重新塑造為新的形式,并與僅僅幾年前的最佳實(shí)踐有非常大的差異。對(duì)很多架構(gòu)師、設(shè)計(jì)者和管理者來說,這種變化會(huì)很痛苦。然而,糾結(jié)于過去就意味著失敗。

這一變化有幾種促進(jìn)力量。現(xiàn)實(shí)的財(cái)務(wù)與地理狀況已迫使對(duì)第三方IP(知識(shí)產(chǎn)權(quán))的依賴性提高,并且削弱了從下游問題到RTL(寄存器傳輸級(jí))糾錯(cuò)的反饋回路。復(fù)雜性已迫使以前下游的工作進(jìn)入到設(shè)計(jì)流的早期,尤其是激進(jìn)電源管理的設(shè)計(jì)產(chǎn)生的電源與時(shí)鐘網(wǎng)絡(luò)的復(fù)雜性。另外,先進(jìn)工藝的挑戰(zhàn)也同時(shí)影響到了前端和后端的工作。

推動(dòng)力

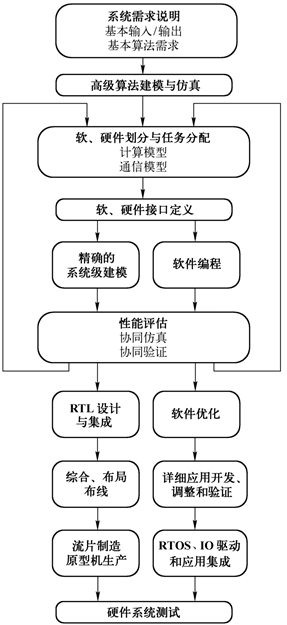

IP可能是解決方案的一部分,而不是問題的一部分。從I/O控制器到CPU的一切IP重用,可能都對(duì)設(shè)計(jì)團(tuán)隊(duì)起到了驅(qū)散和縮減作用。但I(xiàn)P的普遍使用改變了設(shè)計(jì)流的本質(zhì)。以前的流程包括:建立性能需求、將它們縮減至RTL、網(wǎng)表綜合,以及在單元中實(shí)現(xiàn)。現(xiàn)在,設(shè)計(jì)流程變成了一組特定的復(fù)雜、日趨固定且不透明功能塊的裝配與強(qiáng)制封裝的過程。當(dāng)設(shè)計(jì)者在整合或封裝中遇到問題時(shí),通常只有原始IP的開發(fā)者才能提供幫助。

雖然IP重用有助于減少設(shè)計(jì)的規(guī)模,但無助于減少復(fù)雜性的其它方面。尤其是對(duì)電源管理來說,時(shí)鐘門控是降低動(dòng)態(tài)功耗的一種強(qiáng)制性設(shè)計(jì)步驟,但它也將SoC的時(shí)鐘網(wǎng)絡(luò)搞得非常復(fù)雜,因此時(shí)鐘樹實(shí)際上成為了另外的信號(hào)網(wǎng)絡(luò),需要作提取、時(shí)序、電源與信號(hào)完整性收斂。電壓島、電源門控,以及DVFS(動(dòng)態(tài)電壓/頻率縮放)正在進(jìn)入大多數(shù)設(shè)計(jì)團(tuán)隊(duì),它們的使用很可能使電源網(wǎng)格更加復(fù)雜化。

最后,工藝本身也在促進(jìn)著變革。盡管工藝工程師與單元庫開發(fā)者都在竭盡全力,但到65nm節(jié)點(diǎn)時(shí),先進(jìn)工藝的復(fù)雜性已開始穿過定制/單元的障礙,將其呈現(xiàn)在芯片設(shè)計(jì)者面前。Virage Logic公司技術(shù)營(yíng)銷總監(jiān)Lisa Minwell認(rèn)為:“我們存儲(chǔ)編譯器的設(shè)計(jì)者已不得不去處理工藝變動(dòng)、單元驅(qū)動(dòng)強(qiáng)度不足,以及日益復(fù)雜的DFM (可制造性設(shè)計(jì))規(guī)則問題。”采用基于單元流程的芯片設(shè)計(jì)者現(xiàn)在要面臨所有這些問題。這些力量的結(jié)合,不僅使設(shè)計(jì)更為困難,而且還改變了設(shè)計(jì)所依從的方案。

艱難的開始

Open-Silicon公司剛做了一個(gè)1億門的無線網(wǎng)絡(luò)SoC。該公司的設(shè)計(jì)采用了TSMC(臺(tái)積電公司)的65 nm CMOS工藝。Open-Silicon公司工程副總裁Taher Madraswala稱:“設(shè)計(jì)的關(guān)鍵是先期的規(guī)劃。”O(jiān)pen-Silicon公司在芯片的物理設(shè)計(jì)方面與ASIC設(shè)計(jì)服務(wù)公司Brite Semiconductor公司合作,采用了來自一家無晶圓半導(dǎo)體供應(yīng)商HiSilicon公司的需求與RTL。Madraswala說,“這差不多是一個(gè)自頂向下的設(shè)計(jì)”,并指出時(shí)鐘布局對(duì)先期工作有明顯的推動(dòng)作用。

Open-Silicon的工作開始于了解設(shè)計(jì),完成風(fēng)險(xiǎn)評(píng)估。他說:“這是一個(gè)非常巨大的內(nèi)核,還有一些極長(zhǎng)的走線。因此,我們花了三天時(shí)間開會(huì)以了解時(shí)鐘結(jié)構(gòu)。”對(duì)塊的布放來說,了解各個(gè)時(shí)鐘來源、使用者以及門控結(jié)構(gòu)是必需的預(yù)備工作。如果團(tuán)隊(duì)犯了錯(cuò)誤,那時(shí)鐘的時(shí)序就幾乎沒有收斂的機(jī)會(huì)了。

Open-Silicon公司必須使用多個(gè)IP內(nèi)核實(shí)例,它們基本上確定了管腳的位置,給塊的布放帶來了另一種約束。Madraswala解釋說:“問題在于可重復(fù)性。如果你改變了內(nèi)核的定位方向,則關(guān)鍵走線的長(zhǎng)度就變了,得到的時(shí)序就不同了。”于是,該團(tuán)隊(duì)對(duì)頂層信號(hào)、時(shí)鐘和I/O作了一次預(yù)先布線,然后將這個(gè)布線作為設(shè)計(jì)分區(qū)以及其后各塊布放的基礎(chǔ)。

Redpine Signals公司主席兼首席執(zhí)行官Venkat Mattela說:“現(xiàn)在,很難在系統(tǒng)級(jí)對(duì)一個(gè)設(shè)計(jì)作劃分。”他指出工程師必須在早期作電源規(guī)劃。Redpine公司的設(shè)計(jì)中有一個(gè)用于嵌入系統(tǒng)應(yīng)用的極低功耗802.11n收發(fā)器,RTL中,模塊定義為獨(dú)立于芯片電源策略的實(shí)體。其后的模塊分區(qū)工作不僅產(chǎn)生了功能邊界,同時(shí)還有電壓島與時(shí)鐘域之間的邊界。因此,設(shè)計(jì)團(tuán)隊(duì)可以在設(shè)計(jì)的開始,將每個(gè)RTL塊中的電源意圖(Power intent)捕捉成為一個(gè)UPF(通用電源格式)文件。

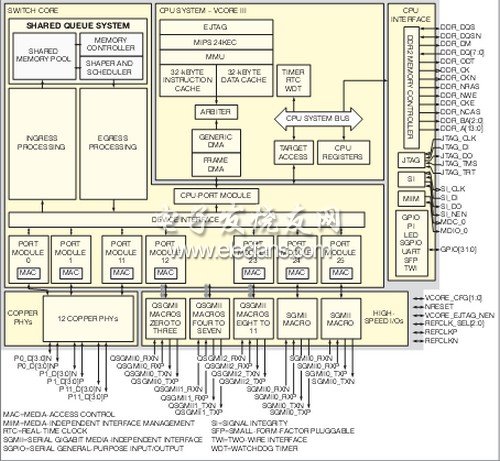

在設(shè)計(jì)早期還要注意其它一些問題。例如,Vitesse半導(dǎo)體公司最近開發(fā)了一款24端口的交換So C,集成了銅線PHY(物理層)塊(圖1)。該公司的設(shè)計(jì)總監(jiān)Mandeep Chadra稱,在評(píng)估設(shè)計(jì)者可以做到多大集成度時(shí),主要的工作都是看PHY塊的功耗,因?yàn)檫@些塊的功耗占總功耗的大部分。他說:“在整個(gè)規(guī)劃過程中,電源一直是一個(gè)主要問題,尤其是當(dāng)我們的目標(biāo)是一個(gè)打線封裝時(shí)。”封裝問題決不能事后才定,而要進(jìn)入芯片規(guī)劃的早期決策。當(dāng)不采用倒裝芯片的信號(hào)再分配層時(shí),片芯上I/O的布局就要反映出芯片的管腳布局。在這些頻率上,芯片必然影響到將使用的電路板布局。因此,Chadra補(bǔ)充說,一個(gè)交換機(jī)的物理布局會(huì)直接影響到公司的平面規(guī)劃。

?

圖1. Vitesse 7427包括一個(gè)24端口交換機(jī)和MIPS處理器,集成了PHY和MAC。

在芯片規(guī)劃的初期,會(huì)出現(xiàn)兩個(gè)問題:電源管理策略,以及頂層的信號(hào)、時(shí)鐘與電源走線問題,而EDA供應(yīng)商已對(duì)這些變化作出了回應(yīng)。現(xiàn)在,所有大公司都有電源感知流程,鼓勵(lì)設(shè)計(jì)者在早期用標(biāo)準(zhǔn)CPF(公共電源格式)或UPF文件捕捉電源意圖,然后通過綜合、布局布線和驗(yàn)證來引導(dǎo)實(shí)現(xiàn)電源管理。

供應(yīng)商正越來越多地注意到設(shè)計(jì)團(tuán)隊(duì)的一個(gè)需求,那就是早在設(shè)計(jì)的分區(qū)和平面規(guī)劃階段,就要擁有初始的布線信息。Mentor Graphics公司布局布線部經(jīng)理Pravin Madhani認(rèn)為:“在設(shè)計(jì)的早期階段,最大的意外就是堵塞。因此人們會(huì)非常早地使用自己的布局布線工具,檢查潛在的堵塞問題。”這種趨勢(shì)轉(zhuǎn)而促使布局布線工具供應(yīng)商擴(kuò)展了自己的工具,使之可以用于設(shè)計(jì)的初期階段。

意外的堵塞問題會(huì)產(chǎn)生高昂的后果。Open-Silicon的Madraswala稱:“我們一系列塊都遭遇了堵塞問題。我們必須返回去,重寫RTL來解決這些問題。”這就要對(duì)那些塊再走一遍驗(yàn)證、設(shè)置和綜合過程。而Open-Silicon則是從頭建立一個(gè)通向HiSilicon的RTL設(shè)計(jì)的快速反饋路徑,方法是在中國(guó)的HiSilicon公司派駐了一個(gè)六人設(shè)計(jì)團(tuán)隊(duì)。

第三方IP的堵塞意外可能更糟。例如,IP供應(yīng)商缺乏資源,不能按你的時(shí)間表修改RTL,或者堵塞是出現(xiàn)在一個(gè)硬IP塊的管腳處。在最差情況下,SoC團(tuán)隊(duì)可能不得不更換IP供應(yīng)商。于是,使設(shè)計(jì)分區(qū)和布局與功率策略保持一致,并且擁有一個(gè)頂級(jí)布線的早期視圖,就成為了任務(wù)關(guān)鍵的問題。

綜合與驗(yàn)證

Open-Silicon、Vitesse和Redpine的設(shè)計(jì)團(tuán)隊(duì)并不認(rèn)為綜合是一個(gè)大問題。他們更關(guān)注如何避免重復(fù)地做綜合。Madraswala說:“我們把每個(gè)RTL塊看成像是一個(gè)獨(dú)立的片芯。然后我們?cè)谝粋€(gè)足夠高的結(jié)果品質(zhì)上,關(guān)注每個(gè)塊在流程中的每個(gè)步驟。這樣的結(jié)果可能是,在時(shí)鐘插入后,我們只要做一次綜合。”O(jiān)pen-Silicon使用自己的綜合工具,自動(dòng)地插入時(shí)鐘門控。另外,Madraswala稱,在架構(gòu)級(jí)的配置用于處理芯片的電源管理。“存在著電源島,但是,由于電源管理已通過RTL成為顯式的,因此我們不需要像CPF一類的東西。”同樣,Vitesse的設(shè)計(jì)使用了大量的時(shí)鐘門控,但只有一個(gè)電源門控的塊,而Chadra報(bào)告稱普通綜合流程中沒有問題。

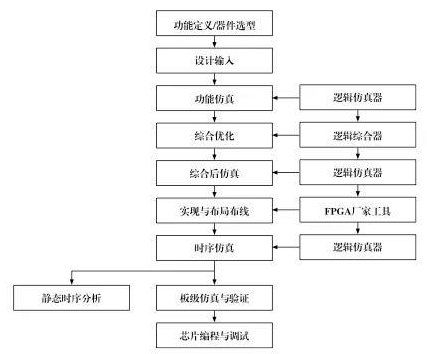

但是,Redpine采用了一種更積極的電源管理策略,使工具更加復(fù)雜。這種方案已影響到了設(shè)計(jì)流程(圖2)。Mattela稱,原則上,如果你正確地組織了RTL,并精確地捕捉了自己的電源意圖,就應(yīng)該能將RTL、UPF和電源感知庫送入綜合步驟,并且獲得一個(gè)包含全部已就位絕緣體、電平轉(zhuǎn)換器以及控制的網(wǎng)表。但他傷心地說,現(xiàn)實(shí)中,“你按了按鍵,可什么事也沒發(fā)生。”結(jié)構(gòu)上一切完美無誤,但如果用電壓感知工具做一次詳細(xì)的手工驗(yàn)證,就會(huì)發(fā)現(xiàn)完全不同的情況。

?

圖2. Redpine公司的方法包括對(duì)電源意圖的早期捕獲,以及對(duì)實(shí)現(xiàn)的后期檢查。

驗(yàn)證似乎采用了不同于綜合的新次序。隨著復(fù)雜性的增加,功能驗(yàn)證開始得更早,在一個(gè)更抽象的層級(jí)。Vitesse的Chadra稱:“我們采用一種基于覆蓋的OVM(開放驗(yàn)證方法)方案”。在24端口交換核心與MIPS CPU核心的性能模型中,設(shè)計(jì)早期啟動(dòng)了該過程,以了解芯片在有流量情況下的動(dòng)態(tài)性能。然后繼續(xù)對(duì)更多細(xì)節(jié)作驗(yàn)證,直到時(shí)鐘門控電路和絕緣體就位,測(cè)試平臺(tái)驅(qū)動(dòng)門級(jí)模型。Chadra說:“根據(jù)我們的需求文檔,我們的驗(yàn)證計(jì)劃中有特定的目標(biāo)。我們會(huì)隨著代碼覆蓋的程度而增加這些目標(biāo),指導(dǎo)驗(yàn)證工作。”

Redpine的Mattela稱,該公司的DVFS設(shè)計(jì)需要特別小心。部分問題源于邏輯仿真器,因?yàn)樗⒉荒苷f明,信號(hào)電平的一個(gè)失配是否會(huì)對(duì)電壓島之間的一根路徑造成毀滅性破壞。于是,Redpine的驗(yàn)證工程師求助于手工技術(shù),如強(qiáng)制某節(jié)點(diǎn)為三態(tài),看下游會(huì)發(fā)生什么。Mattela警告說,一部分問題是你永遠(yuǎn)不知道正在使用的模型的來源。他表示:“不要信任處于多電壓狀況下的那些模型。你不知道它們的編寫者是電子工程師還是軟件人員,后者認(rèn)為一就是一,零就是零。”

后端流程

現(xiàn)在,你需要考慮物理設(shè)計(jì)階段了:布局、布線和設(shè)計(jì)收斂。在這個(gè)階段,IP重用的影響以及設(shè)計(jì)復(fù)雜性都開始減弱,但無論如何也不會(huì)消失。而先進(jìn)工藝的挑戰(zhàn)為每個(gè)步驟都投下了更強(qiáng)的陰影。首先是好消息:設(shè)計(jì)經(jīng)理似乎認(rèn)為工具已經(jīng)接管了很多不久前還要手工完成的新任務(wù),實(shí)現(xiàn)了自動(dòng)化。Madraswala稱Open-Silicon可以利用IC Compiler感知DFM的優(yōu)點(diǎn),幫助準(zhǔn)備那些工藝強(qiáng)制要求的復(fù)雜設(shè)計(jì)規(guī)則。Mattela稱:“幾年前,一個(gè)電源管理設(shè)計(jì)在出帶前的一切工作都要手工完成。現(xiàn)在,我們已經(jīng)有了很大改進(jìn),尤其是在布線后的驗(yàn)證方面。”

然而,變化的力量仍會(huì)帶來問題。一個(gè)問題很簡(jiǎn)單:新任務(wù)促生新工具,而新工具通常是有問題的。Chadra稱:“比方說,有些point工具就不成熟。”工具的能力是一個(gè)更普遍的問題。他解釋說:“我們必須對(duì)設(shè)計(jì)作分區(qū),用工具運(yùn)行每個(gè)部分。所幸,大多數(shù)芯片都可劃分為非常自然的分段。最大的挑戰(zhàn)是讓交換通過布局布線。”

Madraswala也提到了布局布線能力。他說:“當(dāng)在IC Compiler中打開DFM感知能力時(shí),設(shè)計(jì)規(guī)模就受到了很大限制。我們被限制在大約40萬個(gè)可放置實(shí)例,”這是要通過小針眼驅(qū)動(dòng)一個(gè)1億門設(shè)計(jì)。

能力并非布局布線工具的唯一問題。現(xiàn)代布線器都能感知時(shí)序,即它們不僅嘗試為每根線尋找最可能的路徑,還能讀取設(shè)計(jì)的時(shí)序約束,嘗試使所有網(wǎng)表的布放都滿足時(shí)序要求。這個(gè)過程要求工具能夠評(píng)估一個(gè)建議走線的延遲,也就是評(píng)估走線的電容。因此,現(xiàn)代布線工具要么調(diào)用簽核提取工具,但這可能慢到無法使用,要么擁有內(nèi)置“快速而粗略”的提取評(píng)估器。不幸的是,即使在65 nm工藝節(jié)點(diǎn)上,對(duì)于那些不知道快速近似法的情況,寄生提取都是一項(xiàng)復(fù)雜的工作。Madraswala說:“IC Compiler與現(xiàn)實(shí)之間有差異。”

Chadra的情況也好不了多少。他說:“布線器的電容評(píng)估并不十分精確,”但未聲明指的是哪款布局布線工具。“我們的工具拐了不少大彎,不得不返回,重新布線。”

時(shí)序估計(jì)問題也使EDA供應(yīng)商進(jìn)入困境。如果布線器的快速電容評(píng)估不良,則物理系統(tǒng)設(shè)計(jì)者就會(huì)遇到提取、時(shí)序和重新布線等循環(huán)工作。如果布線器調(diào)用簽核提取與時(shí)序工具,則運(yùn)行時(shí)間和能力都是問題,因?yàn)檫@些工具必須應(yīng)付所有精細(xì)尺度的效應(yīng),情況會(huì)變得更加復(fù)雜。

在這些芯片設(shè)計(jì)完成后,Cadence和Synopsys都宣布了第三種可能的方案:將初期布局與時(shí)序移入綜合工具,甚至是在設(shè)計(jì)流程的更早期。這樣,評(píng)估并不會(huì)改善,但工具設(shè)計(jì)者顯然是不希望綜合工具再去創(chuàng)建那些布線器會(huì)作出錯(cuò)誤評(píng)估和錯(cuò)誤布線的網(wǎng)表。

在布線器與設(shè)計(jì)規(guī)則中也存在著類似的問題。如果布線器在工作時(shí)沒有遵循設(shè)計(jì)規(guī)則,則最終文件中就會(huì)出現(xiàn)很多違反規(guī)則情況。因此,布線器會(huì)從LEF(布局交換格式)文件中提取出設(shè)計(jì)規(guī)則,并在布線時(shí)檢查走線。這一過程對(duì)65nm節(jié)點(diǎn)的數(shù)字電路有滿意的工作效果。不過,Mentor Graphics公司的Madhani警告說,LEF不能表述先進(jìn)工藝中的某些規(guī)則,如收縮(pinch)規(guī)則。于是Mentor現(xiàn)在讓自己的Olympus布線器動(dòng)態(tài)地調(diào)用Calibre用于DRC的簽核工具。同樣,這種方案也帶來了性能成本,但慢點(diǎn)總好于出錯(cuò)。

還有意外情況,在經(jīng)過了所有前端工作后,電源域和第三方IP也會(huì)給后端設(shè)計(jì)帶來一些問題。ASIC供應(yīng)商Global Unichip公司營(yíng)銷總監(jiān)Keh-Ching Huang說:“多電源域會(huì)導(dǎo)致一種復(fù)雜的收斂。我們不得不使用大量的手工過程和腳本。”Huang稱甚至IP的選擇也會(huì)影響收斂流。“例如,如果某個(gè)客戶使用了一個(gè)低速DDR接口,則IP塊一般為軟形式,我們必須對(duì)其作綜合。塊內(nèi)將有時(shí)序收斂問題。但如果客戶獲得的是一個(gè)高速DDR接口許可,則它的形式是硬IP,這樣整個(gè)收斂過程就完全不同了。如果有問題,一般都是在封裝內(nèi)。”總之,如果一個(gè)設(shè)計(jì)包含主要來自外部的IP,則其對(duì)設(shè)計(jì)收斂的影響仍是一個(gè)有待探討的問題。

最后一點(diǎn)是新環(huán)境對(duì)模擬設(shè)計(jì)的影響。Vitesse為此項(xiàng)目重新設(shè)計(jì)了自己的銅PHY,修改了以前的設(shè)計(jì)以降低功耗。在過程中,模擬設(shè)計(jì)者遇到了一系列布局驅(qū)動(dòng)的效應(yīng),它們?cè)?5 nm工藝中是新出現(xiàn)的。Chadra稱:“我們了解到,阱鄰近與耗盡布放都影響著器件的性能。器件模型對(duì)這些效應(yīng)的建立工作還算不錯(cuò),但我們?nèi)匀灰鲋貜?fù)的布局提取,才能讓電路像我們需要的那樣工作。”

那么,整體上如何呢?顯然,今天的SoC設(shè)計(jì)需要更多的前期規(guī)劃,尤其要處理長(zhǎng)走線、時(shí)鐘和電源管理策略。預(yù)先的驗(yàn)證規(guī)劃也很重要。設(shè)計(jì)團(tuán)隊(duì)?wèi)?yīng)懂得,很多東西都進(jìn)入了綜合工具。這個(gè)步驟不再是標(biāo)準(zhǔn)單元Verilog語句的一個(gè)簡(jiǎn)單替代。因此,設(shè)計(jì)團(tuán)隊(duì)?wèi)?yīng)做好計(jì)劃,盡量減少綜合工具的重復(fù),尤其是當(dāng)那些難處理的結(jié)構(gòu)已到位時(shí),如門控的時(shí)鐘樹和測(cè)試掃描鏈。同樣,設(shè)計(jì)團(tuán)隊(duì)?wèi)?yīng)知道,過分的電源管理會(huì)使驗(yàn)證大大復(fù)雜化,這種考慮可能表明,選擇一種更漸進(jìn)的電源管理策略優(yōu)于一種復(fù)雜的策略。

最后,物理設(shè)計(jì)與收斂正在變得更困難。選擇前端工具或開發(fā)腳本,防止早期出現(xiàn)堵塞問題。對(duì)布線與簽核工具之間的迭代作出規(guī)劃,因?yàn)樗鼈兛赡芑ゲ徽J(rèn)同。對(duì)基礎(chǔ)結(jié)構(gòu),流程可能與以往相同。但重點(diǎn)正在轉(zhuǎn)移。Madraswala說:“本設(shè)計(jì)中大約60%的步驟都與過去一樣。約30%或40%是針對(duì)65 nm的,但正是這些步驟是大部分問題的根源。”

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論