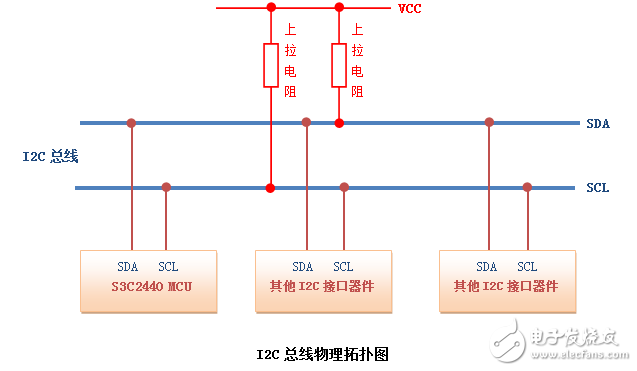

I2C總線在物理連接上非常簡單,分別由SDA(串行數據線)和SCL(串行時鐘線)及上拉電阻組成。通信原理是通過對SCL和SDA線高低電平時序的控制,來產生I2C總線協議所需要的信號進行數據的傳遞。在總線空閑狀態時,這兩根線一般被上面所接的上拉電阻拉高,保持著高電平。

一、 技術性能:

工作速率有100K和400K兩種;

支持多機通訊;

支持多主控模塊,但同一時刻只允許有一個主控;

由數據線SDA和時鐘SCL構成的串行總線;

每個電路和模塊都有唯一的地址;

每個器件可以使用獨立電源

二、 基本工作原理:

以啟動信號START來掌管總線,以停止信號STOP來釋放總線;

每次通訊以START開始,以STOP結束;

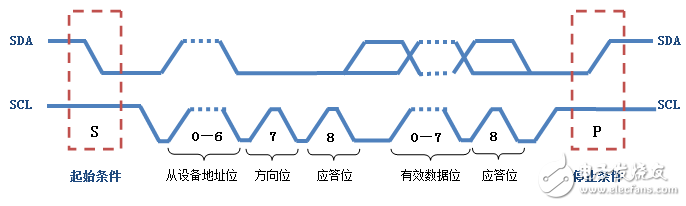

啟動信號START后緊接著發送一個地址字節,其中7位為被控器件的地址碼,一位為讀/寫控制位R/W,R. /W位為0表示由主控向被控器件寫數據,R/W為1表示由主控向被控器件讀數據;

當被控器件檢測到收到的地址與自己的地址相同時,在第9個時鐘期間反饋應答信號;

每個數據字節在傳送時都是高位(MSB)在前;

寫通訊過程:

1. 主控在檢測到總線空閑的狀況下,首先發送一個START信號掌管總線;

2. 發送一個地址字節(包括7位地址碼和一位R/W);

3. 當被控器件檢測到主控發送的地址與自己的地址相同時發送一個應答信號(ACK);

4. 主控收到ACK后開始發送第一個數據字節;

5. 被控器收到數據字節后發送一個ACK表示繼續傳送數據,發送NACK表示傳送數據結束;

6. 主控發送完全部數據后,發送一個停止位STOP,結束整個通訊并且釋放總線;

讀通訊過程:

1. 主控在檢測到總線空閑的狀況下,首先發送一個START信號掌管總線;

2. 發送一個地址字節(包括7位地址碼和一位R/W);

3. 當被控器件檢測到主控發送的地址與自己的地址相同時發送一個應答信號(ACK);

4. 主控收到ACK后釋放數據總線,開始接收第一個數據字節;

5. 主控收到數據后發送ACK表示繼續傳送數據,發送NACK表示傳送數據結束;

6. 主控發送完全部數據后,發送一個停止位STOP,結束整個通訊并且釋放總線;

? ?I2C總線特征

I2C總線上的每一個設備都可以作為主設備或者從設備,而且每一個設備都會對應一個唯一的地址(可以從I2C器件的數據手冊得知),主從設備之間就通過這個地址來確定與哪個器件進行通信,在通常的應用中,我們把CPU帶I2C總線接口的模塊作為主設備,把掛接在總線上的其他設備都作為從設備。

I2C總線上可掛接的設備數量受總線的最大電容400pF 限制,如果所掛接的是相同型號的器件,則還受器件地址位的限制。

I2C總線數據傳輸速率在標準模式下可達100kbit/s,快速模式下可達400kbit/s,高速模式下可達3.4Mbit/s。一般通過I2C總線接口可編程時鐘來實現傳輸速率的調整,同時也跟所接的上拉電阻的阻值有關。

I2C總線上的主設備與從設備之間以字節(8位)為單位進行雙向的數據傳輸。

I2C總線協議

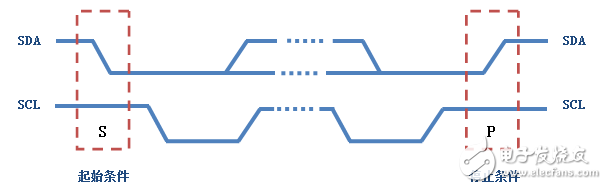

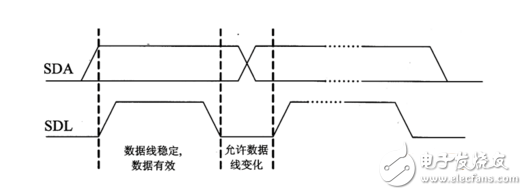

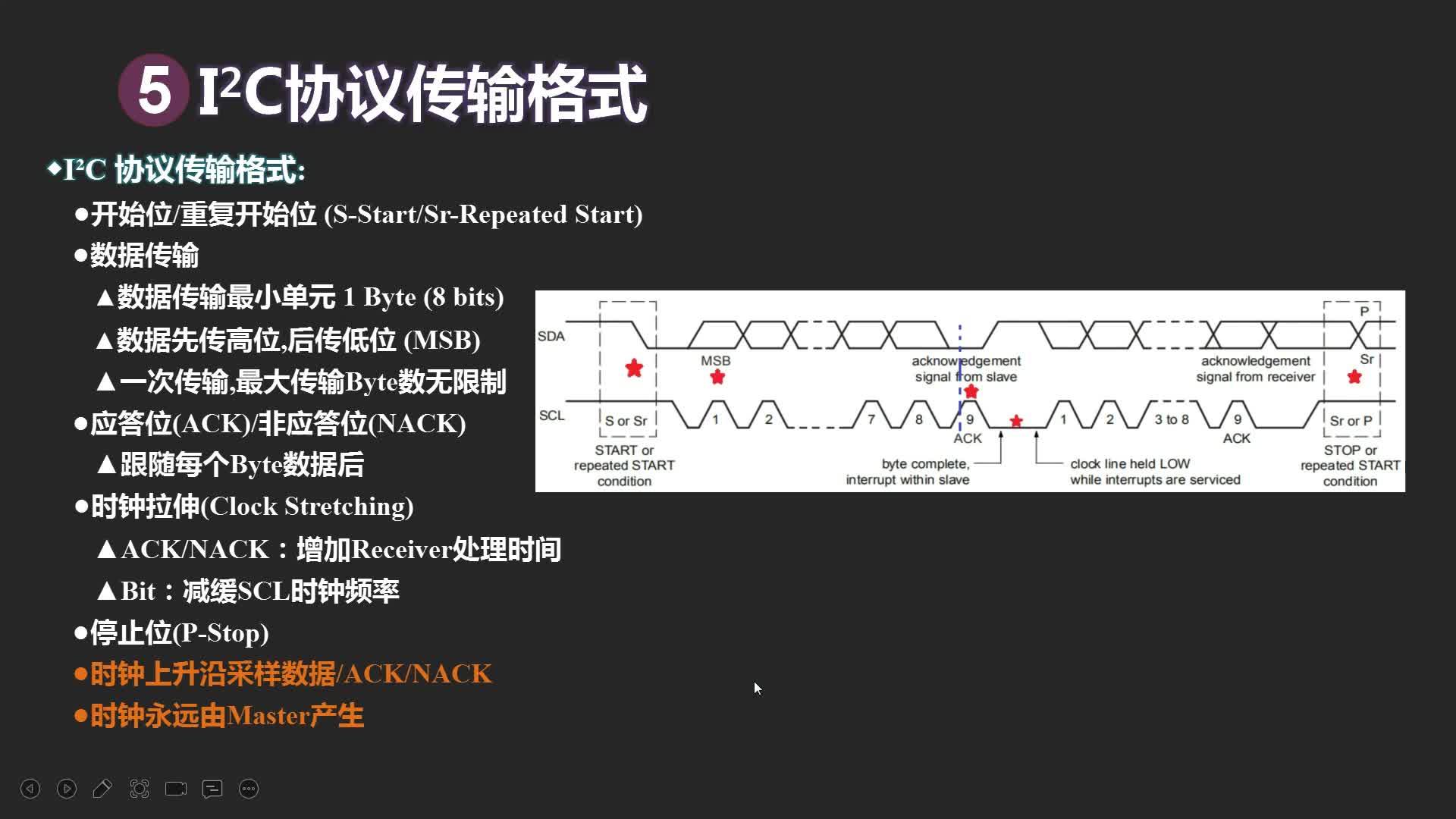

I2C協議規定,總線上數據的傳輸必須以一個起始信號作為開始條件,以一個結束信號作為傳輸的停止條件。起始和結束信號總是由主設備產生。總線在空閑狀態時,SCL和SDA都保持著高電平,當SCL為高電平而SDA由高到低的跳變,表示產生一個起始條件;當SCL為高而SDA由低到高的跳變,表示產生一個停止條件。在起始條件產生后,總線處于忙狀態,由本次數據傳輸的主從設備獨占,其他I2C器件無法訪問總線;而在停止條件產生后,本次數據傳輸的主從設備將釋放總線,總線再次處于空閑狀態。如圖所示:

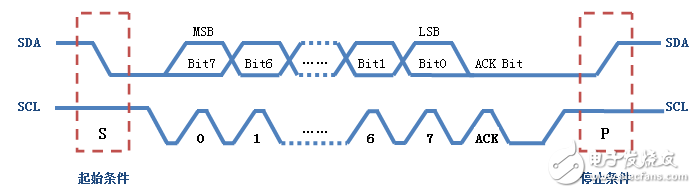

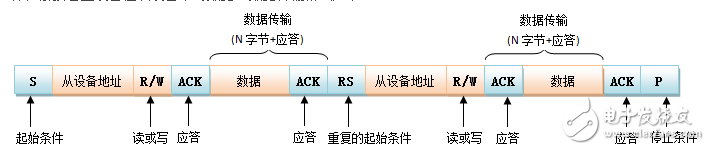

在了解起始條件和停止條件后,我們再來看看在這個過程中數據的傳輸是如何進行的。前面我們已經提到過,數據傳輸以字節為單位。主設備在SCL線上產生每個時鐘脈沖的過程中將在SDA線上傳輸一個數據位,當一個字節按數據位從高位到低位的順序傳輸完后,緊接著從設備將拉低SDA線,回傳給主設備一個應答位,此時才認為一個字節真正的被傳輸完成。當然,并不是所有的字節傳輸都必須有一個應答位,比如:當從設備不能再接收主設備發送的數據時,從設備將回傳一個否定應答位。數據傳輸的過程如圖所示:

在前面我們還提到過,I2C總線上的每一個設備都對應一個唯一的地址,主從設備之間的數據傳輸是建立在地址的基礎上,也就是說,主設備在傳輸有效數據之前要先指定從設備的地址,地址指定的過程和上面數據傳輸的過程一樣,只不過大多數從設備的地址是7位的,然后協議規定再給地址添加一個最低位用來表示接下來數據傳輸的方向,0表示主設備向從設備寫數據,1表示主設備向從設備讀數據。如圖所示:

I2C總線操作

對I2C總線的操作實際就是主從設備之間的讀寫操作。大致可分為以下三種操作情況:

第一,主設備往從設備中寫數據。數據傳輸格式如下:

第二,主設備從從設備中讀數據。數據傳輸格式如下:

第三,主設備往從設備中寫數據,然后重啟起始條件,緊接著從從設備中讀取數據;或者是主設備從從設備中讀數據,然后重啟起始條件,緊接著主設備往從設備中寫數據。數據傳輸格式如下:

第三種操作在單個主設備系統中,重復的開啟起始條件機制要比用STOP終止傳輸后又再次開啟總線更有效率。

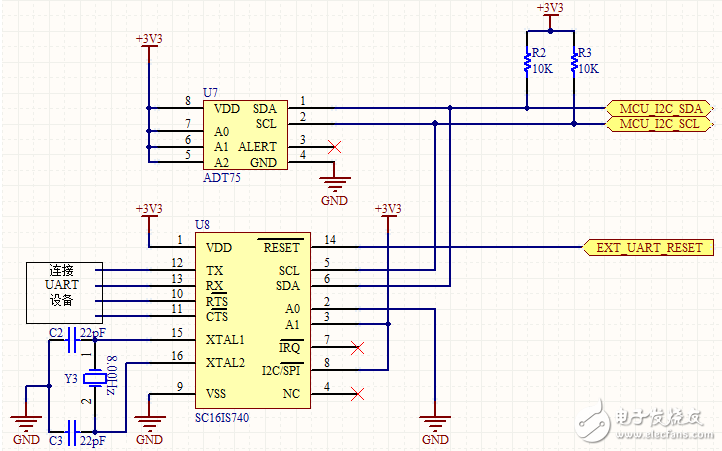

1.2.1 I2C總線硬件接口電路示例一

這個電路是基于LPC2368 ARM7芯片進行設計的,使用其內部的I2C接口作為主設備,使用ADT75和SC16IS740作為兩個從設備的I2C總線應用。

ADT75是一個帶I2C接口的溫度傳感器器件,數據手冊上對其地址的描述如下:

由此,其地址跟A0、A1、A2引腳的接法有關,我們這里的實例是將A0、A1、A2全部接到高電平上,因此其地址是:1001111(即0x4F),又因根據協議再給地址添加一個最低位(方向位,默認給寫方向),因此最后這個溫度傳感器作為從設備的地址是:10011110(即0x9E)。

SC16IS740是一個具有I2C或者SPI接口的擴展UART的器件(通過第8腳來決定使用I2C還是SPI接口,我們這里要求使用I2C接口,因此將第8腳接到高電平)。根據數據手冊,我們同樣的可以知道地址跟A0、A1的接法有關,我們這里的A0接高電平,A1接低電平。因此這個器件作為從設備的地址是:10010010(即0x92)。

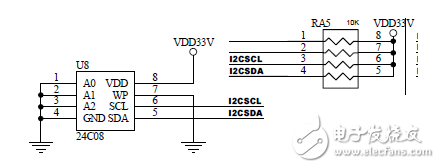

1.2.2 I2C總線硬件接口電路示例二

這個電路是Mini2440開發板上I2C總線接口的應用。我們可以看到,SDA和SCL線上接了一個10K的上拉排阻。AT24C08是一個容量為8Kbit的EEPROM存儲器件(注意是8Kbit,也就是1KB) ,根據數據手冊中器件地址部分的描述,AT24C08的地址是:1010+A2A1A0+方向位,其中1010是EEPROM的類型識別符;僅僅使用A2來確定總線訪問本器件的從設備地址,這里接的低電平,所以為0;A1和A0是器件內部頁地址,在對器件擦除或者編程時使用,雖然這里也接的低電平,但器件內部并不使用引腳的輸入值,也就是說A1和A0的值是由軟件進行設定的。

1.3 脫離操作系統的I2C總線驅動示例(以電路示例一為例)

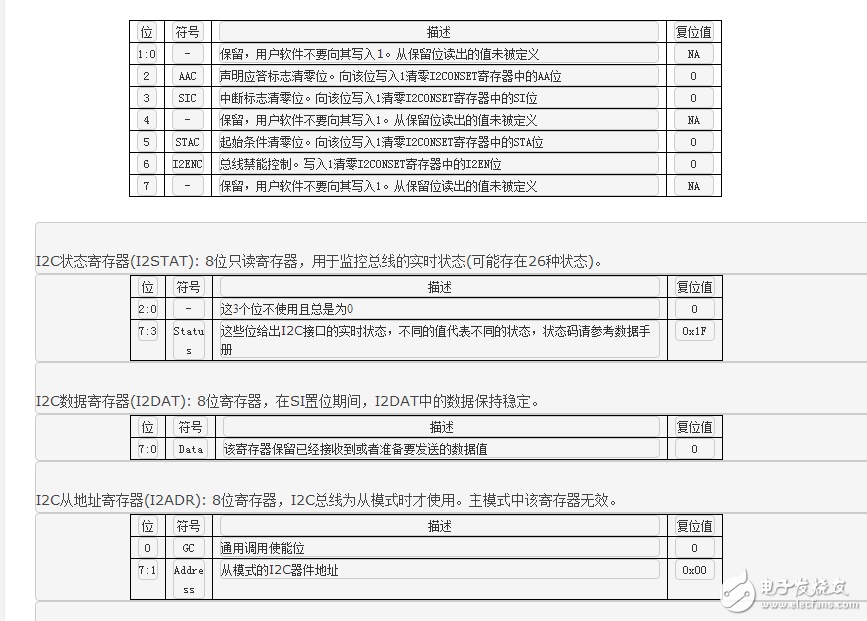

1.3.1 LPC2368中I2C接口寄存器描述

LPC2368中有三個I2C總線接口,分別表示為I2C0、I2C1和I2C2,每個I2C接口都包含7個寄存器。它們分別是:

I2C控制置位寄存器(I2CONSET): 8位寄存器,各位不同的設置是對I2C總線不同的控制。

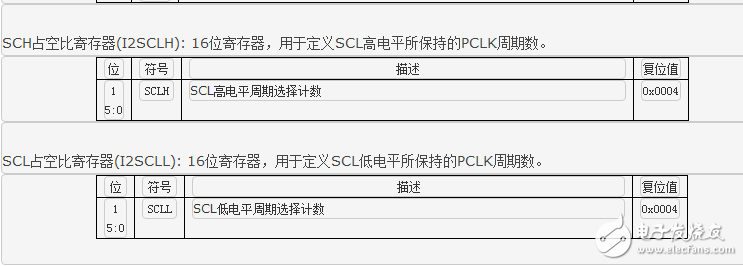

在前面的I2C總線特征中我們提到過,I2C總線的速率通過可編程時鐘來調整,即必須通過軟件對I2SCLH和I2SCLL寄存器進行設置來選擇合適的數據頻率和占空比。 頻率由下面的公式得出(fPCLK是PCLK的頻率)。

LPC2368中I2C總線操作

在1.1.4中我們已經講過了對I2C總線的操作,但那只是從協議和時序上的描述,那我們如何從軟件上去體現出來呢?接下來我們就討論這個問題。

對I2C總線上主從設備的讀寫可使用兩種方法,一是使用輪詢的方式,二是使用中斷的方式。輪詢方式即是在一個循環中判斷I2C狀態寄存器當前的狀態值來確定總線當前所處的狀態,然后根據這個狀態來進行下一步的操作。中斷方式即是使能I2C中斷,注冊I2C中斷服務程序,在服務程序中讀取I2C狀態寄存器的當前狀態值,再根據狀態值來確定下一步的操作。

不管使用哪種方法,看來I2C狀態寄存器的值是至關重要的。這些狀態值代表什么意思呢?下面我們描述一些常用的狀態值(詳細的狀態值含義請參考數據手冊)。

0x08: 表明主設備向總線已發出了一個起始條件;

0x10: 表明主設備向總線已發出了一個重復的起始條件;

0x18: 表明主設備向總線已發送了一個從設備地址(寫方向)并且接收到從設備的應答;

0x20: 表明主設備向總線已發送了一個從設備地址(寫方向)并且接收到從設備的非應答;

0x28: 表明主設備向總線已發送了一個數據字節并且接收到從設備的應答;

0x30: 表明主設備向總線已發送了一個數據字節并且接收到從設備的非應答;

0x40: 表明主設備向總線已發送了一個從設備地址(讀方向)并且接收到從設備的應答;

0x48: 表明主設備向總線已發送了一個從設備地址(讀方向)并且接收到從設備的非應答;

0x50: 表明主設備從總線上已接收一個數據字節并且返回了應答;

0x58: 表明主設備從總線上已接收一個數據字節并且返回了非應答;

四、 總線信號時序分析

1. 總線空閑狀態

SDA和SCL兩條信號線都處于高電平,即總線上所有的器件都釋放總線,兩條信號線各自的上拉電阻把電平拉高;

2. 啟動信號START

時鐘信號SCL保持高電平,數據信號SDA的電平被拉低(即負跳變)。啟動信號必須是跳變信號,而且在建立該信號前必修保證總線處于空閑狀態;

3. 停止信號STOP

時鐘信號SCL保持高電平,數據線被釋放,使得SDA返回高電平(即正跳變),停止信號也必須是跳變信號。

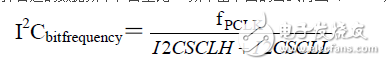

4. 數據傳送

SCL線呈現高電平期間,SDA線上的電平必須保持穩定,低電平表示0(此時的線電壓為地電壓),高電平表示1(此時的電壓由元器件的VDD決定)。只有在SCL線為低電平期間,SDA上的電平允許變化。

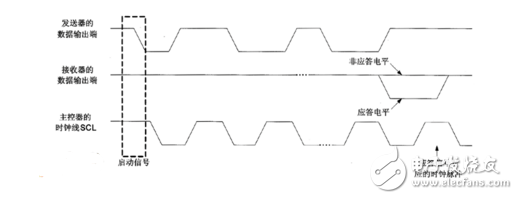

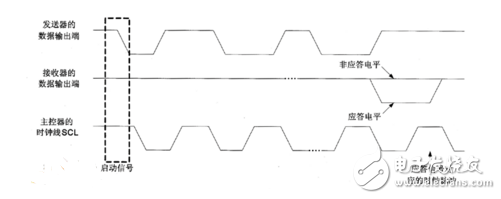

5. 應答信號ACK

I2C總線的數據都是以字節(8位)的方式傳送的,發送器件每發送一個字節之后,在時鐘的第9個脈沖期間釋放數據總線,由接收器發送一個ACK(把數據總線的電平拉低)來表示數據成功接收。

6. 無應答信號NACK

在時鐘的第9個脈沖期間發送器釋放數據總線,接收器不拉低數據總線表示一個NACK,NACK有兩種用途:

a. 一般表示接收器未成功接收數據字節;

b. 當接收器是主控器時,它收到最后一個字節后,應發送一個NACK信號,以通知被控發送器結束數據發送,并釋放總線,以便主控接收器發送一個停止信號STOP。

五、 尋址約定

地址的分配方法有兩種:

1. 含CPU的智能器件,地址由軟件初始化時定義,但不能與其它的器件有沖突;

2. 不含CPU的非智能器件,由廠家在器件內部固化,不可改變。

高7位為地址碼,其分為兩部分:

1. 高4位屬于固定地址不可改變,由廠家固化的統一地址;

2. 低三位為引腳設定地址,可以由外部引腳來設定(并非所有器件都可以設定);

主控器向被控器發送的信息種類有:啟動信號、停止信號、7位地址碼、讀/寫控制位、10位地址碼、數據字節、重啟動信號、應答信號、時鐘脈沖。

被控器向主控器發送的信息種類有:應答信號、數據字節、時鐘低電平。

下面對I2C總線通信過程中出現的幾種信號狀態和時序進行分析。

①總線空閑狀態。

I2C總線總線的SDA和SCL兩條信號線同時處于高電平時,規定為總線的空閑狀態。此時各個器件的輸出級場效應管均處在截止狀態,即釋放總線,由兩條信號線各自的上拉電阻把電平拉高。

②啟動信號。

在時鐘線SCL保持高電平期間,數據線SDA上的電平被拉低(即負跳變),定義為I2C總線總線的啟動信號,它標志著一次數據傳輸的開始。

啟動信號是一種電平跳變時序信號,而不是一個電平信號。啟動信號是由主控器主動建立的,在建立該信號之前I2C總線必須處于空閑狀態,如圖1所示。

圖1 I2C總線上的啟動信號和停止信號

③停止信號。

在時鐘線SCL保持高電平期間,數據線SDA被釋放,使得SDA返回高電平(即正跳變),稱為I2C總線的停止信號,它標志著一次數據傳輸的終止。

停止信號也是一種電平跳變時序信號,而不是一個電平信號,停止信號也是由主控器主動建立的,建立該信號之后,I2C總線將返回空閑狀態。

④數據位傳送。

在I2C總線上傳送的每一位數據都有一個時鐘脈沖相對應(或同步控制),即在SCL串行時鐘的配合下,在SDA上逐位地串行傳送每一位數據。

進行數據傳送時,在SCL呈現高電平期間,SDA上的電平必須保持穩定,低電平為數據0,高電平為數據1。

只有在SCL為低電平期間,才允許SDA上的電平改變狀態。邏輯0的電平為低電壓,而邏輯1的電平取決于器件本身的正電源電壓VDD(當使用獨立電源時),如圖2所示。

圖2 I2C總線上的數據位傳送

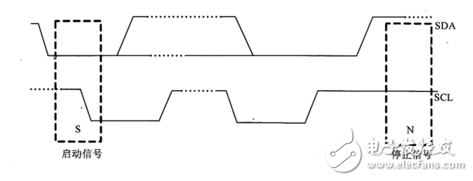

⑤應答信號。

I2C總線上的所有數據都是以8位字節傳送的,發送器每發送一個字節,就在時鐘脈沖9期間釋放數據線,由接收器反饋一個應答信號。

應答信號為低電平時,規定為有效應答位(ACK簡稱應答位),表示接收器已經成功地接收了該字節;應答信號為高電平時,規定為非應答位(NACK),一般表示接收器接收該字節沒有成功。

對于反饋有效應答位ACK的要求是,接收器在第9個時鐘脈沖之前的低電平期間將SDA線拉低,并且確保在該時鐘的高電平期間為穩定的低電平。

如果接收器是主控器,則在它收到最后一個字節后,發送一個NACK信號,以通知被控發送器結束數據發送,并釋放SDA線,以便主控接收器發送一個停止信號P,如圖3所示。

圖3 I2C總線上的應答時序

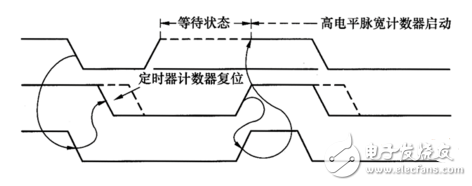

⑥插入等待時間。

如果被控器需要延遲下一個數據字節開始傳送的時間,則可以通過把時鐘線SCL電平拉低并且保持,使主控器進入等待狀態。

一旦被控器釋放時鐘線,數據傳輸就得以繼續下去,這樣就使得被控器得到足夠時間轉移已經收到的數據字節,或者準備好即將發送的數據字節。

帶有CPU的被控器在對收到的地址字節做出應答之后,需要一定的時間去執行中斷服務子程序,來分析或比較地址碼,其間就把SCL線鉗位在低電平上,直到處理妥當后才釋放SCL線,進而使主控器繼續后續數據字節的發送,如圖4所示。

圖4 I2C總線上的插入等待時間

⑦重啟動信號。

在主控器控制總線期間完成了一次數據通信(發送或接收)之后,如果想繼續占用總線再進行一次數據通信(發送或接收),而又不釋放總線,就需要利用重啟動Sr信號時序。

重啟動信號Sr既作為前一次數據傳輸的結束,又作為后一次數據傳輸的開始。利用重啟動信號的優點是,在前后兩次通信之間主控器不需要釋放總線,這樣就不會丟失總線的控制權,即不讓其他主器件節點搶占總線。

⑧時鐘同步。

如果在某一I2C總線系統中存在兩個主器件節點,分別記為主器件1和主器件2,其時鐘輸出端分別為CLK1和CL【0,它們都有控制總線的能力。

假設在某一期間兩者相繼向SCL線發出了波形不同的時鐘脈沖序列CLK1和CLK2(時鐘脈沖的高、低電平寬度都是依靠各自內部專用計數器定時產生的),在總線控制權還沒有裁定之前這種現象是可能出現的。

鑒于I2C總線的“線與”特性,使得時鐘線SCL上得到的時鐘信號波形,既不像主器件1所期望的CLK1,也不像主器件2所期望的CLK2,而是兩者進行邏輯與的結果。

CLKI和CLK2的合成波形作為共同的同步時鐘信號,一旦總線控制權裁定給某一主器件,則總線時鐘信號將會只由該主器件產生,如圖5所示。

圖5 I2C總線上的時鐘同步

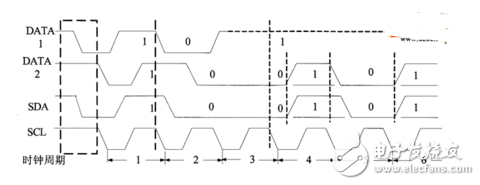

⑨總線沖突和總線仲裁。

假如在某I2C總線系統中存在兩個主器件節點,分別記為主器件1和主器件2,其數據輸出端分別為DATA1和DATA2,它們都有控制總線的能力,這就存在著發生總線沖突(即寫沖突)的可能性。

假設在某一瞬間兩者相繼向總線發出了啟動信號,鑒于:I2C總線的“線與”特性,使得在數據線SDA上得到的信號波形是DATA1和DATA2兩者相與的結果,該結果略微超前送出低電平的主器件1,其DATA1的下降沿被當做SDA的下降沿。

在總線被啟動后,主器件1企圖發送數據“101……”,主器件2企圖發送數據“100101……”。

兩個主器件在每次發出一個數據位的同時都要對自己輸出端的信號電平進行抽檢,只要抽檢的結果與它們自己預期的電平相符,就會繼續占用總線,總線控制權也就得不到裁定結果。

主器件1的第3位期望發送“1”,也就是在第3個時鐘周期內送出高電平。

在該時鐘周期的高電平期間,主器件1進行例行抽檢時,結果檢測到一個不相匹配的電平“0”,這時主器件1只好決定放棄總線控制杈;因此,主器件2就成了總線的惟一主宰者,總線控制權也就最終得出了裁定結果,從而實現了總線仲裁的功能。

從以上總線仲裁的完成過程可以得出:仲裁過程主器件1和主器件2都不會丟失數據;各個主器件沒有優先級別之分,總線控制權是隨機裁定的,即使是搶先發送啟動信號的主器件1最終也并沒有得到控制杈。

系統實際上遵循的是“低電平優先”的仲裁原則,將總線判給在數據線上先發送低電平的主器件,而其他發送高電平的主器件將失去總線控制權,如圖6所示。

圖6 I2C總線上的總線仲裁

⑩總線封鎖狀態。

在特殊情況下,如果需要禁止所有發生在I2C總線上的通信活動,封鎖或關閉總線是一種可行途徑,只要掛接于該總線上的任意一個器件將時鐘線SCL鎖定在低電平上即可。

I2C總線是由Philips公司開發的兩線式串行總線,用于連接微控制器和外圍設備。

I2C總線支持多主控模式,任何能夠進行發送和接收的設備都可以成為主設備。主控能夠控制數據的傳輸和時鐘頻率,在任意的時刻只能有一個主控。

組成I2C總線的兩個信號為數據線SDA和時鐘線SCL。為避免總信號線的混亂,要求各設備連接到總線的輸出端必須是開漏輸出或集電極開路輸出的結構。根據這種結構的“線與”邏輯,I2C總線上任意器件輸出低電平都會使相應總線上的信號線變低。

總線空閑時,上拉電阻使SDA和SCL線都保持高電平。

數據線 SDA 的電平狀態必須在時鐘線 SCL 處于高電平期間保持穩定不變。SDA 的電平狀態只有在 SCL 處于低電平期間才允許改變。但是在 I2C總線的起始和結束時例外。

當SCL穩定在高電平時,SDA由高到低的變化將產生一個開始位,而由低到高的變化則產生一個停止位。開始位和停止位都是由I2C主設備產生的。如果從設備采用7位地址,則主設備在發起傳輸前,需先發送一字節的地址信息,前7位為設備地址,最后1位為讀寫標志。之后每次傳輸的數據也是一個字節,從MSB位(Most Significant Bit 最高有效位,對應有LSB: Least Significant Bit 最低有效位)開始傳輸。每個字節傳完后,在SCL的第9個上升沿到來之前,接受方應該發出一個ACK位。

應答位的時鐘脈沖仍由主機產生,而應答位的數據狀態則遵循“誰接收誰產生”的原則,即總是由接收器產生應答位。主機向從機發送數據時,應答位由從機產生;主機從從機接收數據時,應答位由主機產生。I2C總線標準規定:應答位為 0 表示接收器應答(ACK) ,常常簡記為 A;為 1 則表示非應答(NACK) ,常常簡記為NA。發送器發送完 LSB 之后,應當釋放 SDA 線(拉高 SDA,輸出晶體管截止) ,以等待接收器產生應答位。

在切換數據的傳輸方向時,可以不必先產生停止條件再開始下次傳輸,而是直接再一次產生開始條件。I2C 總線在已經處于忙的狀態下,再一次直接產生起始條件的情況被稱為重復起始條件。例如:訪問某一具有 I2C總線接口的 E2PROM 存儲器時,主機先向存儲器輸入存儲單元的地址信息(發送數據) ,然后再讀取其中的存儲內容(接收數據)。

帶有 I2C 總線的器件除了有從機地址(Slave Address)外,還可能有子地址。從機地址是指該器件在 I2C 總線上被主機尋址的地址, 而子地址是指該器件內部不同部件或存儲單元的編址。 與從機地址一樣,子地址實際上也是像普通數據那樣進行傳輸的,傳輸格式仍然是與數據相統一的,區分傳輸的到底是地址還是數據要靠收發雙方具體的邏輯約定。子地址的長度必須由整數個字節組成,可能是單字節(8 位子地址) ,也可能是雙字節(16 位子地址) ,還可能是 3 字節以上,這要看具體器件的規定。

I2C體系結構分3個部分:I2C核心、I2C總線驅動、I2C設備驅動。

I2C核心提供了I2C總線驅動和設備驅動的注冊、注銷方法,I2C通信方法上層的、與具體適配器無關的代碼以及探測設備、檢測設備地址的上層代碼等。

I2C總線驅動是對I2C硬件體系結構中適配器端的實現,適配器可由CPU控制,甚至可以直接集成在CPU內部。包含了i2c_adapter、i2c_algorithm和控制I2C適配器產生通信信號的函數。通過I2C總線驅動的代碼,我們可以控制I2C適配器以主控方式產生開始位、停止位讀寫周期,以及以從設備方式被讀寫,產生ACK等。

I2C設備驅動是對I2C硬件體系結構中設備端的實現,設備一般掛接在受CPU控制的I2C適配器上,通過I2C適配器與CPU交換數據。包含了i2c_driver和i2c_client。

所有的I2C設備都在sysfs文件系統中顯示,存于/sys/bus/i2c/目錄下,以適配器地址和芯片地址的形式列出。

i2c_adapter對應于物理上的一個適配器,而i2c_algorithm對應一套通信方法。一個I2C適配器需要i2c_algorithm提供的通信函數來控制適配器上產生特定的訪問周期。缺少i2c_algorithm的i2c_adapter什么也做不了,因此i2c_adapter中包含其使用的i2c_algorithm的指針。

i2c_driver對應一套驅動方法,是純粹的用于輔助作用的數據結構,它不對應于任何的物理實體。i2c_client對應于真實的物理設備,每個I2C設備都需要一個i2c_client來描述。i2c_client一般被包含在I2C字符設備的私有信息結構體中。

i2c_driver于i2c_client發生關聯的時刻在i2c_driver的attach_adapter()函數被運行時。attach_adapter()會探測物理設備,當確定一個client存在時,把該client使用的i2c_client數據結構的adapter指針指向對應的i2c_adapter,driver指針指向該i2c_driver,并會調用i2c_adapter的client_register()函數。相反的過程會發生在i2c_driver的detach_client()函數被調用的時候。

i2c_transfer()函數用于進行I2C適配器和I2C設備之間的一組消息交互,i2c_master_send()函數和i2c_master_recv()函數內部會調用i2c_transfer()函數分別完成一條寫消息和一條讀消息。i2c_transfer()函數本身并不具備驅動適配器物理硬件完成消息交互的能力,它只是尋找到i2c_adapter對應的i2c_algorithm,并使用i2c_algorithm的master_xfer函數真正驅動硬件流程。

I2C總線驅動模塊加載函數需完成兩個工作:

1.初始化I2C適配器所使用的硬件資源,如申請I/O地址、中斷號等。

2.通過i2c_add_adapter()添加i2c_adapter的數據結構,當然這個i2c_adapter數據結構的成員已經被xxx適配器的相應函數指針所初始化。

I2C總線驅動模塊的卸載函數要完成的工作與加載函數相反。

I2C總線通信方法:我們要為特定的I2C適配器實現其通信方法,主要實現i2c_algorithm的master_xfer()函數和functionality()函數。functionality()函數用于返回algorithm所支持的通信協議,如I2C_FUNC_I2C、I2C_FUNC_10BIT_ADDR、I2C_FUNC_SMBUS_READ_BYTE、I2C_FUNC_SMBUS_WRITE_BYTE等。master_xfer()函數在I2C適配器上完成傳遞給它的i2c_msg數組中的每個I2C消息。

master_xfer()函數處理I2C消息數組,對于數組中的每個消息,判斷消息類型,若為讀消息,則賦從設備地址為(msg-》addr《《1)| 1 ,否則為msg-》addr《《1(賦地址為setaddr)。對每個消息產生一個開始位,緊接著傳送從設備地址,然后開始數據的發送或接收,對最后的消息還需產生一個停止位。

I2C設備驅動(i2c_driver和i2c_client)。

I2C設備驅動要使用i2c_driver和i2c_client數據結構并填充其中的成員函數。i2c_client一般被包含在設備的私有信息結構體yyy_data中,而i2c_driver則適合被定義成全局變量并初始化。

I2C設備驅動的模塊加載函數中會做:

(1)通過register_chrdev()函數將I2C設備注冊為一個字符設備。

(2)通過I2C核心的i2c_add_driver()函數添加i2c_driver。

模板卸載函數中則相反。

yyy_init()-》i2c_add_driver()-》yyy_attach_adapter()-》i2c_probe()-》yyy_detect()-》i2c_client初始化-》i2c_attach_client()-》yyy_init_client

yyy_exit()-》i2c_del_driver()-》yyy_detach_client()-》i2c_detach_client()

作為一種字符類設備,Linux I2C設備驅動的文件操作接口與普通的設備驅動是完全一致的。I2C設備的寫操作經歷了如下幾個步驟:

(1)從用戶空間到字符設備驅動寫函數接口,寫函數構造I2C消息數組。

(2)寫函數把構造的I2C消息數組傳遞給I2C核心的傳輸函數i2c_transfer()。

(3)I2C核心的傳輸函數i2c_transfer()找到對應適配器algorithm的通信方法函數master_xfer()去最終完成I2C消息的處理。

read()/write()(用戶空間)-》yyy_read()/yyy_write()(I2C設備驅動文件操作接口)-》i2c_transfer()(I2C核心)-》master_xfer()(I2C總線驅動)

i2c-dev.c文件完全可以被看做一個I2C設備驅動,不過,它實現的一個i2c_client是虛擬、臨時的,隨著設備文件的打開而產生,并隨設備文件的關閉而撤銷,并沒有被添加到i2c_adapter的clients鏈表中。i2c-dev.c針對每個I2C適配器生成一個主設備號為89的設備文件,實現了i2c_driver的成員函數以及文件操作接口,所以,i2c-dev.c的主體式“i2c_driver成員函數+字符設備驅動”。

i2c-dev.c中提供i2cdev_read()、i2cdev_write()函數來對應用戶空間要使用的read()和write()文件操作接口,這兩個函數分別調用I2C核心的i2c_master_recv()和i2c_master_send()函數來構造一條I2C消息并引發適配器algorithm通信函數的調用,完成消息的傳輸。i2cdev_read()和i2cdev_write()函數不具備太強的通用性,滅有太大的使用價值,只能適用于非RepStart模式的情況。對于兩條以上消息組成的讀寫,在用戶空間需要組織i2c_msg消息數組并調用I2C_RDWR IOCTL命令。

電子發燒友App

電子發燒友App

評論