什么是SPI

SPI是串行外設(shè)接口(Serial Peripheral Interface)的縮寫。SPI,是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳,同時(shí)為PCB的布局上節(jié)省空間,提供方便,正是出于這種簡單易用的特性,如今越來越多的芯片集成了這種通信協(xié)議,比如AT91RM9200。

SPI協(xié)議概括

SPI的通信原理很簡單,它以主從方式工作,這種模式通常有一個(gè)主設(shè)備和一個(gè)或多個(gè)從設(shè)備,需要至少4根線,事實(shí)上3根也可以(單向傳輸時(shí))。也是所有基于SPI的設(shè)備共有的,它們是SDI(數(shù)據(jù)輸入)、SDO(數(shù)據(jù)輸出)、SCLK(時(shí)鐘)、CS(片選)。

(1)SDI – SerialData In,串行數(shù)據(jù)輸入;

(2)SDO – SerialDataOut,串行數(shù)據(jù)輸出;

(3)SCLK – Serial Clock,時(shí)鐘信號(hào),由主設(shè)備產(chǎn)生;

(4)CS – 從設(shè)備使能信號(hào),由主設(shè)備控制。

什么是I2C總線

I2C--INTER-IC串行總線的縮寫,是PHILIPS公司推出的芯片間串行傳輸總線。它以1根串行數(shù)據(jù)線(SDA)和1根串行時(shí)鐘線(SCL)實(shí) 現(xiàn)了雙工的同步數(shù)據(jù)傳輸。具有接口線少,控制方式簡化,器件封裝形式小,通信速率較高等優(yōu)點(diǎn)。在主從通信中,可以有多個(gè)I2C總線器件同時(shí)接到I2C總線 上,通過地址來識(shí)別通信對(duì)象。

I2C 接口的協(xié)議里面包括設(shè)備地址信息,可以同一總線上連接多個(gè)從設(shè)備,通過應(yīng)答來互通數(shù)據(jù)及命令。但是傳輸速率有限,標(biāo)準(zhǔn)模式下可達(dá)到100Kbps,快速模式下可達(dá)到400Kbps(我們開發(fā)板一般在130Kbps),高速模式下達(dá)到4Mbps,不能實(shí)現(xiàn)全雙工,不適合傳輸很多的數(shù)據(jù)。

I2C總線是一個(gè)真正的多主機(jī)總線,總線上多個(gè)主機(jī)初始化傳輸,可以通過傳輸檢測(cè)和仲裁來防止數(shù)據(jù)被破壞 。

下來詳細(xì)了解I2C總線時(shí)序:

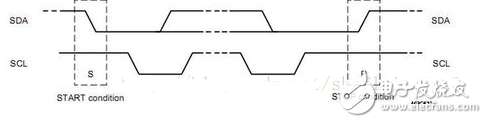

1.1 總線數(shù)據(jù)有效性

I2C總線是單工,因此同一時(shí)刻數(shù)據(jù)只有一個(gè)流向,因此采樣有效時(shí)鐘也是單一的,是在SCL時(shí)鐘的高電平采樣數(shù)據(jù)。

I2C總線上SDA數(shù)據(jù)在SCL時(shí)鐘低電平是可以發(fā)生變化,但是在時(shí)鐘高電平時(shí)必須穩(wěn)定,以便主從設(shè)備根據(jù)時(shí)鐘采樣數(shù)據(jù),如下圖:

1.2 總線空閑條件

I2C總線上設(shè)備都釋放總線(發(fā)出傳輸停止)后,I2C總線根據(jù)上拉電阻變成高電平,SDA SCL都是高電平。

1.3 總線數(shù)據(jù)傳輸起始和結(jié)束條件

I2C總線SCL高電平時(shí)SDA出現(xiàn)由高到低的跳變,標(biāo)志總線上數(shù)據(jù)傳輸?shù)拈_始條件

I2C總線SCL高電平時(shí)SDA出現(xiàn)由低到高的跳變,標(biāo)志總線上數(shù)據(jù)傳輸?shù)慕Y(jié)束條件

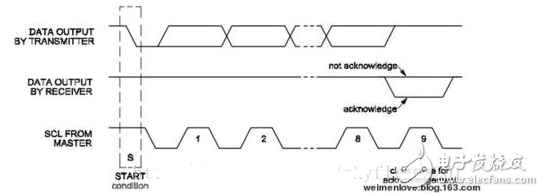

1.4 總線數(shù)據(jù)傳輸順序以及ACK應(yīng)答

I2C總線上數(shù)據(jù)傳輸室MSB在前,LSB在后,從示波器上看,從左向右依次讀出數(shù)據(jù)即可

I2C總線傳輸?shù)臄?shù)據(jù)不收限制,但是每次發(fā)到SDA上的必須是8位,并且主機(jī)發(fā)送8位后釋放總線,從機(jī)收到數(shù)據(jù)后必須拉低SDA一個(gè)時(shí)鐘,回應(yīng)ACK表示數(shù)據(jù)接收成功,我們?nèi)绻静ㄆ魃峡吹降牟ㄐ尉褪敲看?位數(shù)據(jù),8bit+1bit ack。如下:

從機(jī)收到一字節(jié)數(shù)據(jù)后,如果需要一些時(shí)間處理,則會(huì)拉低SCL,讓傳輸進(jìn)入等待狀態(tài),處理完成,釋放SCL,繼續(xù)傳輸,如下:

1.5 總線讀寫時(shí)序

數(shù)據(jù)的傳輸在起始條件之后,發(fā)送一個(gè)7位的從機(jī)地址,緊接著第8位是數(shù)據(jù)方向(R/ W),0-表示發(fā)送數(shù)據(jù)(寫),1-表示接收數(shù)據(jù)(讀)。數(shù)據(jù)傳輸一般由主機(jī)產(chǎn)生的停止位(P)終止。但是如果主機(jī)仍希望在總線上通訊,它可以產(chǎn)生重復(fù)起始條件(Sr),和尋址另一個(gè)從機(jī),而不是首先產(chǎn)生一個(gè)停止條件。在這種傳輸中,可能有不同的讀/寫格式結(jié)合。

I2C總線主設(shè)備讀寫從設(shè)備,一般都是與從設(shè)備的寄存器打交道,這個(gè)可以通過閱讀從設(shè)備的datasheet獲取。總線寫時(shí)序如下:

master start + master addr|w + slave ack + master reg|w + slave ack + master data + slave ack + master restart。。master data + slave nack + master stop

總線讀時(shí)序如下:

master start + master addr|w + slave ack + master reg|w + slave ack + master restart + master addr|r + slave ack + slave data + master nack + master stop

總線讀時(shí)序與寫的不同之處在于讀需要2次傳輸才能完成一次讀取,首先要寫寄存器地址到從設(shè)備,其實(shí)是寫到了從設(shè)備的控制寄存器或者命令寄存器,從設(shè)備內(nèi)部會(huì)根據(jù)這個(gè)地址來尋址所要操作的寄存器。

我在讀我們的bios和內(nèi)核時(shí)發(fā)現(xiàn),2者在總線讀時(shí)序上的實(shí)現(xiàn)不太一樣,在于第一次寄存器地址寫入后,一個(gè)發(fā)的是restart,一個(gè)發(fā)的是stop,然后再start開始讀取數(shù)據(jù),示波器抓波形發(fā)現(xiàn)讀取數(shù)據(jù)都正確,說明這2種時(shí)序都是正確的。

I2C總線的讀寫時(shí)序比較固定,設(shè)備通信嚴(yán)格遵循協(xié)議,因此I2C總線設(shè)備驅(qū)動(dòng)程序的編寫也就相對(duì)簡單一些。

主要應(yīng)用的I2C總線設(shè)備有touchscreen rtc 外擴(kuò)io等

SPI總線

SPI--Serial Peripheral Interface,串行外圍設(shè)備接口,是Motorola公司推出的一種同步串行通訊方式,是一種三線同步總線,因其硬件功能很強(qiáng),與SPI有關(guān)的軟件就相當(dāng)簡單,使CPU有更多的時(shí)間處理其他事務(wù)。

SPI通常有SCK時(shí)鐘,STB片選,DATA數(shù)據(jù)信號(hào)三個(gè)信號(hào)。 I2C通常有 SDA數(shù)據(jù)和SCL時(shí)鐘兩個(gè)信號(hào)。

SPI總線真正實(shí)現(xiàn)了全雙工數(shù)據(jù)傳輸,SPI 有3線跟4線兩種,4線的話,就是多了一條叫SDC的線,用來告知從設(shè)備現(xiàn)在傳輸?shù)氖菙?shù)據(jù)還是指令。這個(gè)接口較快,可以傳輸較連續(xù)的數(shù)據(jù)。SPI要想連接多個(gè)從設(shè)備,就需要給每個(gè)從設(shè)備配備一根片選信號(hào)。如果要可以實(shí)現(xiàn)全雙工,也是需要多加一根數(shù)據(jù)線(MOSI MISO)。

也就是說SPI總線是通過片選來選擇從設(shè)備。

spi總線速度要比I2C要快,我們開發(fā)板最快能達(dá)到30MHZ。

spi總線特點(diǎn):

1. 采用主-從模式(Master-Slave) 的控制方式

SPI 規(guī)定了兩個(gè) SPI 設(shè)備之間通信必須由主設(shè)備 (Master) 來控制次設(shè)備 (Slave)。 一個(gè) Master 設(shè)備可以通過提供 Clock 以及對(duì) Slave 設(shè)備進(jìn)行片選 (Slave Select) 來控制多個(gè) Slave 設(shè)備, SPI 協(xié)議還規(guī)定 Slave 設(shè)備的 Clock 由 Master 設(shè)備通過 SCK 管腳提供給 Slave 設(shè)備, Slave 設(shè)備本身不能產(chǎn)生或控制 Clock, 沒有 Clock 則 Slave 設(shè)備不能正常工作。

2. 采用同步方式(Synchronous)傳輸數(shù)據(jù)

Master 設(shè)備會(huì)根據(jù)將要交換的數(shù)據(jù)來產(chǎn)生相應(yīng)的時(shí)鐘脈沖(Clock Pulse), 時(shí)鐘脈沖組成了時(shí)鐘信號(hào)(Clock Signal) , 時(shí)鐘信號(hào)通過時(shí)鐘極性 (CPOL) 和 時(shí)鐘相位 (CPHA) 控制著兩個(gè) SPI 設(shè)備間何時(shí)數(shù)據(jù)交換以及何時(shí)對(duì)接收到的數(shù)據(jù)進(jìn)行采樣, 來保證數(shù)據(jù)在兩個(gè)設(shè)備之間是同步傳輸?shù)摹?/p>

3. 數(shù)據(jù)交換(Data Exchanges)

SPI 設(shè)備間的數(shù)據(jù)傳輸之所以又被稱為數(shù)據(jù)交換, 是因?yàn)?SPI 協(xié)議規(guī)定一個(gè) SPI 設(shè)備不能在數(shù)據(jù)通信過程中僅僅只充當(dāng)一個(gè) “發(fā)送者(Transmitter)” 或者 “接收者(Receiver)”。 也就是說是全雙工的,在每個(gè) Clock 周期內(nèi), SPI 設(shè)備都會(huì)發(fā)送并接收一個(gè) bit 大小的數(shù)據(jù), 相當(dāng)于該設(shè)備有一個(gè) bit 大小的數(shù)據(jù)被交換了。

一個(gè) Slave 設(shè)備要想能夠接收到 Master 發(fā)過來的控制信號(hào), 必須在此之前能夠被 Master 設(shè)備進(jìn)行訪問 (Access)。 所以, Master 設(shè)備必須首先通過 SS/CS pin 對(duì) Slave 設(shè)備進(jìn)行片選, 把想要訪問的 Slave 設(shè)備選上。

在數(shù)據(jù)傳輸?shù)倪^程中, 每次接收到的數(shù)據(jù)必須在下一次數(shù)據(jù)傳輸之前被采樣。 如果之前接收到的數(shù)據(jù)沒有被讀取, 那么這些已經(jīng)接收完成的數(shù)據(jù)將有可能會(huì)被丟棄, 導(dǎo)致 SPI 物理模塊最終失效。 因此, 在程序中一般都會(huì)在 SPI 傳輸完數(shù)據(jù)后, 去讀取 SPI 設(shè)備里的數(shù)據(jù), 即使這些數(shù)據(jù)(Dummy Data)在我們的程序里是無用的。

具體spi工作原理可以看博客另外一篇文章

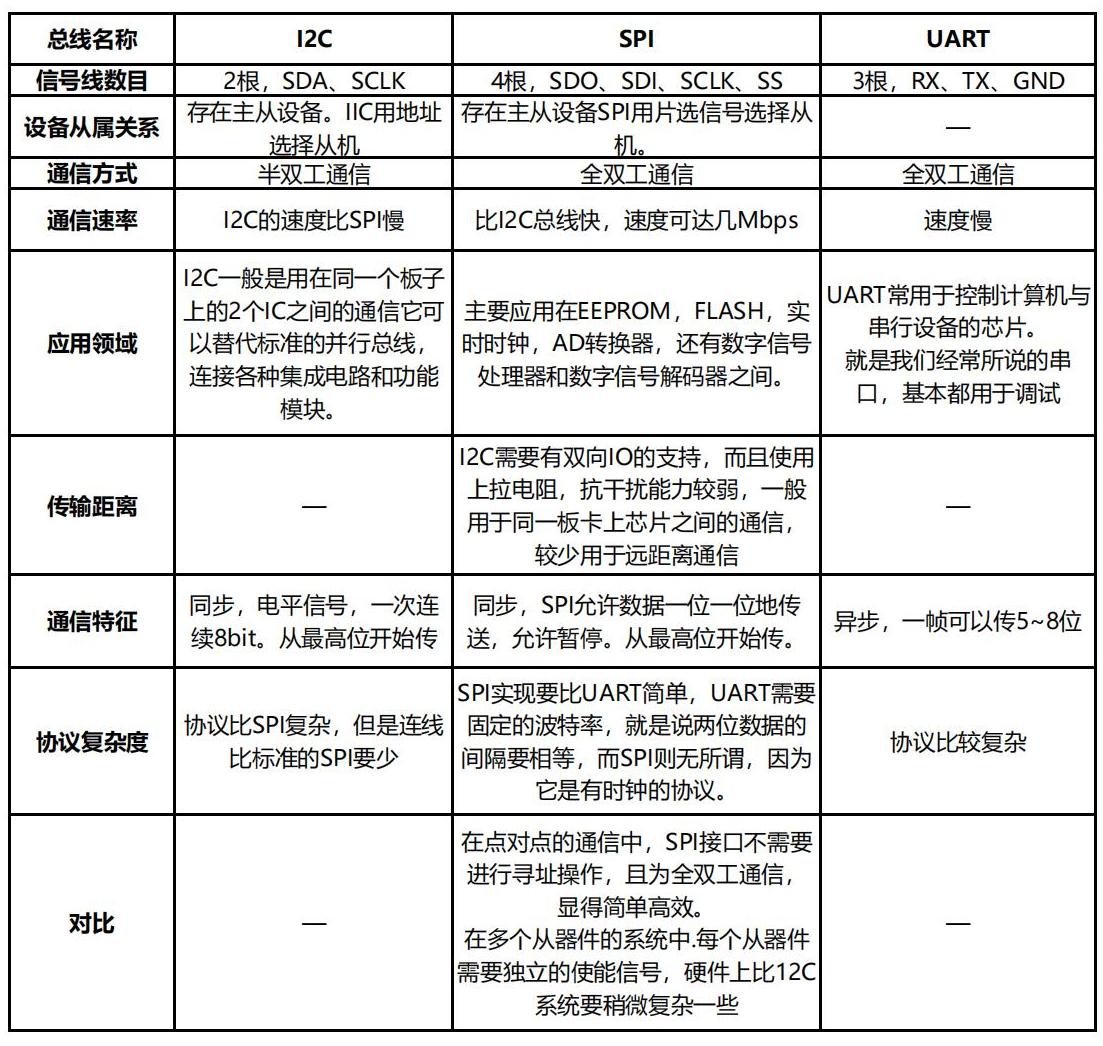

SPI和I2C是2種不同的通信協(xié)議,現(xiàn)在已經(jīng)廣泛的應(yīng)用在IC之間的通信中。并且不少單片機(jī)已經(jīng)整和了SPI和I2C的借口。但像51這種不支持SPI和I2C的單片機(jī),也可以用模擬時(shí)鐘的工作方式進(jìn)行SPI和I2C的通信的。

下面主要總結(jié)一下2種總線的異同點(diǎn):

1 I2C總線不是全雙工,2根線SCL SDA。spi總線實(shí)現(xiàn)全雙工,4根線SCK CS MOSI MISO

2 I2C總線是多主機(jī)總線,通過SDA上的地址信息來鎖定從設(shè)備。spi總線只有一個(gè)主設(shè)備,主設(shè)備通過CS片選來確定從設(shè)備

3 I2C總線傳輸速度在100kbps-4Mbps。spi總線傳輸速度更快,可以達(dá)到30MHZ以上。

4 I2C總線空閑狀態(tài)下SDA SCL都是高電平。spi總線空閑狀態(tài)MOSI MISO也都是 SCK是有CPOL決定的

5 I2C總線scl高電平時(shí)sda下降沿標(biāo)志傳輸開始,上升沿標(biāo)志傳輸結(jié)束。spi總線cs拉低標(biāo)志傳輸開始,cs拉高標(biāo)志傳輸結(jié)束

6 I2C總線是SCL高電平采樣。spi總線因?yàn)槭侨p工,因此是沿采樣,具體要根據(jù)CPHA決定。一般情況下master device是SCK的上升沿發(fā)送,下降沿采集

7 I2C總線和spi總線數(shù)據(jù)傳輸都是MSB在前,LSB在后(串口是LSB在前)

8 I2C總線和spi總線時(shí)鐘都是由主設(shè)備產(chǎn)生,并且只在數(shù)據(jù)傳輸時(shí)發(fā)出時(shí)鐘

9 I2C總線讀寫時(shí)序比較固定統(tǒng)一,設(shè)備驅(qū)動(dòng)編寫方便。spi總線不同從設(shè)備讀寫時(shí)序差別比較大,因此必須根據(jù)具體的設(shè)備datasheet來實(shí)現(xiàn)讀寫,相對(duì)復(fù)雜一些。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論