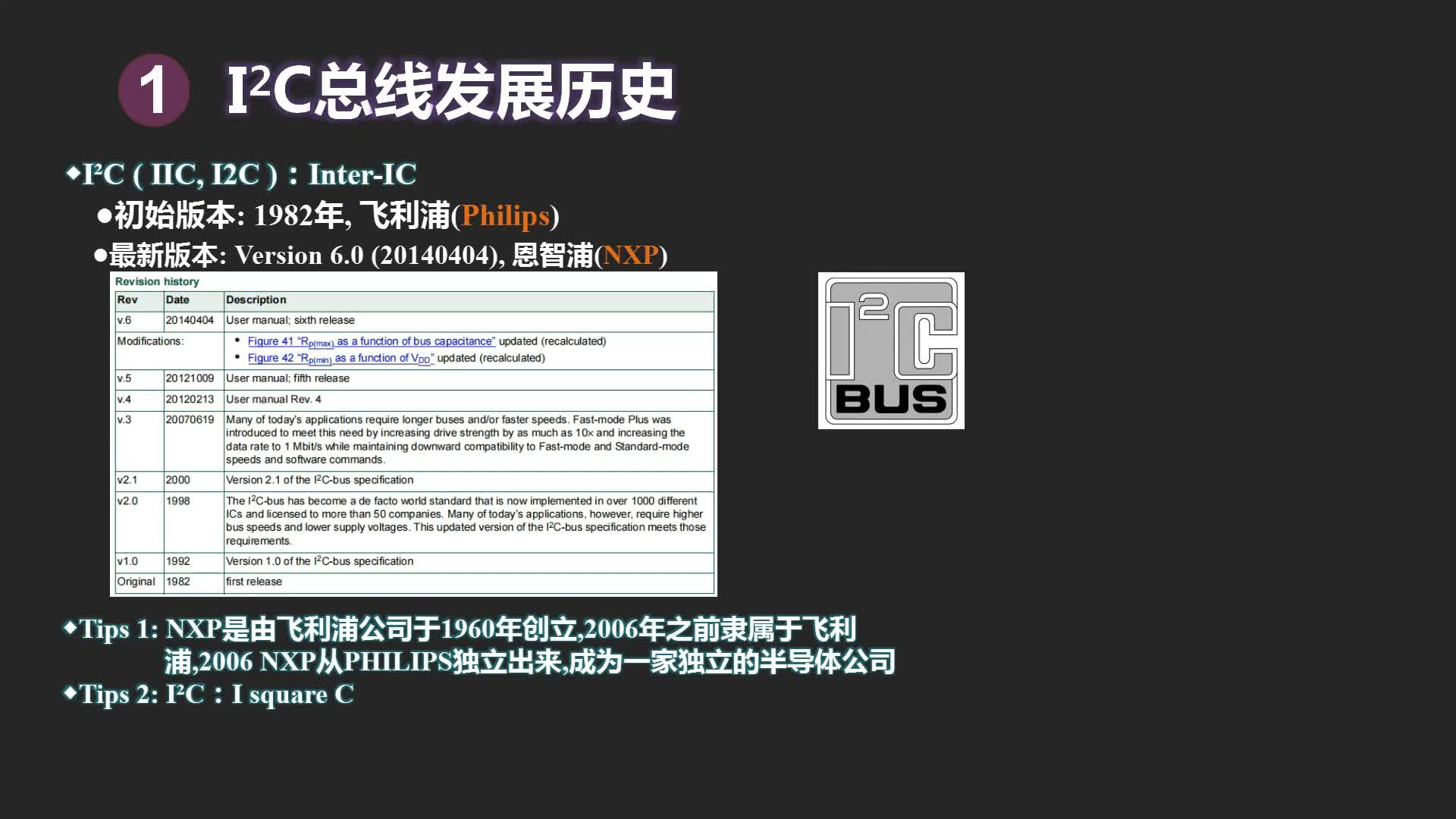

I2C(Inter-Integrated Circuit)總線是一種由PHILIPS公司開發(fā)的兩線式串行總線,用于連接微控制器及其外圍設(shè)備。I2C總線產(chǎn)生于在80年代,最初為音頻和視頻設(shè)備開發(fā),如今主要在服務(wù)器管理中使用,其中包括單個組件狀態(tài)的通信。例如管理員可對各個組件進(jìn)行查詢,以管理系統(tǒng)的配置或掌握組件的功能狀態(tài),如電源和系統(tǒng)風(fēng)扇。可隨時監(jiān)控內(nèi)存、硬盤、網(wǎng)絡(luò)、系統(tǒng)溫度等多個參數(shù),增加了系統(tǒng)的安全性,方便了管理。

1 I2C總線特點(diǎn)

I2C總線最主要的優(yōu)點(diǎn)是其簡單性和有效性。由于接口直接在組件之上,因此I2C總線占用的空間非常小,減少了電路板的空間和芯片管腳的數(shù)量,降低了互聯(lián)成本。總線的長度可高達(dá)25英尺,并且能夠以10Kbps的最大傳輸速率支持40個組件。I2C總線的另一個優(yōu)點(diǎn)是,它支持多主控(multimastering), 其中任何能夠進(jìn)行發(fā)送和接收的設(shè)備都可以成為主總線。一個主控能夠控制信號的傳輸和時鐘頻率。當(dāng)然,在任何時間點(diǎn)上只能有一個主控。

2 總線的構(gòu)成及信號類型

I2C總線是由數(shù)據(jù)線SDA和時鐘SCL構(gòu)成的串行總線,可發(fā)送和接收數(shù)據(jù)。在CPU與被控IC之間、IC與IC之間進(jìn)行雙向傳送,最高傳送速率100kbps。各種被控制電路均并聯(lián)在這條總線上,但就像電話機(jī)一樣只有撥通各自的號碼才能工作,所以每個電路和模塊都有唯一的地址,在信息的傳輸過程中,I2C總線上并接的每一模塊電路既是主控器(或被控器),又是發(fā)送器(或接收器),這取決于它所要完成的功能。CPU發(fā)出的控制信號分為地址碼和控制量兩部分,地址碼用來選址,即接通需要控制的電路,確定控制的種類;控制量決定該調(diào)整的類別(如對比度、亮度等)及需要調(diào)整的量。這樣,各控制電路雖然掛在同一條總線上,卻彼此獨(dú)立,互不相關(guān)。

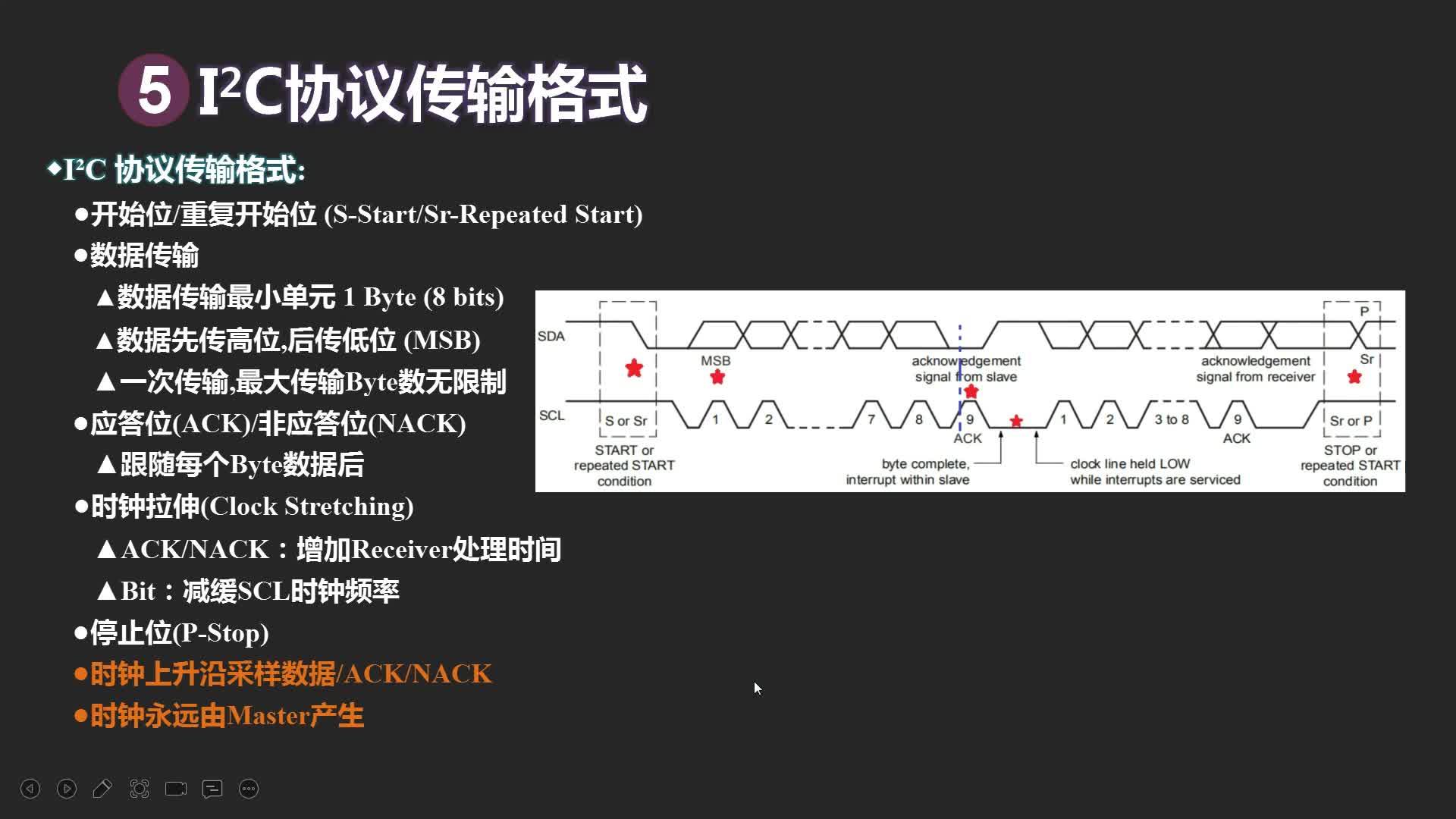

I2C總線在傳送數(shù)據(jù)過程中共有三種類型信號, 它們分別是:開始信號、結(jié)束信號和應(yīng)答信號。

開始信號:SCL為高電平時,SDA由高電平向低電平跳變,開始傳送數(shù)據(jù)。

結(jié)束信號:SCL為高電平時,SDA由低電平向高電平跳變,結(jié)束傳送數(shù)據(jù)。

應(yīng)答信號:接收數(shù)據(jù)的IC在接收到8bit數(shù)據(jù)后,向發(fā)送數(shù)據(jù)的IC發(fā)出特定的低電平脈沖,表示已收到數(shù)據(jù)。CPU向受控單元發(fā)出一個信號后,等待受控單元發(fā)出一個應(yīng)答信號,CPU接收到應(yīng)答信號后,根據(jù)實(shí)際情況作出是否繼續(xù)傳遞信號的判斷。若未收到應(yīng)答信號,由判斷為受控單元出現(xiàn)故障。

目前有很多半導(dǎo)體集成電路上都集成了I2C接口。帶有I2C接口的單片機(jī)有:CYGNAL的 C8051F0XX系列,PHILIPSP87LPC7XX系列,MICROCHIP的PIC16C6XX系列等。很多外圍器件如存儲器、監(jiān)控芯片等也提供I2C接口。

在I2C總線通信的過程中,參與通信的雙方互相之間所傳輸?shù)男畔⒎N類歸納如下。

主控器向被控器發(fā)送的信息種類有:啟動信號、停止信號、7位地址碼、讀/寫控制位、10位地址碼、數(shù)據(jù)字節(jié)、重啟動信號、應(yīng)答信號、時鐘脈沖。

被控器向主控器發(fā)送的信息種類有:應(yīng)答信號、數(shù)據(jù)字節(jié)、時鐘低電平。

下面對I2C總線通信過程中出現(xiàn)的幾種信號狀態(tài)和時序進(jìn)行分析。

①總線空閑狀態(tài)。

I2C總線總線的SDA和SCL兩條信號線同時處于高電平時,規(guī)定為總線的空閑狀態(tài)。此時各個器件的輸出級場效應(yīng)管均處在截止?fàn)顟B(tài),即釋放總線,由兩條信號線各自的上拉電阻把電平拉高。

②啟動信號。

在時鐘線SCL保持高電平期間,數(shù)據(jù)線SDA上的電平被拉低(即負(fù)跳變),定義為I2C總線總線的啟動信號,它標(biāo)志著一次數(shù)據(jù)傳輸?shù)拈_始。

啟動信號是一種電平跳變時序信號,而不是一個電平信號。啟動信號是由主控器主動建立的,在建立該信號之前I2C總線必須處于空閑狀態(tài),如圖1所示

③停止信號。

在時鐘線SCL保持高電平期間,數(shù)據(jù)線SDA被釋放,使得SDA返回高電平(即正跳變),稱為I2C總線的停止信號,它標(biāo)志著一次數(shù)據(jù)傳輸?shù)慕K止。

停止信號也是一種電平跳變時序信號,而不是一個電平信號,停止信號也是由主控器主動建立的,建立該信號之后,I2C總線將返回空閑狀態(tài)。

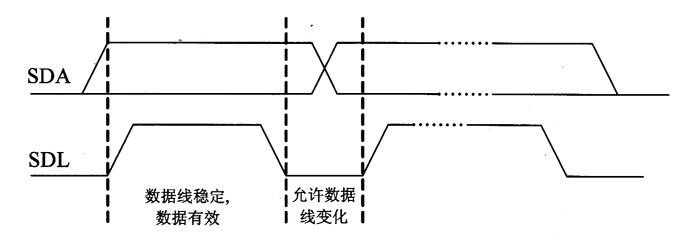

④數(shù)據(jù)位傳送。

在I2C總線上傳送的每一位數(shù)據(jù)都有一個時鐘脈沖相對應(yīng)(或同步控制),即在SCL串行時鐘的配合下,在SDA上逐位地串行傳送每一位數(shù)據(jù)。

進(jìn)行數(shù)據(jù)傳送時,在SCL呈現(xiàn)高電平期間,SDA上的電平必須保持穩(wěn)定,低電平為數(shù)據(jù)0,高電平為數(shù)據(jù)1。

只有在SCL為低電平期間,才允許SDA上的電平改變狀態(tài)。邏輯0的電平為低電壓,而邏輯1的電平取決于器件本身的正電源電壓VDD(當(dāng)使用獨(dú)立電源時),如圖2所示。

⑤應(yīng)答信號。

I2C總線上的所有數(shù)據(jù)都是以8位字節(jié)傳送的,發(fā)送器每發(fā)送一個字節(jié),就在時鐘脈沖9期間釋放數(shù)據(jù)線,由接收器反饋一個應(yīng)答信號。

應(yīng)答信號為低電平時,規(guī)定為有效應(yīng)答位(ACK簡稱應(yīng)答位),表示接收器已經(jīng)成功地接收了該字節(jié);應(yīng)答信號為高電平時,規(guī)定為非應(yīng)答位(NACK),一般表示接收器接收該字節(jié)沒有成功。

對于反饋有效應(yīng)答位ACK的要求是,接收器在第9個時鐘脈沖之前的低電平期間將SDA線拉低,并且確保在該時鐘的高電平期間為穩(wěn)定的低電平。

如果接收器是主控器,則在它收到最后一個字節(jié)后,發(fā)送一個NACK信號,以通知被控發(fā)送器結(jié)束數(shù)據(jù)發(fā)送,并釋放SDA線,以便主控接收器發(fā)送一個停止信號P,如圖3所示。

⑥插入等待時間。

如果被控器需要延遲下一個數(shù)據(jù)字節(jié)開始傳送的時間,則可以通過把時鐘線SCL電平拉低并且保持,使主控器進(jìn)入等待狀態(tài)。

一旦被控器釋放時鐘線,數(shù)據(jù)傳輸就得以繼續(xù)下去,這樣就使得被控器得到足夠時間轉(zhuǎn)移已經(jīng)收到的數(shù)據(jù)字節(jié),或者準(zhǔn)備好即將發(fā)送的數(shù)據(jù)字節(jié)。

帶有CPU的被控器在對收到的地址字節(jié)做出應(yīng)答之后,需要一定的時間去執(zhí)行中斷服務(wù)子程序,來分析或比較地址碼,其間就把SCL線鉗位在低電平上,直到處理妥當(dāng)后才釋放SCL線,進(jìn)而使主控器繼續(xù)后續(xù)數(shù)據(jù)字節(jié)的發(fā)送,如圖4所示。

⑦重啟動信號。

在主控器控制總線期間完成了一次數(shù)據(jù)通信(發(fā)送或接收)之后,如果想繼續(xù)占用總線再進(jìn)行一次數(shù)據(jù)通信(發(fā)送或接收),而又不釋放總線,就需要利用重啟動Sr信號時序。

重啟動信號Sr既作為前一次數(shù)據(jù)傳輸?shù)慕Y(jié)束,又作為后一次數(shù)據(jù)傳輸?shù)拈_始。利用重啟動信號的優(yōu)點(diǎn)是,在前后兩次通信之間主控器不需要釋放總線,這樣就不會丟失總線的控制權(quán),即不讓其他主器件節(jié)點(diǎn)搶占總線。

⑧時鐘同步。

如果在某一I2C總線系統(tǒng)中存在兩個主器件節(jié)點(diǎn),分別記為主器件1和主器件2,其時鐘輸出端分別為CLK1和CL【0,它們都有控制總線的能力。

假設(shè)在某一期間兩者相繼向SCL線發(fā)出了波形不同的時鐘脈沖序列CLK1和CLK2(時鐘脈沖的高、低電平寬度都是依靠各自內(nèi)部專用計數(shù)器定時產(chǎn)生的),在總線控制權(quán)還沒有裁定之前這種現(xiàn)象是可能出現(xiàn)的。

鑒于I2C總線的“線與”特性,使得時鐘線SCL上得到的時鐘信號波形,既不像主器件1所期望的CLK1,也不像主器件2所期望的CLK2,而是兩者進(jìn)行邏輯與的結(jié)果。

CLKI和CLK2的合成波形作為共同的同步時鐘信號,一旦總線控制權(quán)裁定給某一主器件,則總線時鐘信號將會只由該主器件產(chǎn)生,如圖5所示。

⑨總線沖突和總線仲裁。

假如在某I2C總線系統(tǒng)中存在兩個主器件節(jié)點(diǎn),分別記為主器件1和主器件2,其數(shù)據(jù)輸出端分別為DATA1和DATA2,它們都有控制總線的能力,這就存在著發(fā)生總線沖突(即寫沖突)的可能性。

假設(shè)在某一瞬間兩者相繼向總線發(fā)出了啟動信號,鑒于:I2C總線的“線與”特性,使得在數(shù)據(jù)線SDA上得到的信號波形是DATA1和DATA2兩者相與的結(jié)果,該結(jié)果略微超前送出低電平的主器件1,其DATA1的下降沿被當(dāng)做SDA的下降沿。

在總線被啟動后,主器件1企圖發(fā)送數(shù)據(jù)“101……”,主器件2企圖發(fā)送數(shù)據(jù)“100101……”。

兩個主器件在每次發(fā)出一個數(shù)據(jù)位的同時都要對自己輸出端的信號電平進(jìn)行抽檢,只要抽檢的結(jié)果與它們自己預(yù)期的電平相符,就會繼續(xù)占用總線,總線控制權(quán)也就得不到裁定結(jié)果。

主器件1的第3位期望發(fā)送“1”,也就是在第3個時鐘周期內(nèi)送出高電平。

在該時鐘周期的高電平期間,主器件1進(jìn)行例行抽檢時,結(jié)果檢測到一個不相匹配的電平“0”,這時主器件1只好決定放棄總線控制杈;因此,主器件2就成了總線的惟一主宰者,總線控制權(quán)也就最終得出了裁定結(jié)果,從而實(shí)現(xiàn)了總線仲裁的功能。

從以上總線仲裁的完成過程可以得出:仲裁過程主器件1和主器件2都不會丟失數(shù)據(jù);各個主器件沒有優(yōu)先級別之分,總線控制權(quán)是隨機(jī)裁定的,即使是搶先發(fā)送啟動信號的主器件1最終也并沒有得到控制杈。

系統(tǒng)實(shí)際上遵循的是“低電平優(yōu)先”的仲裁原則,將總線判給在數(shù)據(jù)線上先發(fā)送低電平的主器件,而其他發(fā)送高電平的主器件將失去總線控制權(quán),如圖6所示。

⑩總線封鎖狀態(tài)。

在特殊情況下,如果需要禁止所有發(fā)生在I2C總線上的通信活動,封鎖或關(guān)閉總線是一種可行途徑,只要掛接于該總線上的任意一個器件將時鐘線SCL鎖定在低電平上即可。

電子發(fā)燒友App

電子發(fā)燒友App

評論