SPI,是英語Serial Peripheral Interface的縮寫,顧名思義就是串行外圍設(shè)備接口。SPI,是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳,同時(shí)為PCB的布局上節(jié)省空間,提供方便,正是出于這種簡單易用的特性,現(xiàn)在越來越多的芯片集成了這種通信協(xié)議。

SPI是一個(gè)環(huán)形總線結(jié)構(gòu),由ss(cs)、sck、sdi、sdo構(gòu)成,其時(shí)序其實(shí)很簡單,主要是在sck的控制下,兩個(gè)雙向移位寄存器進(jìn)行數(shù)據(jù)交換。

上升沿發(fā)送、下降沿接收、高位先發(fā)送。

上升沿到來的時(shí)候,sdo上的電平將被發(fā)送到從設(shè)備的寄存器中。

下降沿到來的時(shí)候,sdi上的電平將被接收到主設(shè)備的寄存器中。

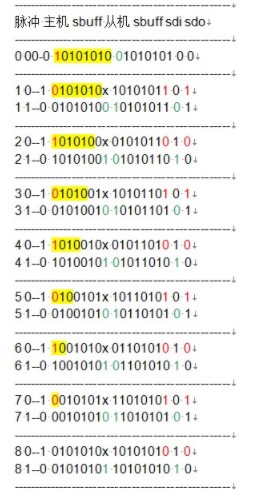

假設(shè)主機(jī)和從機(jī)初始化就緒:并且主機(jī)的sbuff=0xaa (10101010),從機(jī)的sbuff=0x55 (01010101),下面將分步對(duì)spi的8個(gè)時(shí)鐘周期的數(shù)據(jù)情況演示一遍(假設(shè)上升沿發(fā)送數(shù)據(jù))。

---------------------------------------------------

脈沖 主機(jī)sbuff 從機(jī)sbuff sdi sdo

---------------------------------------------------

0 00-0 10101010 01010101 0 0

---------------------------------------------------

1 0--1 0101010x 10101011 0 1

1 1--0 01010100 10101011 0 1

---------------------------------------------------

2 0--1 1010100x 01010110 1 0

2 1--0 10101001 01010110 1 0

---------------------------------------------------

3 0--1 0101001x 10101101 0 1

3 1--0 01010010 10101101 0 1

---------------------------------------------------

4 0--1 1010010x 01011010 1 0

4 1--0 10100101 01011010 1 0

---------------------------------------------------

5 0--1 0100101x 10110101 0 1

5 1--0 01001010 10110101 0 1

---------------------------------------------------

6 0--1 1001010x 01101010 1 0

6 1--0 10010101 01101010 1 0

---------------------------------------------------

7 0--1 0010101x 11010101 0 1

7 1--0 00101010 11010101 0 1

---------------------------------------------------

8 0--1 0101010x 10101010 1 0

8 1--0 01010101 10101010 1 0

---------------------------------------------------

這樣就完成了兩個(gè)寄存器8位的交換,上面的0--1表示上升沿、1--0表示下降沿,sdi、 sdo相對(duì)于主機(jī)而言的。根據(jù)以上分析,一個(gè)完整的傳送周期是16位,即兩個(gè)字節(jié),因?yàn)椋紫戎鳈C(jī)要發(fā)送命令過去,然后從機(jī)根據(jù)主機(jī)的名準(zhǔn)備數(shù)據(jù),主機(jī)在下一個(gè)8位時(shí)鐘周期才把數(shù)據(jù)讀回來。

SPI總線是Motorola公司推出的三線同步接口,同步串行3線方式進(jìn)行通信:一條時(shí)鐘線SCK,一條數(shù)據(jù)輸入線MOSI,一條數(shù)據(jù)輸出線MISO;用于 CPU與各種外圍器件進(jìn)行全雙工、同步串行通訊。

SPI主要特點(diǎn)有:可以同時(shí)發(fā)出和接收串行數(shù)據(jù);可以當(dāng)作主機(jī)或從機(jī)工作;提供頻率可編程時(shí)鐘;發(fā)送結(jié)束中斷標(biāo)志;寫沖突保護(hù);總線競爭保護(hù)等。

SPI總線有四種工作方式(SP0, SP1, SP2, SP3),其中使用的最為廣泛的是SPI0和SPI3方式。

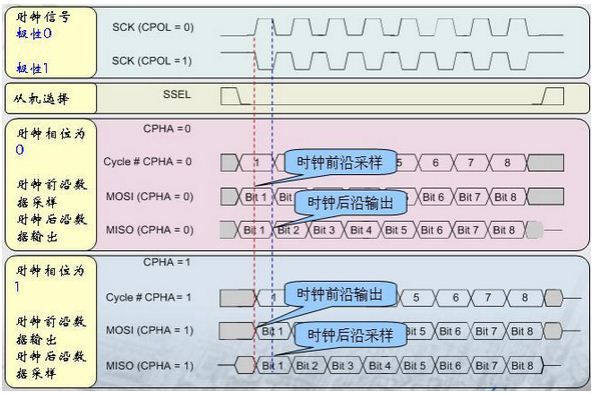

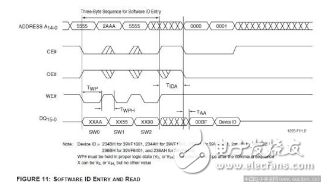

SPI模塊為了和外設(shè)進(jìn)行數(shù)據(jù)交換,根據(jù)外設(shè)工作要求,其輸出串行同步時(shí)鐘極性和相位可以進(jìn)行配置,時(shí)鐘極性(CPOL)對(duì)傳輸協(xié)議沒有重大的影響。如果CPOL=0,串行同步時(shí)鐘的空閑狀態(tài)為低電平;如果CPOL=1,串行同步時(shí)鐘的空閑狀態(tài)為高電平。時(shí)鐘相位(CPHA)能夠配置用于選擇兩種不同的傳輸協(xié)議之一進(jìn)行數(shù)據(jù)傳輸。如果 CPHA=0,在串行同步時(shí)鐘的第一個(gè)跳變沿(上升或下降)數(shù)據(jù)被采樣;如果CPHA=1,在串行同步時(shí)鐘的第二個(gè)跳變沿(上升或下降)數(shù)據(jù)被采樣。 SPI主模塊和與之通信的外設(shè)音時(shí)鐘相位和極性應(yīng)該一致。

SPI時(shí)序圖詳解-SPI接口在模式0下輸出第一位數(shù)據(jù)的時(shí)刻

SPI接口在模式0下輸出第一位數(shù)據(jù)的時(shí)刻

SPI接口有四種不同的數(shù)據(jù)傳輸時(shí)序,取決于CPOL和CPHL這兩位的組合。圖1中表現(xiàn)了這四種時(shí)序,

時(shí)序與CPOL、CPHL的關(guān)系也可以從圖中看出。

圖1

CPOL是用來決定SCK時(shí)鐘信號(hào)空閑時(shí)的電平,CPOL=0,空閑電平為低電平,CPOL=1時(shí),

空閑電平為高電平。CPHA是用來決定采樣時(shí)刻的,CPHA=0,在每個(gè)周期的第一個(gè)時(shí)鐘沿采樣,

CPHA=1,在每個(gè)周期的第二個(gè)時(shí)鐘沿采樣。

由于我使用的器件工作在模式0這種時(shí)序(CPOL=0,CPHA=0),所以將圖1簡化為圖2,

只關(guān)注模式0的時(shí)序。

圖2

我們來關(guān)注SCK的第一個(gè)時(shí)鐘周期,在時(shí)鐘的前沿采樣數(shù)據(jù)(上升沿,第一個(gè)時(shí)鐘沿),

在時(shí)鐘的后沿輸出數(shù)據(jù)(下降沿,第二個(gè)時(shí)鐘沿)。首先來看主器件,主器件的輸出口(MOSI)輸出的數(shù)據(jù)bit1,

在時(shí)鐘的前沿被從器件采樣,那主器件是在何時(shí)刻輸出bit1的呢?bit1的輸出時(shí)刻實(shí)際上在SCK信號(hào)有效以前,

比 SCK的上升沿還要早半個(gè)時(shí)鐘周期。bit1的輸出時(shí)刻與SSEL信號(hào)沒有關(guān)系。再來看從器件,

主器件的輸入口MISO同樣是在時(shí)鐘的前沿采樣從器件輸出的bit1的,那從器件又是在何時(shí)刻輸出bit1的呢。

從器件是在SSEL信號(hào)有效后,立即輸出bit1,盡管此時(shí)SCK信號(hào)還沒有起效。關(guān)于上面的主器件

和從器件輸出bit1位的時(shí)刻,可以從圖3、4中得到驗(yàn)證。

圖3

注意圖3中,CS信號(hào)有效后(低電平有效,注意CS下降沿后發(fā)生的情況),故意用延時(shí)程序

延時(shí)了一段時(shí)間,之后再向數(shù)據(jù)寄存器寫入了要發(fā)送的數(shù)據(jù),來觀察主器件輸出bit1的情況(MOSI)。

可以看出,bit1(值為1)是在SCK信號(hào)有效之前的半個(gè)時(shí)鐘周期的時(shí)刻開始輸出的(與CS信號(hào)無關(guān)),

到了SCK的第一個(gè)時(shí)鐘周期的上升沿正好被從器件采樣。

圖4

圖4中,注意看CS和MISO信號(hào)。我們可以看出,CS信號(hào)有效后,從器件立刻輸出了bit1(值為1)。

通常我們進(jìn)行的spi操作都是16位的。圖5記錄了第一個(gè)字節(jié)和第二個(gè)字節(jié)間的相互銜接的過程。

第一個(gè)字節(jié)的最后一位在SCK的上升沿被采樣,隨后的SCK下降沿,從器件就輸出了第二個(gè)字節(jié)的第一位。

SPI總線協(xié)議介紹(接口定義,傳輸時(shí)序)

一、技術(shù)性能

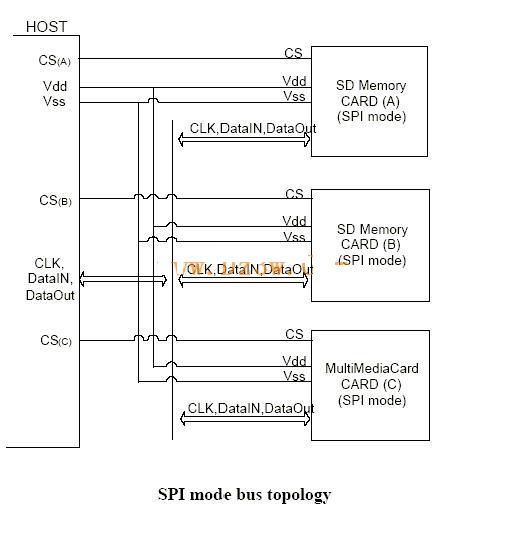

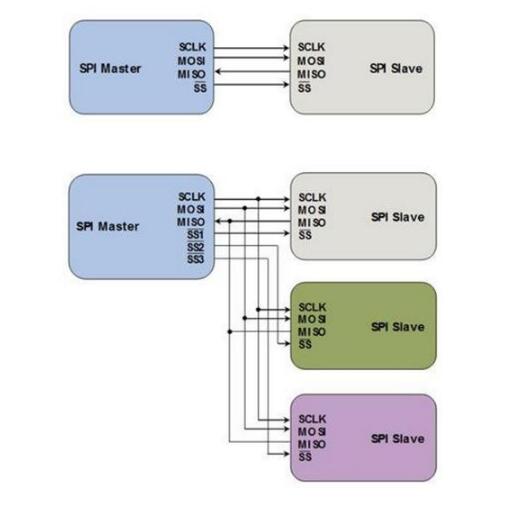

SPI接口是Motorola 首先提出的全雙工三線同步串行外圍接口,采用主從模式(Master Slave)架構(gòu);支持多slave模式應(yīng)用,一般僅支持單Master。

時(shí)鐘由Master控制,在時(shí)鐘移位脈沖下,數(shù)據(jù)按位傳輸,高位在前,低位在后(MSB first);SPI接口有2根單向數(shù)據(jù)線,為全雙工通信,目前應(yīng)用中的數(shù)據(jù)速率可達(dá)幾Mbps的水平。

-------------------------------------------------------

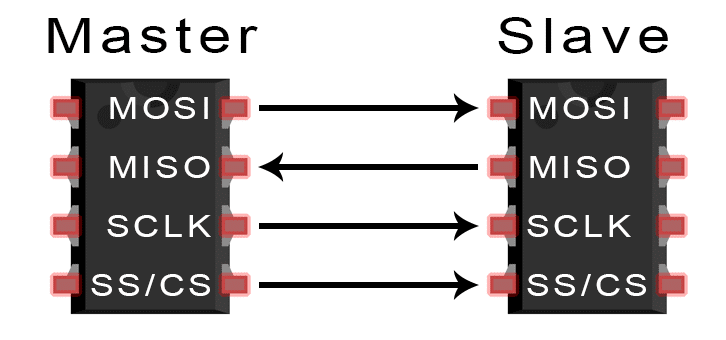

二、接口定義

SPI接口共有4根信號(hào)線,分別是:設(shè)備選擇線、時(shí)鐘線、串行輸出數(shù)據(jù)線、串行輸入數(shù)據(jù)線。

(1)MOSI:主器件數(shù)據(jù)輸出,從器件數(shù)據(jù)輸入

(2)MISO:主器件數(shù)據(jù)輸入,從器件數(shù)據(jù)輸出

(3)SCLK :時(shí)鐘信號(hào),由主器件產(chǎn)生

(4)/SS:從器件使能信號(hào),由主器件控制

-------------------------------------------------------

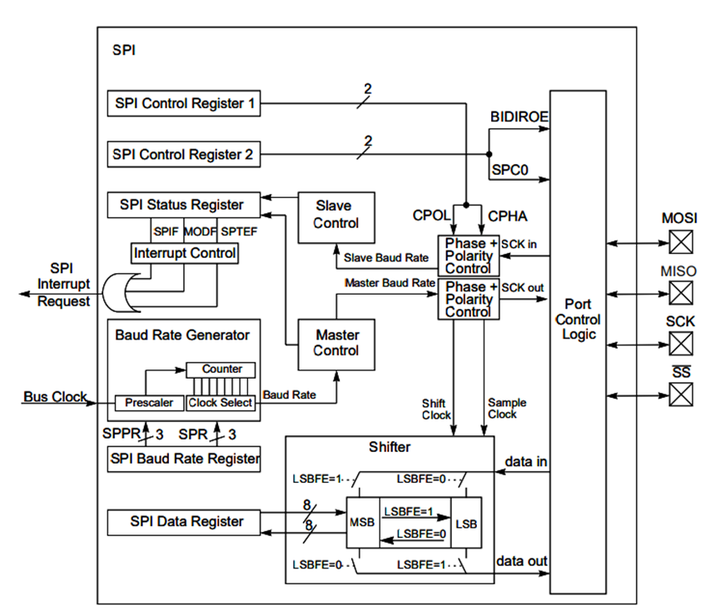

三、內(nèi)部結(jié)構(gòu)

四、傳輸時(shí)序

SPI接口在內(nèi)部硬件實(shí)際上是兩個(gè)簡單的移位寄存器,傳輸?shù)臄?shù)據(jù)為8位,在主器件產(chǎn)生的從器件使能信號(hào)和移位脈沖下,按位傳輸,高位在前,低位在后。如下圖所示,在SCLK的下降沿上數(shù)據(jù)改變,上升沿一位數(shù)據(jù)被存入移位寄存器。

SPI接口沒有指定的流控制,沒有應(yīng)答機(jī)制確認(rèn)是否接收到數(shù)據(jù)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論