ARM720T是一款通用的32位微處理器,具有8KB的高速緩存、擴大的寫入緩沖區(qū)和內(nèi)存管理單元(MMU),組合在一個芯片中。ARM720T中的CPU是ARM7TDMI。ARM720T是與ARM處理器

2023-08-02 11:36:56

性能--ARM調(diào)試架構(gòu),額外支持實時調(diào)試。這使關(guān)鍵異常處理程序能夠在調(diào)試系統(tǒng)時執(zhí)行。

?支持外部緊密耦合存儲器(TCM)。為每個外部指令和數(shù)據(jù)存儲器塊提供TCM接口。指令和數(shù)據(jù)TCM塊的大小都是特定于實現(xiàn)者的,可以在0KB到1MB之間

2023-08-02 10:17:36

PrimeCell DC-DC轉(zhuǎn)換器接口是由ARM開發(fā)、測試和許可的符合高級微控制器總線架構(gòu)(AMBA)的片上系統(tǒng)外圍設(shè)備。

PrimeCell DC-DC轉(zhuǎn)換器接口是一個AMBA從模塊,連接到高級

2023-08-02 11:14:26

(AXI),用于支持優(yōu)先級的二級接口

多處理器實現(xiàn)

?九級管道

?帶返回堆棧的分支預(yù)測

?低中斷延遲

?外部協(xié)處理器接口和協(xié)處理器CP14和CP15

?可選的指令和數(shù)據(jù)存儲器保護單元(MPU)

?可選的指令

2023-08-02 09:15:45

高速緩存體系結(jié)構(gòu)處理器,適用于全內(nèi)存管理、高性能和低功耗至關(guān)重要的多程序應(yīng)用。此設(shè)計中的獨立指令和數(shù)據(jù)緩存大小分別為16KB,具有8字線長度。ARM920T處理器實現(xiàn)了一個增強的ARM架構(gòu)v4-MMU,為

2023-08-02 13:05:00

CPU。16KB指令與 16KB 數(shù)據(jù)緩存。指令與數(shù)據(jù)存儲器管理單元(MMU)。寫緩沖器。高級微處理器總線架構(gòu)(AMBA)總線接口。ETM(內(nèi)置追蹤宏單元)接口。 ARM920T中的ARM

2019-09-26 09:43:55

ARM966E-S是一個可合成的宏單元,將ARM處理器與緊密耦合的SRAM存儲器相結(jié)合。它是ARM9 Thumb系列高性能32位片上系統(tǒng)(SoC)處理器解決方案的一員,面向廣泛的嵌入式應(yīng)用,在這

2023-08-02 07:46:42

ARM9E 系列微處理器的主要特點如下。支持 DSP 指令集,適合于需要高速數(shù)字信號處理的場合。5級流水線,指令執(zhí)行效率更高。 支持 32 位 ARM 指令集和 16 位 Thumb 指令集。支持

2019-09-26 09:36:52

ARM處理器中斷處理的編程是怎么實現(xiàn)的?

2021-04-27 06:46:53

。ARM處理器模式ARM微處理器支持7種運行模式,分別為:用戶模式(usr):ARM處理器正常的程序執(zhí)行狀態(tài)。快速中斷模式(fiq):用于高速數(shù)據(jù)傳輸或通道處理。外部中斷模式(irq):用于通用的中斷

2011-01-27 11:13:20

。ARM處理器模式ARM微處理器支持7種運行模式,分別為:用戶模式(usr):ARM處理器正常的程序執(zhí)行狀態(tài)。快速中斷模式(fiq):用于高速數(shù)據(jù)傳輸或通道處理。外部中斷模式(irq):用于通用的中斷

2011-01-27 14:19:05

(32位)數(shù)據(jù),從第四個字節(jié)到第七個字節(jié)放置第二個存儲的字?jǐn)?shù)據(jù),一次排列。作為32位的微處理器,arm體系結(jié)構(gòu)所支持的最大尋址空間為4GB。存儲器格式1、大端格式:高字節(jié)在低地址,低字節(jié)在高地址;2、小端

2017-11-06 10:43:47

32位的微處理器,arm體系結(jié)構(gòu)所支持的最大尋址空間為4GB。存儲器格式1、大端格式:高字節(jié)在低地址,低字節(jié)在高地址;2、小端格式:高字節(jié)在高地址,低字節(jié)在低地址。指令長度Arm微處理器的指令長度是32位

2017-10-12 11:30:08

32位的微處理器,arm體系結(jié)構(gòu)所支持的最大尋址空間為4GB。 存儲器格式1、大端格式:高字節(jié)在低地址,低字節(jié)在高地址;2、小端格式:高字節(jié)在高地址,低字節(jié)在低地址。 指令長度Arm微處理器的指令長度

2017-10-25 16:55:35

。ARM復(fù)位后PC無條件的指向0x00000000處。MMU是ARM處理器的內(nèi)存管理單元,CPU管理虛擬存儲器、物理存儲器的控制線路,同時負(fù)責(zé)虛擬地址映射為物理地址,以及提供硬件機制的內(nèi)存訪問授權(quán);進行虛擬地址到物理地址的轉(zhuǎn)換通過查找頁表來完成,每次在訪問內(nèi)存時先查TLB,查不到再到內(nèi)存中查整個頁表。.

2021-12-21 07:16:24

ARM處理器模式和ARM處理器狀態(tài)有何區(qū)別?

2022-11-01 15:15:13

處理器內(nèi)核二、經(jīng)典ARM處理器編程模型三、Cortex-M4處理器四、STM32F407芯片簡潔一、ARM處理器特點1.ARM處理器主要特點(1)ARM7系列采用馮諾依曼結(jié)構(gòu)(輸入輸出、控制器、存儲器、處理器),ARM9~11采用哈佛體系結(jié)構(gòu)(存儲器分為程序存儲器和數(shù)據(jù)存儲器)(2)屬于RISC型處理器結(jié)

2021-12-13 07:18:29

。因此在介紹ARM之前,需要對RISC體系結(jié)構(gòu)、組織結(jié)構(gòu)是基本情況進行全面介紹。1. RISC體系結(jié)構(gòu)計算機體系結(jié)構(gòu)描述:從用戶角度看到的計算機屬性,如計算機的指令集、可見寄存器、存儲器管理單元和異常處理

2022-04-24 09:57:10

時的實現(xiàn)工藝。容易實現(xiàn)高性能。RISC體系結(jié)構(gòu)的簡單性、有效性很容易設(shè)計出低成本、高性能的處理器。RISC技術(shù)的歷史貢獻在計算機設(shè)計技術(shù)的發(fā)展變化中,20世紀(jì)60年代初引入的虛擬存儲器、Cache和流水線

2022-04-24 10:02:29

。作為 32 位的微處理器,ARM920T 體系結(jié)構(gòu)所支持的最大尋址空間位 4GB(232字節(jié)) 。ARM920T 體系結(jié)構(gòu)支持兩種方法存儲字?jǐn)?shù)據(jù),即大端(Big Enddian)格式和小端

2019-09-27 09:37:35

2.ARM微處理器的指令系統(tǒng)ARM微處理器的指令集是加載/存儲型的,即指令集僅能處理寄存器中的數(shù)據(jù),而且處理結(jié)果都要放回寄存器中,而對系統(tǒng)存儲器的訪問則需要通過專門的加載/存儲指令來完成。ARM

2021-12-20 06:54:28

慕課電子科技大學(xué).嵌入式系統(tǒng).第三章.ARM微處理器編程基礎(chǔ)和接口實驗.ARM微處理器編程基礎(chǔ)實驗0 目錄3 ARM微處理器編程基礎(chǔ)和接口實驗3.1 ARM微處理器編程基礎(chǔ)實驗3.1.1課堂重點

2021-12-14 09:04:05

慕課電子科技大學(xué).嵌入式系統(tǒng).第三章.ARM微處理器編程基礎(chǔ)和接口實驗.ARM設(shè)備接口實驗0 目錄3 ARM微處理器編程基礎(chǔ)和接口實驗3.2 ARM設(shè)備接口實驗3.2.1課堂重點3.2.2測試與作業(yè)

2021-12-14 08:46:10

[table][tr][td=670][table][tr][td]arm處理器本身所產(chǎn)生的地址為虛擬地址,每一個arm芯片內(nèi)都有存儲器,而這個芯片內(nèi)的存儲器的地址為物理地址。我們寫程序的目的是為了

2014-03-24 11:57:18

各位大神,小菜需要一款主頻在600MHZ以上的,帶有PWM,和AD轉(zhuǎn)換的ARM處理器,用作運動控制的。

2014-04-13 09:58:18

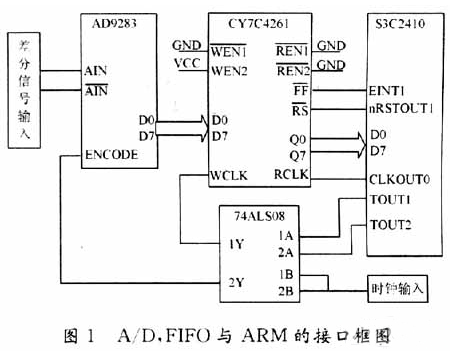

FIFO存儲器是系統(tǒng)的緩沖環(huán)節(jié),如果沒有FIFO存儲器,整個系統(tǒng)就不可能正常工作,它主要有幾方面的功能:1)對連續(xù)的數(shù)據(jù)流進行緩存,防止在進機和存儲操作時丟失數(shù)據(jù);2)數(shù)據(jù)集中起來進行進棧和存儲,可

2022-01-18 10:03:06

第一套在8086的微計算機系統(tǒng)中,存儲器是如何組織的?是如何與處理器總線連接的?#BHE信號起什么作用?答:8086 為 16 位處理器,可訪問 1M 字節(jié)的存儲器空間;1M 字節(jié)的存儲器分為兩個

2021-07-26 06:06:49

PXA255處理器開發(fā)諸如車載導(dǎo)航系統(tǒng)時,電子地圖等海量地理信息數(shù)據(jù)需要一個容量大、體積小、性能優(yōu)異的存儲器。“Compact Flash”卡,簡稱CF卡,具有高速度、大容量、體積小、重量輕、功耗低

2019-04-08 09:36:20

描述此參考設(shè)計面向目前使用 FPGA 或 ASIC 將高速數(shù)據(jù)轉(zhuǎn)換器連接到基帶處理器的寬帶接收器系統(tǒng)開發(fā)人員,他們需要縮短產(chǎn)品上市時間,同時增強性能并大大降低成本、功率和尺寸。此參考設(shè)計包括首個廣泛

2018-09-20 09:07:06

高速模/數(shù)轉(zhuǎn)換器AD10242的功能特點與應(yīng)用有哪些?如何實現(xiàn)AD10242與DSP進行接口連接?

2021-04-14 06:36:19

高速硬盤存儲設(shè)備實現(xiàn)數(shù)據(jù)的持續(xù)高速存儲,要求處理數(shù)據(jù)的速度高。通常這些需要傳輸和處理大量數(shù)據(jù)的設(shè)備均選用數(shù)字信號處理器DSP作為微處理器。同時,SCSI協(xié)議中許多復(fù)雜的控制功能也需要這個微處理器來實現(xiàn)

2011-06-02 09:33:21

本章節(jié)介紹了 Cyclone? IV 器件的存儲器接口管腳的支持以及外部存儲器接口的特性。除了大量供應(yīng)的片上存儲器,Cyclone IV 器件可以很容易地與各種外部存儲器件建立連接,其中包括

2017-11-14 10:12:11

了設(shè)計的一大挑戰(zhàn)。FPGA可通過在單個FPGA中實現(xiàn)多個視頻處理器來提供強大的處理能力。那么現(xiàn)在的挑戰(zhàn)就變成了要使數(shù)據(jù)盡快且高效地從FPGA進出。DDR3存儲器系統(tǒng)在大多數(shù)情況下可以為這些基于FPGA的系統(tǒng)

2019-05-24 05:00:34

FPGA實現(xiàn)高速FFT處理器的設(shè)計介紹了采用Xilinx公司的Virtex - II系列FPGA設(shè)計高速FFT處理器的實現(xiàn)方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復(fù)雜邏輯,采用

2012-08-12 11:49:01

為了滿足智能手機功能日益提高的數(shù)據(jù)需求,現(xiàn)代數(shù)字移動通信系統(tǒng)的基礎(chǔ)設(shè)施必須持續(xù)發(fā)展以支持更寬的帶寬和更快的數(shù)據(jù)轉(zhuǎn)換。為實現(xiàn)高速的數(shù)據(jù)速率,數(shù)字轉(zhuǎn)換器中的數(shù)字中頻處理、包括DDC(數(shù)字下變頻器

2019-08-01 07:26:17

緩存,而 SL3另外還可在局域 L2 高速緩存中進行緩存。 為向軟件執(zhí)行提供快速通道,外部存儲器同內(nèi)部共享存儲器一樣,通過同一存儲器控制器進行連接,而并非像在嵌入式處理器架構(gòu)上所進行的傳統(tǒng)做法那樣

2011-08-13 15:45:42

存儲器訪問權(quán)限控制Cache通過MMU的訪存MMU會先查找TLB中的虛擬地址表如果TLB中沒有虛擬地址的入口,硬件從主存儲器中的轉(zhuǎn)換表中獲取轉(zhuǎn)換與訪問權(quán)限。ARM的MMU訪存原理ARM的MMU頁表格

2022-06-13 16:41:04

ARM7TDMI處理器內(nèi)核,為用戶提供了面向移動終端應(yīng)用的豐富外設(shè)、低功耗管理和低成本的外存配置,整個芯片可以運行在75 MHz。數(shù)據(jù)通信系統(tǒng)使用的主要功能模塊如下:20 KB片上零等待靜態(tài)存儲器

2019-04-26 07:00:06

和存儲。FPGA將一組數(shù)據(jù)處理完畢后,以中斷的方式通知SEP3203,處理器以DMA方式將運算后的結(jié)果存儲到片外的SDRAM中。由于數(shù)據(jù)寫滿FIFO的時間大于FPGA處理數(shù)據(jù)的時間,所以整個系統(tǒng)實現(xiàn)了

2018-12-05 10:13:09

了PowerPC、集成的APU控制器以及一個與之相連的協(xié)處理器。來自高速緩存或存儲器中的指令可以立即出現(xiàn)在CPU解碼器和APU控制器上,如果CPU能識別指令,則運行這些指令。否則,APU控制器或用

2015-02-02 14:18:19

計算機指令以及處理計算機軟件中的數(shù)據(jù)。中央處理器主要包括運算器(算術(shù)邏輯運算單元,ALU,Arithmetic Logic Unit)和高速緩沖存儲器(Cache)及實現(xiàn)它們之間聯(lián)系的數(shù)據(jù)(Dat...

2022-02-10 08:00:15

串行外圍設(shè)備接口SPI(serial peripheral interface)總線技術(shù)是Motorola公司推出的一種同步串行接口,它允許CPU與TTL移位寄存器、A/D或D/A轉(zhuǎn)換器、實時時鐘(RTO)、存儲器以及LCD和LED顯示驅(qū)動器等外圍接口器件以串行方式進行通訊。

2019-07-12 06:33:07

ARM處理器本身是32位設(shè)計,但也配備16位指令集。一般來講存儲器比等價32位代碼節(jié)省達35%,然而保留了32位系統(tǒng)的所有優(yōu)勢。

2019-11-11 06:48:04

戶模式進入系統(tǒng)模式。ARM 處理器是一個綜合體,ARM 公司自身并不制造微處理器。它們是由 ARM 的合作 伙伴(Intel 或 LSI)制造。ARM 還允許將其處理器通過協(xié)處理器接口進行緊耦合。它還

2019-09-24 17:47:38

高速轉(zhuǎn)換器是什么

2021-03-04 07:26:53

關(guān)于高速存儲器的調(diào)試和評估,看完你就懂了

2021-05-11 06:28:25

關(guān)于數(shù)Gpbs高速存儲器接口設(shè)計的分析,看完你就懂了

2021-05-19 06:38:12

描述此參考設(shè)計介紹高可靠性應(yīng)用(基于 66AK2Gx 多內(nèi)核 DSP + ARM 處理器片上系統(tǒng) (SoC))中具有糾錯碼 (ECC) 支持的雙倍數(shù)據(jù)速率 (DDR) 存儲器接口的系統(tǒng)注意事項。其中

2022-09-15 06:26:24

微處理器送往存儲器和I/O接口電路的,如讀/寫信號,片選信號、中斷響應(yīng)信號等;也有是其它部件反饋給CPU的,比如:中斷申請信號、復(fù)位信號、總線請求信號、限備就緒信號等。控制總線的具體情況取決于CPU。三

2022-08-17 15:20:52

的,因此,還應(yīng)將微處理器的一些必要引腳用接口插座引出,方便實驗開發(fā)使用。下面將以模塊為單元介紹典型的需要引出的引腳,并給出相應(yīng)電路的選型。3.2.1 FLASH存儲器模塊所需引腳為ADDR[21:0

2011-11-25 10:03:34

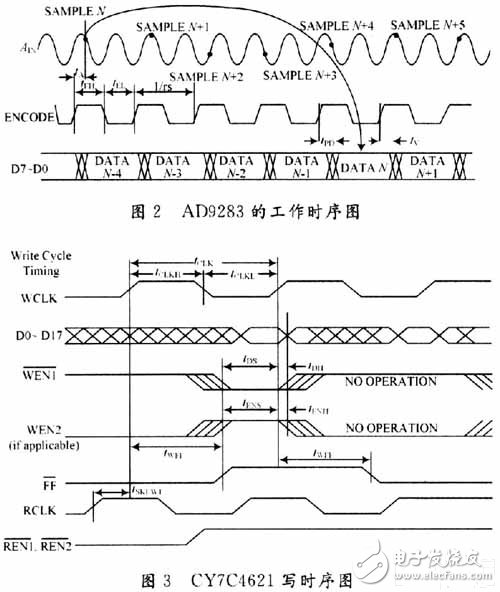

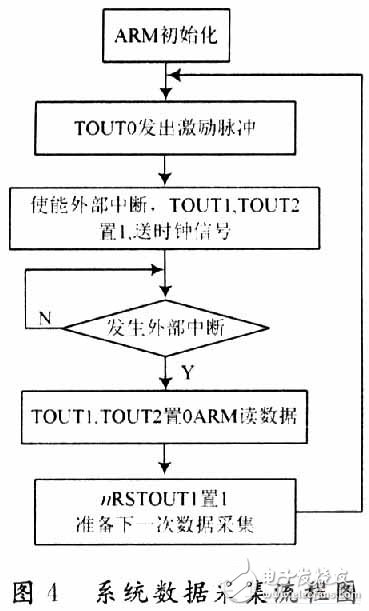

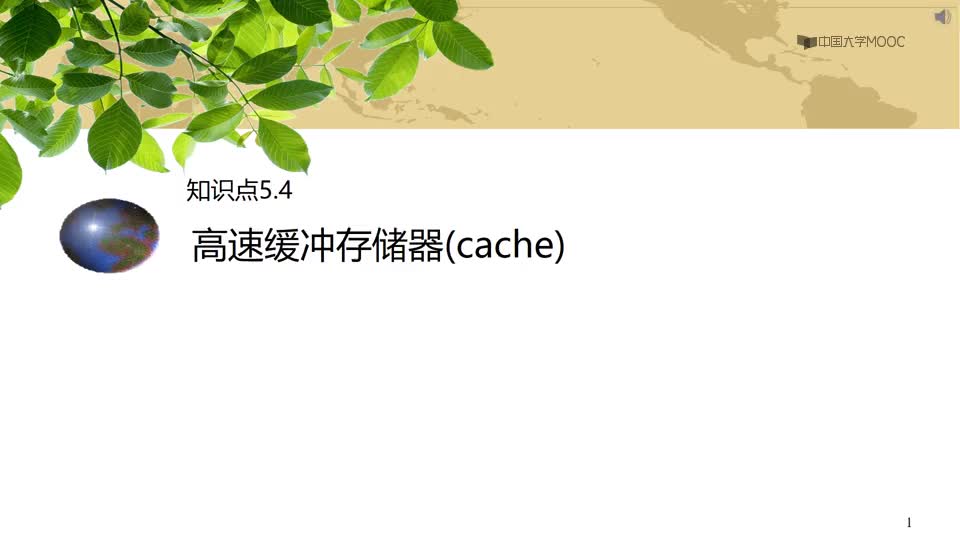

在高頻超聲波數(shù)據(jù)采集系統(tǒng)中,很多高速A/D轉(zhuǎn)換器往往不能直接與處理器相連接,這時就需要使用FIFO在處理器與A/D轉(zhuǎn)換器之間架一座橋梁,FIFO的先入先出特性可以方便緩存大量的數(shù)據(jù)塊。在基于ARM

2020-12-28 06:55:06

了設(shè)計的一大挑戰(zhàn)。FPGA可通過在單個FPGA中實現(xiàn)多個視頻處理器來提供強大的處理能力。那么現(xiàn)在的挑戰(zhàn)就變成了要使數(shù)據(jù)盡快且高效地從FPGA進出。DDR3存儲器系統(tǒng)在大多數(shù)情況下可以為這些基于FPGA的系統(tǒng)

2019-05-27 05:00:02

。在結(jié)構(gòu)上的改進主要包括可變寬度的存儲器接口、更快速的指令周期時間、可設(shè)置優(yōu)先級的雙通道DMA處理器、靈活的引導(dǎo)程序裝入方式、可重新定位的中斷向量表以及可選的邊緣/電平觸發(fā)中斷方式等。 1

2019-06-14 05:00:08

FIFO、緊耦合存儲器及16位的SRAM集成在SOPC系統(tǒng)中,并在FPGA開發(fā)板上實現(xiàn)的方法,其內(nèi)容包括外設(shè)的接入方法,以及緊耦合存儲器如何通過緊耦合從端口直接與處理器的緊耦合數(shù)據(jù)/指令主端口相連等

2018-12-07 10:27:46

基于Proteus的Arm處理器的SPI接口實現(xiàn)

2010-02-10 10:41:58

處理器供電的理想選擇。對相位的增加或遮蔽能力可在寬范圍的負(fù)載條件下實現(xiàn)高效率。LP8758 就是業(yè)內(nèi)最先進多相位轉(zhuǎn)換器的最好示例,它是手機處理器電源的理想選擇。它具有低IQ,小總體解決方案尺寸,16A

2018-09-06 15:55:29

一、什么是CacheCache是一種容量比較小,但訪問速度比較快存儲器。由于處理器的速度遠(yuǎn)高于主存,處理器直接從內(nèi)存中存取數(shù)據(jù)要等待一定周期,而Cache位于處理器與主存之間,保存著最近一段時間

2016-08-31 16:30:26

如何實現(xiàn)擴展存儲器的設(shè)計?

2021-10-28 08:08:51

本文介紹了使用XCR3032實現(xiàn)K9K1G08U0M與微控制器的接口原理,給出了VerilogHD L實現(xiàn)程序。對大容量FLASH存儲器的接口設(shè)計具有一定的參考價值。

2021-04-29 06:34:20

如何利用Xilinx FPGA和存儲器接口生成器簡化存儲器接口?

2021-05-06 07:23:59

DDR3存儲器控制器面臨的挑戰(zhàn)有哪些?如何用一個特定的FPGA系列LatticeECP3實現(xiàn)DDR3存儲器控制器。

2021-04-30 07:26:55

什么是I2C總線?一種基于I2C總線的AT24存儲器數(shù)據(jù)串并轉(zhuǎn)換接口的VHDL設(shè)計

2021-05-27 06:55:42

的工作時鐘頻率。然而,設(shè)計至DDR3的接口也變得更具挑戰(zhàn)性。在FPGA中實現(xiàn)高速、高效率的DDR3控制器是一項艱巨的任務(wù)。直到最近,只有少數(shù)高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

如何用低成本FPGA解決高速存儲器接口挑戰(zhàn)?

2021-04-29 06:59:22

我喜歡使用verilog,vivado2017.1設(shè)計處理器(MIPS32),設(shè)備是Virtex7 vc707。我已經(jīng)使用BRAM作為主存儲器(.coe文件的init指令)在FPGA(Virtex7

2020-08-25 13:19:36

本文采用SoPC內(nèi)嵌32位的軟核處理器Nios,實現(xiàn)了一個UART串行口和以太網(wǎng)接口的轉(zhuǎn)換器(以下簡稱轉(zhuǎn)換器),并基于Microtronix公司針對Nios處理器移植的μClinux開發(fā)了應(yīng)用程序。

2021-04-25 06:17:46

困難,因此高性能的ARM協(xié)處理器接口僅限于片上使用。最常使用的協(xié)處理器是用于控制片上功能的系統(tǒng)協(xié)處理器,例如控制ARM720上的高速緩存Cache和存儲器管理單元MMU等。ARM也開發(fā)了浮點協(xié)處理器

2022-04-24 09:36:47

本文講述了一種基于ARM7處理器實現(xiàn)USB接口與CAN總線的實例,通過其可以在PC實現(xiàn)對CAN總線上設(shè)備的監(jiān)控。

2021-05-21 06:58:17

如何滿足各種讀取數(shù)據(jù)捕捉需求以實現(xiàn)高速接口?怎么縮短高端存儲器接口設(shè)計?

2021-04-29 07:00:08

描述此參考設(shè)計介紹高可靠性應(yīng)用(基于 66AK2Gx 多內(nèi)核 DSP + ARM 處理器片上系統(tǒng) (SoC))中具有糾錯碼 (ECC) 支持的雙倍數(shù)據(jù)速率 (DDR) 存儲器接口的系統(tǒng)注意事項。其中

2018-10-22 10:20:57

模數(shù)轉(zhuǎn)換器(Analog To Digital Converter)簡稱ADC(也可以寫成A/D),是指將連續(xù)變化的模擬信號轉(zhuǎn)換為離散的數(shù)字信號的器件。 直接存儲器存取技術(shù)(Direct

2022-02-07 08:29:11

協(xié)議用于維護由于多個處理器共享數(shù)據(jù)引發(fā)的多處理器數(shù)據(jù)一致性問題。論述了一個適用于64位多核處理器的共享緩存設(shè)計,包括如何實現(xiàn)多處理器緩存一致性及其全定制后端實現(xiàn)。本文介紹了一種共享高速存儲器模塊

2021-02-23 07:12:38

本文設(shè)計了一種在多處理器系統(tǒng)中的Nios II軟核處理器的啟動方案,這個方案在外部處理器向Nios II的程序存儲器和數(shù)據(jù)存儲器加載數(shù)據(jù)時,可以控制Nios II處理器的啟動。

2021-04-27 06:52:42

數(shù)據(jù)存儲器 FLASH程序存儲器 FLASH數(shù)據(jù)存儲器 片內(nèi)RAM數(shù)據(jù)存儲器16M字節(jié)外部數(shù)據(jù)存儲器各有什么區(qū)別?特點?小弟看到這段 很暈。ADuC812的用戶數(shù)據(jù)存儲器包含三部分,片內(nèi)640字節(jié)的FLASH數(shù)據(jù)存儲器、256字節(jié)的RAM以及片外可擴展到16M字節(jié)的數(shù)據(jù)存儲器。求助高手。解釋一下不同。

2011-11-29 09:50:46

STM32F103處理器內(nèi)部存儲器結(jié)構(gòu)及映射???STM32F103存儲器映像為預(yù)定義形式,嚴(yán)格規(guī)定了哪個位置使用哪條總線。???STM32F103的程序存儲器、數(shù)據(jù)存儲器、寄存器和IO端口被組織到

2021-12-09 07:51:09

用于高速數(shù)據(jù)轉(zhuǎn)換器的串行接口有哪些選擇?

2021-04-09 06:55:28

解碼器需要一個恒速的傳輸流)。雖然存儲器對同步的要求似乎很小,但當(dāng)涉及到多個碼流時它可能很顯著。這種同步可以由一個異步FIFO實現(xiàn)。 2) 幀存儲: 幀存儲在這些地方需要:任何暫時的處理如幀率轉(zhuǎn)換

2011-07-15 09:18:00

如何滿足各種讀取數(shù)據(jù)捕捉需求以實現(xiàn)高速接口?如何讓接收到的時鐘與數(shù)據(jù)中心對準(zhǔn)?為了縮短設(shè)計周期應(yīng)遵循哪些規(guī)則?如何設(shè)計存儲器接口才能獲得更高性能?

2021-04-14 06:30:23

40kB 的片內(nèi)SRAM、512kB 嵌入的高速Flash 存儲器,128 位寬度的存儲器接口和獨特的加速結(jié)構(gòu)使32 位代碼能夠在最大時鐘速率下運行, 為通信網(wǎng)關(guān)、協(xié)議轉(zhuǎn)換器、軟件modem、語音識別

2019-06-04 05:00:15

In First Out)存儲器憑借其操作簡單、可靠性好等特點,被廣泛的應(yīng)用于數(shù)據(jù)采集系統(tǒng)中,成為了連接MCU與AD芯片的橋梁。為了使MCU、AD芯片以及高速FIFO存儲器能夠協(xié)調(diào)工作,就需要設(shè)計好這

2019-05-23 05:01:08

。在結(jié)構(gòu)上的改進主要包括可變寬度的存儲器接口、更快速的指令周期時間、可設(shè)置優(yōu)先級的雙通道DMA處理器、靈活的引導(dǎo)程序裝入方式、可重新定位的中斷向量表以及可選的邊緣/電平觸發(fā)中斷方式等。 1

2019-06-12 05:00:08

如何使用Arm-2D在小資源Cortex-M處理器芯片中實現(xiàn)圖形界面,非arm cortex處理器能用Arm-2D嗎?

2022-08-04 14:14:51

設(shè)計AD7574 A D轉(zhuǎn)換器與微處理器的接口(該接口用作存儲器映像輸入設(shè)備) :

2009-06-12 14:21:32 52

52 FPGA設(shè)計的高速FIFO電路技術(shù)

本文主要介紹高速FIFO電路在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用,相關(guān)電路主要有高速A/D轉(zhuǎn)換器、FPGA、SDRAM存儲器等。圖1為本方案的結(jié)構(gòu)框圖。在大容量

2010-05-27 09:58:59 2226

2226

摘要:基于TI公司的高速數(shù)字信號處理器芯片,詳細(xì)描述美國SST公司推出的28SF040閃存芯片的性能特點、引腳功能,同時給出用其擴展DSP芯片的數(shù)據(jù)存儲器空間的硬件設(shè)計電路及相應(yīng)的軟件編程方法。 關(guān)鍵詞:閃爍存儲器,接口,DSP

2011-02-27 20:42:54 23

23 大多數(shù)的高速模數(shù)轉(zhuǎn)換器不能夠直接和DSP 相連。一個比較好的解決辦法是使用FIFO 作為輸入緩沖。FIFO 可以通過C6000 系列的外部存儲器接口( EMIF) 與TMS320C6000 系列

2017-05-31 16:09:36 3

3 EE-162:通過外部存儲器總線將ADSP-BF535 Blackfin處理器連接到高速轉(zhuǎn)換器(如AD9860/2上的轉(zhuǎn)換器)

2021-05-20 20:48:46 2

2

電子發(fā)燒友App

電子發(fā)燒友App

評論