一、UART

UART,全稱UniversalAsynchrONous Receiver/Transmitter,譯為通用異步收發(fā)器(異步串行通信口),比SPI、I2C這兩種同步串口的結(jié)構(gòu)要復(fù)雜很多,一般由波特率產(chǎn)生器(產(chǎn)生的波特率等于傳輸波特率的16倍)、UART接收器、UART發(fā)送器組成。硬件上有兩根線,一根用于發(fā)送,一根用于接收。數(shù)據(jù)是異步傳輸?shù)模瑢?duì)雙方的時(shí)序要求比較嚴(yán)格。串口按位(bit)發(fā)送和接收字節(jié),盡管比按字節(jié)(byte)的并行通信慢,但是串口可以在使用一根線發(fā)送數(shù)據(jù)的同時(shí)用另一根線接收數(shù)據(jù)。在多機(jī)通信上面用的最多。如果用GPIO口模擬UART總線,則需一個(gè)輸入口,一個(gè)輸出口。

1、UART幾個(gè)相關(guān)的概念

部分參考,GPIO,I2C,SPI,UART,USART,USB的區(qū)別_步印的博客-CSDN博客_spi和gpio的區(qū)別

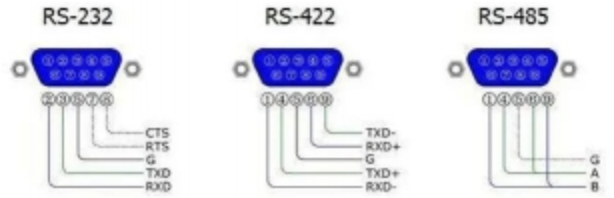

UART包括了RS232、RS499、RS423、RS422和RS485等接口標(biāo)準(zhǔn)規(guī)范和總線標(biāo)準(zhǔn)規(guī)范,即UART是異步串行通信口的總稱。而RS232、RS499、RS423、RS422和RS485等,是對(duì)應(yīng)各種異步串行通信口的接口標(biāo)準(zhǔn)和總線標(biāo)準(zhǔn),它規(guī)定了通信口的電氣特性、傳輸速率、連接特性和接口的機(jī)械特性等內(nèi)容。是屬于通信網(wǎng)絡(luò)OSI模型中的物理層?的概念。具體可以看《嵌入式硬件通信接口協(xié)議-UART(二)不同電氣規(guī)范下的標(biāo)準(zhǔn)》這篇文章。

UART的電平信號(hào)由MCU芯片決定,TTL/CMOS,是嵌入式硬件系統(tǒng)的信號(hào)電平。日常的開發(fā)過(guò)程中,MCU管腳上的UART通信電平就是TTL/CMOS電平信號(hào)。TTL電平,邏輯“0”等于0V電壓,邏輯“1”等于+5V電壓。CMOS電平,邏輯“0”接近0V電壓,邏輯“1”接近電源電壓(3.3V或其他)。TTL電路與CMOS電路比較,TTL電路是電流控制器件,而CMOS電路是電壓控制器件;TTL的速度快,傳輸延遲時(shí)間短(5-10ns),但是功耗大。CMOS電路的速度慢,傳輸延遲時(shí)間長(zhǎng)(25-50ns),但功耗低。CMOS電路本身的功耗與輸入信號(hào)的脈沖頻率有關(guān),頻率越高,芯片即越熱,這是正常現(xiàn)象。

COM口是PC(個(gè)人計(jì)算機(jī))上,異步串行通信口的簡(jiǎn)寫。在PC等操作系統(tǒng)上,COM口區(qū)別于USB、SATA接口的串行接口,定義了在操作系統(tǒng)中的規(guī)范。由于歷史原因,IBM的PC外部接口配置為RS232,成為實(shí)際上的PC界默認(rèn)標(biāo)準(zhǔn)。所以,現(xiàn)在PC機(jī)的COM口均為RS232。若配有多個(gè)異步串行通信口,則分別稱為COM1、COM2等等,但由于串口(COM)不支持熱插拔及傳輸速率較低,目前部分新主板和大部分便攜電腦已開始取消該接口。目前串口多用于工控和測(cè)量設(shè)備以及部分通信設(shè)備中。

UART多應(yīng)用兩個(gè)設(shè)備之間的通信,如用單片機(jī)的設(shè)備和計(jì)算機(jī)的通信。這樣的通信可以做長(zhǎng)距離的。UART速度比SPI、I2C兩者者快,最高達(dá)100K左右,用與計(jì)算機(jī)與設(shè)備或者計(jì)算機(jī)和計(jì)算之間通信,但有效范圍不會(huì)很長(zhǎng),約10米左右,UART優(yōu)點(diǎn)是支持面廣,程序設(shè)計(jì)結(jié)構(gòu)很簡(jiǎn)單,隨著USB的發(fā)展,UART也逐漸走向下坡。

我們常說(shuō)的串口,是指使用RS232標(biāo)準(zhǔn)進(jìn)行傳輸?shù)腢ART接口(9針)。

2、UART通訊需要配置的參數(shù)

1)波特率

波特率部分文章參考,DigCore:嵌入式硬件通信接口協(xié)議-UART(一)協(xié)議基礎(chǔ)

由于UART屬于異步通信,在通信過(guò)程中沒有同步時(shí)鐘CLK來(lái)提供給接收方,接收方也就無(wú)法同步地確定每個(gè)bit的寬度,也就無(wú)法對(duì)每個(gè)bit進(jìn)行正確的采樣。因此接收方必須依靠設(shè)置與發(fā)送方相同的波特率參數(shù),這樣接收方對(duì)信號(hào)管腳進(jìn)行采樣和解碼時(shí),才能正確判斷每個(gè)bit的值是“1”還是“0”,這也就是異步通信的特點(diǎn)。

在各類MCU的UART配置中,常用的波特率值有:4800Bd、9600Bd、19200Bd、115200Bd,單位Bd。

在維基百科的介紹中,可看到,波特率的值,直接以bit/s的單位取倒數(shù)后得到單位s/bit。在示波器端對(duì)UART發(fā)出的波形進(jìn)行抓取實(shí)驗(yàn),可見每bit的寬度在誤差允許范圍內(nèi)基本就是波特率的倒數(shù)值。

在百度百科的詞條介紹中

調(diào)制速率,指的是有效數(shù)據(jù)信號(hào)調(diào)制載波的速率,即單位時(shí)間內(nèi)載波調(diào)制狀態(tài)變化的次數(shù)。它是對(duì)符號(hào)傳輸速率的一種度量,1波特即指每秒傳輸1個(gè)符號(hào),而通過(guò)不同的調(diào)制方式,可以在一個(gè)碼元符號(hào)上負(fù)載多個(gè)bit位信息。單位“波特”本身就已經(jīng)是代表每秒的調(diào)制數(shù),以“波特每秒”(Baud per second)為單位是一種常見的錯(cuò)誤。

它代表的是信號(hào)的變化,而不是傳輸數(shù)據(jù)的多少。它表示每秒鐘內(nèi)通信線路狀態(tài)改變的次數(shù)。如果數(shù)據(jù)不壓縮,波特等于每秒鐘傳輸?shù)臄?shù)據(jù)位數(shù),如果數(shù)據(jù)進(jìn)行了壓縮。那么每秒鐘傳輸?shù)臄?shù)據(jù)位數(shù)通常大于調(diào)制速率,使得交換使用波特和比特/秒有時(shí)會(huì)產(chǎn)生錯(cuò)誤。

但是在現(xiàn)代的實(shí)際使用中,多數(shù)情況下,配置了MCU的波特率后,對(duì)輸出信號(hào)進(jìn)行觀測(cè)發(fā)現(xiàn),此時(shí)波特率就等于比特率。也正是因?yàn)榇藭r(shí)傳輸?shù)姆?hào)即8bit一個(gè)Byte的數(shù)據(jù)量,從而波特率等于比特率。

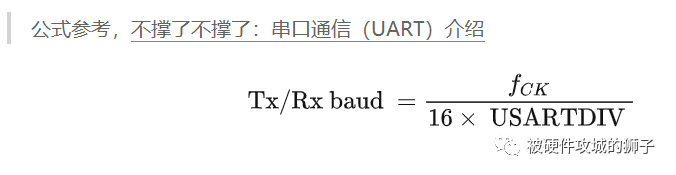

其中,fck為 USART 時(shí)鐘。USARTDIV 是一個(gè)存放在波特率寄存器(USART_BRR)的一個(gè)無(wú)符號(hào)定點(diǎn)數(shù)。DIV_Mantissa[11:0]位定義 USARTDIV 的整數(shù)部分,DIV_Fraction[3:0]位定義 USARTDIV 的小數(shù)部分。例如:DIV_Mantissa=24(0x18),DIV_Fraction=10(0x0A),此時(shí) USART_BRR 值為0x18A;那么USARTDIV的小數(shù)位10/16=0.625;整數(shù)位24,最終USARTDIV的值為24.625。

如果拿到一塊板子或者一套設(shè)備,但沒有源碼程序,純靠硬件抓取通信串口的數(shù)據(jù)內(nèi)容,首先利用示波器觀測(cè)每個(gè)bit的寬度,后換算成比特率,這時(shí)候比特率基本上就是波特率了。利用串口助手模塊,在PC端下載個(gè)串口助手,設(shè)置匹配的波特率進(jìn)行數(shù)據(jù)抓取。

比如抓到波形116us/bit, 直接轉(zhuǎn)換得:1bit/116us = 1 bit/(116/1000000)s = 8620.68 bit/s,此時(shí)配置串口助手的波特率,利用串口助手模塊與被測(cè)信號(hào)管腳進(jìn)行連接,即可實(shí)現(xiàn)串口數(shù)據(jù)的抓取。

2)數(shù)據(jù)格式

起始位:數(shù)據(jù)線空閑狀態(tài)為高電平,要發(fā)送數(shù)據(jù)時(shí)將其拉低一個(gè)時(shí)鐘周期表示起始位。

數(shù)據(jù)位:使用校驗(yàn)位時(shí),數(shù)據(jù)位可以有5~8位;如果不使用校驗(yàn)位,數(shù)據(jù)位可以達(dá)9位。

校驗(yàn)位:奇偶校驗(yàn),保證包括校驗(yàn)位和數(shù)據(jù)位在內(nèi)的所有位中1的個(gè)數(shù)為奇數(shù)或偶數(shù)。

停止位:為了表示數(shù)據(jù)包發(fā)送的結(jié)束,發(fā)送端需要將信號(hào)線從低電平變?yōu)楦唠娖剑⒅辽俦3?個(gè)時(shí)鐘周期。

3)流控制

流控制,俗話說(shuō)就是“握手”。流控制的作用,在不同處理性能的設(shè)備之間,數(shù)據(jù)傳輸之前,接收方會(huì)以“流控制”來(lái)通知發(fā)送方,是否可以繼續(xù)進(jìn)行接下來(lái)的數(shù)據(jù)傳輸。這樣的應(yīng)用場(chǎng)景多見于計(jì)算機(jī)與低性能的微控制器通信,也可見于PC與打印機(jī)之間進(jìn)行的數(shù)據(jù)傳輸,該特點(diǎn)都是接收方的接收緩存已滿或處理事務(wù)較慢時(shí),從而需要流控制來(lái)告知發(fā)送方稍后再發(fā)送。

流控制的方式分別有軟件和硬件兩種。

軟件的流控制方式,在UART通信中,只需RxD、TxD、GND三根即可,數(shù)據(jù)在傳輸過(guò)程中,依靠代碼的判斷處理,并通過(guò)收發(fā)雙方進(jìn)行的數(shù)據(jù)交互完成控制,在現(xiàn)有通信物理信號(hào)線基礎(chǔ)上,使用控制字符(ASCII表中的0x00~0x0x1F、0x7F)完成控制指令的交互。一般在私有協(xié)議下也會(huì)定義一些特殊字符設(shè)為控制指令。

硬件的流控制方式,即在原有的RxD、TxD、GND三根信號(hào)線的基礎(chǔ)上,再增加RTS/CTS和DTR/DSR這兩組信號(hào)線。第一組線是RTS(Request toSend)和CTS(Clear toSend)。當(dāng)接收方準(zhǔn)備好接收數(shù)據(jù),它置高RTS線表示它準(zhǔn)備好了,如果發(fā)送方也就緒,它置高CTS,表示它即將發(fā)送數(shù)據(jù)。第二組線是DTR(DataTerminal Ready)和DSR(Data SetReady)。這些線主要用于Modem通信。使得串口和Modem通信他們的狀態(tài)。例如:當(dāng)Modem已經(jīng)準(zhǔn)備好接收來(lái)自PC的數(shù)據(jù),它置高DTR線,表示和電話線的連接已經(jīng)建立。讀取DSR線置高,PC機(jī)開始發(fā)送數(shù)據(jù)。一個(gè)簡(jiǎn)單的規(guī)則是DTR/DSR用于表示系統(tǒng)通信就緒,而RTS/CTS用于單個(gè)數(shù)據(jù)包的傳輸。

3、UART的優(yōu)缺點(diǎn)

1)優(yōu)點(diǎn)

只使用兩根電線,不需要時(shí)鐘信號(hào)。有一個(gè)奇偶校驗(yàn)位,只要雙方設(shè)置后,就可以改變數(shù)據(jù)包的結(jié)構(gòu)

2)缺點(diǎn)

數(shù)據(jù)幀的大小限制為最多9位,不支持多個(gè)從屬或多個(gè)主系統(tǒng),每個(gè)UART的波特率必須在10%之內(nèi)

二、SPI

參考文章,?SPI、I2C、UART、CAN_一只大笨貓的博客-CSDN博客

SPI,Serial Peripheral interface,顧名思義就是串行外圍設(shè)備接口,是Motorola首先在其MC68HCXX系列處理器上定義的。SPI總線是微控制器四線的外部總線(相對(duì)于內(nèi)部總線)。與IIC不同,SPI沒有明文標(biāo)準(zhǔn),只是一種事實(shí)標(biāo)準(zhǔn),對(duì)通信操作的實(shí)現(xiàn)只作一般的抽象描述,芯片廠商與驅(qū)動(dòng)開發(fā)者通過(guò)data sheets和application notes溝通實(shí)現(xiàn)上的細(xì)節(jié)。

SPI接口主要應(yīng)用在EEPROM、FLASH、實(shí)時(shí)時(shí)鐘、AD轉(zhuǎn)換器,還有數(shù)字信號(hào)處理器和數(shù)字信號(hào)解碼器之間。SPI是一種高速,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳,同時(shí)為PCB的布局上節(jié)省空間,提供方便,正是出于這種簡(jiǎn)單易用的特性,現(xiàn)在越來(lái)越多的芯片集成了這種通信協(xié)議,比如AT91RM9200。

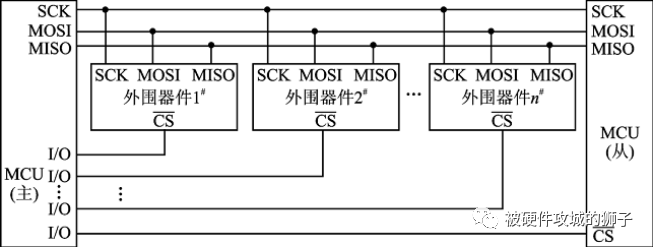

SPI分為主、從兩種模式,一個(gè)SPI通訊系統(tǒng)需要包含一個(gè)(且只能是一個(gè))主設(shè)備,一個(gè)或多個(gè)從設(shè)備。SPI接口的讀寫操作,都是由主設(shè)備發(fā)起。當(dāng)存在多個(gè)從設(shè)備時(shí),通過(guò)各自的片選信號(hào)進(jìn)行管理。

1、SPI使用的四根信號(hào)線

SCLK: Serial Clock (output from master):串行時(shí)鐘,用來(lái)同步數(shù)據(jù)傳輸,由主機(jī)輸出;

MOSI SIMO: Master Output, Slave Input(output from master):主機(jī)輸出從機(jī)輸入數(shù)據(jù)線,通常先傳輸MSB;

MISO SOMI: Master Input, Slave Output(output from slave):主機(jī)輸入從機(jī)輸出數(shù)據(jù)線,通常先傳輸LSB;

SS: Slave Select (active low, output from master):片選線,低電平有效,由主機(jī)輸出。

SSCS:控制芯片是否被選中的,也就是說(shuō)只有片選信號(hào)為預(yù)先規(guī)定的使能信號(hào)時(shí)(一般默認(rèn)為低電位),對(duì)此芯片的操作才有效,這就允許在同一總線上連接多個(gè)SPI設(shè)備成為可能。也就是說(shuō):當(dāng)有多個(gè)從設(shè)備的時(shí)候,因?yàn)槊總€(gè)從設(shè)備上都有一個(gè)片選引腳接入到主設(shè)備機(jī)中,當(dāng)我們的主設(shè)備和某個(gè)從設(shè)備通信時(shí)將需要將從設(shè)備對(duì)應(yīng)的片選引腳電平拉低。

2、SPI的四種操作模式

SPI的四種操作模式,它們的區(qū)別是定義了在時(shí)鐘脈沖的哪條邊沿轉(zhuǎn)換(toggles)輸出信號(hào),哪條邊沿采樣輸入信號(hào),還有時(shí)鐘脈沖的穩(wěn)定電平值(就是時(shí)鐘信號(hào)無(wú)效時(shí)是高還低)。

對(duì)于STM32等MCU自帶的硬件SPI外設(shè)來(lái)說(shuō),可能沒有那么重要,只需要配置一下模式就行了,但是對(duì)于使用使用GPIO模擬或者FPGA來(lái)實(shí)現(xiàn)SPI的時(shí)序,這一點(diǎn)是非常非常重要的。

Master 設(shè)備會(huì)根據(jù)將要交換的數(shù)據(jù)來(lái)產(chǎn)生相應(yīng)的時(shí)鐘脈沖(Clock Pulse),時(shí)鐘脈沖組成了時(shí)鐘信號(hào)(Clock Signal) ,每種模式由時(shí)鐘信號(hào)中的時(shí)鐘極性(clock polarity)CPOL與時(shí)鐘周期(clock phase)CPHA來(lái)定義。

不同的從設(shè)備可能在出廠是就是配置為某種模式,這是不能改變的,但我們的通信雙方必須是工作在同一模式下,所以我們可以對(duì)我們的主設(shè)備的SPI模式進(jìn)行配置,從而實(shí)現(xiàn)主從通訊。

時(shí)鐘極性CPOL是用來(lái)配置SCLK的電平出于哪種狀態(tài)時(shí)是空閑態(tài)或者有效態(tài);時(shí)鐘相位CPHA是用來(lái)配置數(shù)據(jù)采樣是在第幾個(gè)邊沿。

CPOL=0,表示當(dāng)SCLK=0時(shí)處于空閑態(tài),所以有效狀態(tài)就是SCLK處于高電平時(shí);

CPOL=1,表示當(dāng)SCLK=1時(shí)處于空閑態(tài),所以有效狀態(tài)就是SCLK處于低電平時(shí);

CPHA=0,表示數(shù)據(jù)采樣是在第1個(gè)邊沿,數(shù)據(jù)發(fā)送在第2個(gè)邊沿;

CPHA=1,表示數(shù)據(jù)采樣是在第2個(gè)邊沿,數(shù)據(jù)發(fā)送在第1個(gè)邊沿。

在高電平有效狀態(tài)時(shí),第一邊沿為上升沿,第二邊沿為下降沿;在低電平有效狀態(tài)時(shí),第一邊沿為下降沿,第二邊沿為上升沿

具體四種模式如下:

CPOL = 0,CPHA = 0:時(shí)鐘高電平時(shí)為有效狀態(tài),時(shí)鐘上升沿(第一個(gè)邊沿)采樣。

CPOL = 0,CPHA = 1:時(shí)鐘高電平時(shí)為有效狀態(tài),時(shí)鐘下降沿(第二個(gè)邊沿)采樣。

CPOL = 1,CPHA = 0:時(shí)鐘低電平時(shí)為有效狀態(tài),時(shí)鐘下降沿(第一個(gè)邊沿)采樣。

CPOL = 1,CPHA = 1:時(shí)鐘低電平時(shí)為有效狀態(tài),時(shí)鐘上升沿(第二個(gè)邊沿)采樣。

3、SPI的數(shù)據(jù)交換

參考文章,不撐了不撐了:SPI通信協(xié)議介紹

SPI可分為主、從兩種模式,并且支持全雙工模式,所以這也就導(dǎo)致STM32的SPI接口比較復(fù)雜。比如:配置SPI為主模式、配置SPI為從模式、配置SPI為單工通信、配置SPI為雙工通信等等。

在每個(gè) Clock 周期內(nèi),SPI 設(shè)備都會(huì)發(fā)送并接收一個(gè) bit 大小的數(shù)據(jù)(不管主設(shè)備還是從設(shè)備),相當(dāng)于該設(shè)備有一個(gè) bit 大小的數(shù)據(jù)被交換了。

1)主從機(jī)的選擇:

SPI 規(guī)定了兩個(gè) SPI 設(shè)備之間通信必須由主設(shè)備 (Master) 來(lái)控制次設(shè)備 (Slave)。一個(gè) Master 設(shè)備可以通過(guò)提供 Clock 以及對(duì) Slave 設(shè)備進(jìn)行片選 (Slave Select) 來(lái)控制多個(gè) Slave 設(shè)備,當(dāng)我們的主設(shè)備和某個(gè)從設(shè)備通信時(shí)將需要將從設(shè)備對(duì)應(yīng)的片選引腳電平拉低或者是拉高。SPI 協(xié)議還規(guī)定 Slave 設(shè)備的 Clock 由 Master 設(shè)備通過(guò) SCK 管腳提供給 Slave 設(shè)備, Slave 設(shè)備本身不能產(chǎn)生或控制 Clock,沒有 Clock 則 Slave 設(shè)備不能正常工作。

2)數(shù)據(jù)交換的流程:

參考文章:曾小慶:SPI通信協(xié)議詳解(spi總線)

主機(jī)和從機(jī)都有一個(gè)串行移位寄存器(SSPSR)?。它的主要作用是根據(jù)?SPI 時(shí)鐘信號(hào)狀態(tài),往 SSPBUF 里移入或者移出數(shù)據(jù),每次移動(dòng)的數(shù)據(jù)大小由 Bus-Width 以及 Channel-Width 所決定。Bus-Width 的作用是指定地址總線到 Master(主)設(shè)備之間數(shù)據(jù)傳輸?shù)膯挝弧hannel-Width 的作用是指定 Master(主)設(shè)備與 Slave(從)設(shè)備之間數(shù)據(jù)傳輸?shù)膯挝弧?/p>

主機(jī)通過(guò)向它的SPI串行寄存器寫入一個(gè)字節(jié)來(lái)發(fā)起一次傳輸。串行移位寄存器通過(guò)MOSI信號(hào)線將字節(jié)傳送給從機(jī),同時(shí)從機(jī)也將自己的串行移位寄存器中的內(nèi)容通過(guò)MISO信號(hào)線返回給主機(jī)。這樣,兩個(gè)移位寄存器中的內(nèi)容就被交換。外設(shè)的寫操作和讀操作是同步完成的。如果只進(jìn)行寫操作,主機(jī)只需忽略接收到的字節(jié);反之,若主機(jī)要讀取從機(jī)的一個(gè)字節(jié),就必須發(fā)送一個(gè)空字節(jié)來(lái)引發(fā)從機(jī)的傳輸。

SPI的時(shí)序其實(shí)很簡(jiǎn)單,主要是在SCLK的控制下,數(shù)據(jù)按照從高位到低位的方式依次移出主機(jī)寄存器和從機(jī)寄存器,并且依次移入從機(jī)寄存器和主機(jī)寄存器。當(dāng)寄存器中的內(nèi)容全部移出時(shí),相當(dāng)于完成了兩個(gè)寄存器內(nèi)容的交換。

假設(shè)主機(jī)的8位寄存器裝的是待發(fā)送的數(shù)據(jù)10101010,上升沿發(fā)送、下降沿接收、高位先發(fā)送。那么第一個(gè)上升沿來(lái)的時(shí)候,主機(jī)將會(huì)通過(guò)MOSI信號(hào)線傳輸給從機(jī)最高位1,自身寄存器變成0101010x。同時(shí),MISO信號(hào)線會(huì)從從機(jī)處返回一個(gè)數(shù)據(jù)給主機(jī),那么這時(shí)寄存器為0101010MISO,這樣在 8個(gè)時(shí)鐘脈沖以后,兩個(gè)寄存器的內(nèi)容互相交換一次。這樣就完成里一個(gè)SPI時(shí)序。

主機(jī)和從機(jī)的發(fā)送數(shù)據(jù)是同時(shí)完成的,兩者的接收數(shù)據(jù)也是同時(shí)完成的。也就是說(shuō),當(dāng)上升沿主機(jī)發(fā)送數(shù)據(jù)的時(shí)候,從機(jī)也發(fā)送了數(shù)據(jù)。所以為了保證主從機(jī)正確通信,應(yīng)使得它們的SPI具有相同的時(shí)鐘極性和時(shí)鐘相位。

3)SPI的傳輸速率:

參考文章;王超:一文看懂SPI協(xié)議

SCLK的速率就是SPI的傳輸速率,SPI協(xié)議沒有一個(gè)固定的速率,不像I2C標(biāo)準(zhǔn)模式100K,快速模式400K,高速模式3.4M,SPI的傳輸速率取決于器件本身支持多高的速率。最初的標(biāo)準(zhǔn)定義總線速度為100kbps。經(jīng)歷幾次修訂,主要是1995年的400kbps,1998的3.4Mbps。

4)SPI的傳輸?shù)奶攸c(diǎn):

參考文章:對(duì)三種總線SPI、UART、I2C分析理解 - 接口/總線/驅(qū)動(dòng) - 電子發(fā)燒友網(wǎng)

SCLK時(shí)鐘線存在使得數(shù)據(jù)是一位一位傳輸?shù)摹S蒘CLK提供時(shí)鐘脈沖,SDI、SDO則基于此脈沖完成數(shù)據(jù)傳輸。數(shù)據(jù)輸出通過(guò) SDO線,數(shù)據(jù)在時(shí)鐘上升沿或下降沿時(shí)改變,在緊接著的下降沿或上升沿被讀取。完成一位數(shù)據(jù)傳輸,輸入也使用同樣原理。這樣的傳輸方式有一個(gè)優(yōu)點(diǎn),與普通的串行通訊不同,普通的串行通訊一次連續(xù)傳送至少8位數(shù)據(jù),而SPI允許數(shù)據(jù)一位一位的傳送,甚至允許暫停,因?yàn)镾CLK時(shí)鐘線由主控設(shè)備控制,當(dāng)沒有時(shí)鐘跳變時(shí),從設(shè)備不采集或傳送數(shù)據(jù)。也就是說(shuō),主設(shè)備通過(guò)對(duì)SCLK時(shí)鐘線的控制可以完成對(duì)通訊的控制。

主從設(shè)備必須使用相同的工作參數(shù)——SCLK、CPOL 和 CPHA,才能正常工作。如果有多個(gè)從設(shè)備,并且它們使用了不同的工作參數(shù),那么主設(shè)備必須在讀寫不同從設(shè)備間重新配置這些參數(shù)。

參考文章:?華清遠(yuǎn)見:史上講得最清楚的I2C和SPI總線協(xié)議

SPI也沒規(guī)定通信應(yīng)答機(jī)制,沒有規(guī)定流控制規(guī)則。事實(shí)上,SPI主設(shè)備甚至并不知道指定的從設(shè)備是否存在。這些通信控制都得通過(guò)SPI協(xié)議以外自行實(shí)現(xiàn)。例如,要用SPI連接一支命令-響應(yīng)控制型?解碼芯片,則必須在SPI的基礎(chǔ)上實(shí)現(xiàn)更高級(jí)的通信協(xié)議。SPI并不關(guān)心物理接口的電氣特性,例如信號(hào)的標(biāo)準(zhǔn)電壓。在最初,大多數(shù)SPI應(yīng)用都是使用間斷性時(shí)鐘脈沖和以字節(jié)為單位傳輸數(shù)據(jù)的,但現(xiàn)在有很多變種實(shí)現(xiàn)了連續(xù)性時(shí)間脈沖和任意長(zhǎng)度的數(shù)據(jù)幀。

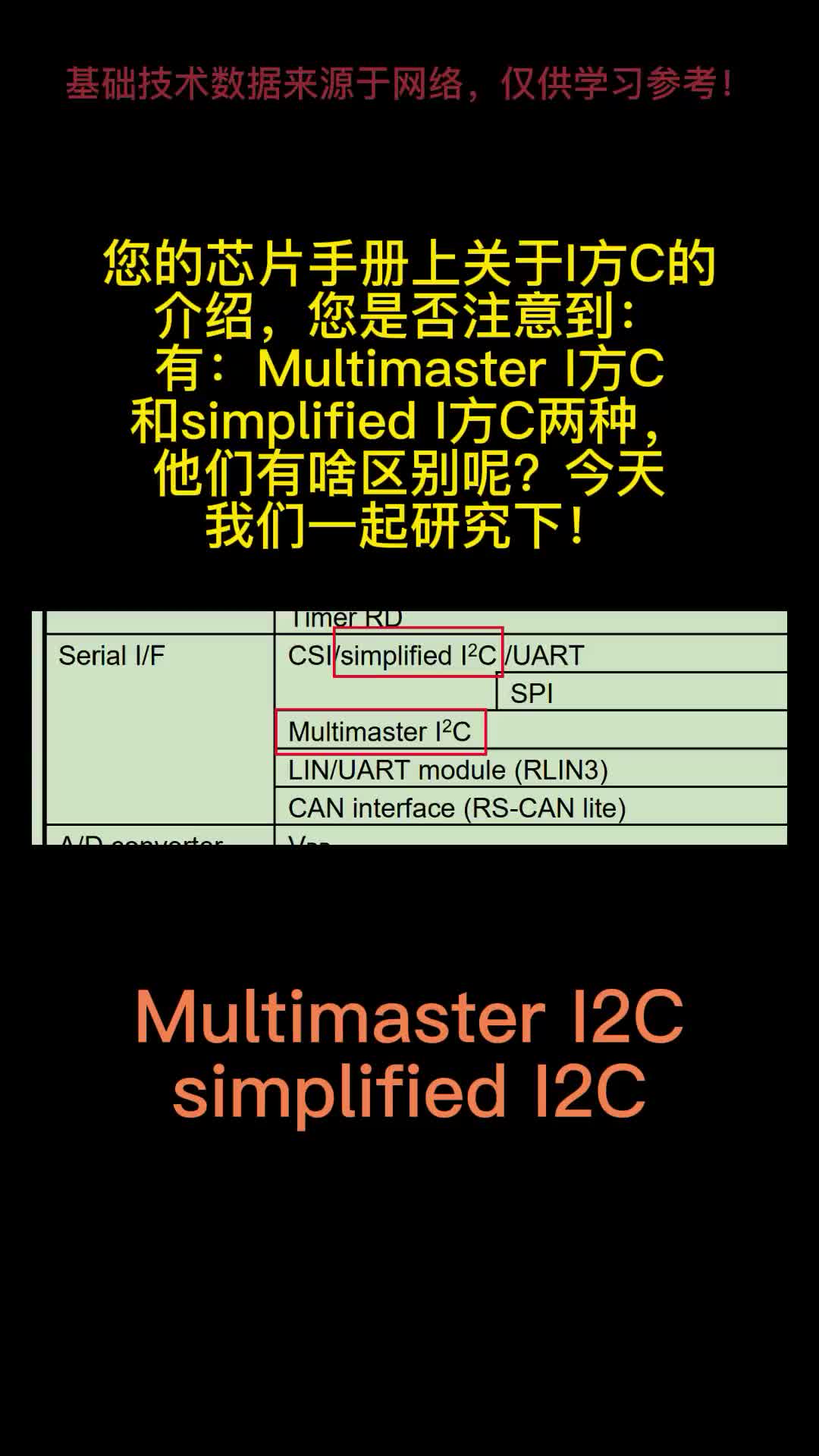

三、IIC

參考文章:SPI、I2C、UART、CAN_一只大笨貓的博客-CSDN博客_i2c spi

IIC(Inter-Integrated Circuit)開發(fā)于1982年,當(dāng)時(shí)是為了給電視機(jī)內(nèi)的CPU和外圍芯片提供更簡(jiǎn)易的互聯(lián)方式。電視機(jī)是最早的嵌入式系統(tǒng)之一,而最初的嵌入系統(tǒng)是使用內(nèi)存映射(memory-mapped I/O)的方式來(lái)互聯(lián)微控制器和外圍設(shè)備的。要實(shí)現(xiàn)內(nèi)存映射,設(shè)備必須并聯(lián)入微控制器的數(shù)據(jù)線和地址線,這種方式在連接多個(gè)外設(shè)時(shí)需大量線路和額外地址解碼芯片,很不方便并且成本高。為了節(jié)省微控制器的引腳和和額外的邏輯芯片,使印刷電路板更簡(jiǎn)單,成本更低,位于荷蘭的Philips實(shí)驗(yàn)室開發(fā)了IIC ,一種只使用二根線接連所有外圍芯片的總線協(xié)議。

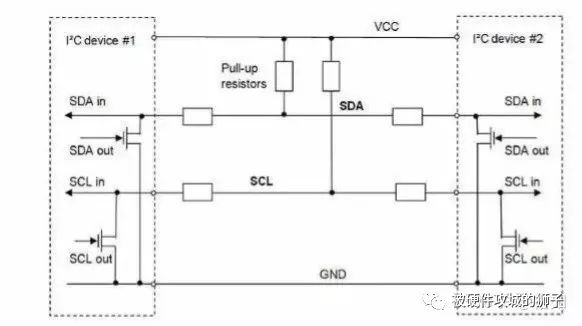

IIC 是多主設(shè)備的總線,IIC沒有物理的芯片選擇信號(hào)線,沒有仲裁邏輯電路,只使用serial data (SDA)數(shù)據(jù)線?和?serial clock(SCL)時(shí)鐘線兩條信號(hào)線,數(shù)據(jù)線用來(lái)傳輸數(shù)據(jù),時(shí)鐘線用來(lái)同步數(shù)據(jù)收發(fā)。兩根信號(hào)線都是雙向傳輸?shù)模@兩條線都是漏極開路或者集電極開路結(jié)構(gòu),使用時(shí)需要外加上拉電阻,可以掛載多個(gè)設(shè)備。

1、IIC的傳輸流程

參考文章:Kevin Zhang:硬件知識(shí)——IIC傳輸

IIC協(xié)議標(biāo)準(zhǔn)規(guī)定發(fā)起通信的設(shè)備稱為主設(shè)備,主設(shè)備發(fā)起一次通信后,其它設(shè)備均為從設(shè)備。

1)IIC 通信過(guò)程大致如下

首先,主設(shè)備發(fā)一個(gè)START信號(hào)。然后其它設(shè)備開始監(jiān)聽總線以準(zhǔn)備接收數(shù)據(jù)。當(dāng)START起始信號(hào)產(chǎn)生后,I2C總線就處于被占用的狀態(tài),當(dāng)停止信號(hào)產(chǎn)生后,總線就處于空閑狀態(tài)。

接著,主設(shè)備發(fā)送一個(gè)8位的數(shù)據(jù)幀(IIC規(guī)定數(shù)據(jù)幀大小必須為8位的字節(jié)),包括7位設(shè)備地址數(shù)據(jù)幀(每一個(gè)IIC設(shè)備都有一個(gè)唯一的七位設(shè)備地址)和?1位的讀寫操作的數(shù)據(jù)幀(讀/寫位用于確定主設(shè)備是向從設(shè)備發(fā)送數(shù)據(jù)還是主設(shè)備從從設(shè)備接受數(shù)據(jù),0代表寫,1代表讀)。

當(dāng)所有設(shè)備接收到數(shù)據(jù)后,比對(duì)地址自己是否為目標(biāo)設(shè)備。如果比對(duì)不符,設(shè)備進(jìn)入等待狀態(tài),等待STOP信號(hào)的來(lái)臨;如果比對(duì)相符,該設(shè)備會(huì)發(fā)送一個(gè)應(yīng)答信號(hào)ACKNOWLEDGE作回應(yīng)。這時(shí)主設(shè)備就和該從設(shè)備建立了連接。

當(dāng)主設(shè)備收到應(yīng)答后便開始傳送或接收數(shù)據(jù)。數(shù)據(jù)幀大小為8位,尾隨一位的應(yīng)答信號(hào)。主設(shè)備發(fā)送數(shù)據(jù),從設(shè)備應(yīng)答;相反主設(shè)備接收數(shù)據(jù),主設(shè)備應(yīng)答。

當(dāng)數(shù)據(jù)傳送完畢,主設(shè)備發(fā)送一個(gè)STOP信號(hào),向其它設(shè)備宣告釋放總線,其它設(shè)備回到初始狀態(tài)。

2)兩條數(shù)據(jù)線在各個(gè)通訊過(guò)程中高低電平的狀態(tài)

參考文章:Serendipity:Linux驅(qū)動(dòng)篇(七)——I2C(一)

空閑時(shí)SDA和SCL被拉高,處于高電平的位置。連到IIC總線上的任一設(shè)備輸出低電平都會(huì)把總線信號(hào)拉低,即各器件的SDA和SCL都是與的關(guān)系。根據(jù)這兩條線的高低電平、上升沿、下降沿就可以實(shí)現(xiàn)主機(jī)與I2C設(shè)備的通訊。

開始與結(jié)束:當(dāng)SCL保持高電平期間,SDA從高電平跳變到低電平,即為開始條件START。當(dāng)SCL保持高電平期間,SDA從低電平跳變到高電平,即為結(jié)束條件STOP。

傳輸:IIC總線標(biāo)準(zhǔn)規(guī)定SDA線的數(shù)據(jù)轉(zhuǎn)換必須在SCL線的低電平期。在SCL線的高電平期,SDA線的上數(shù)據(jù)是穩(wěn)定不變的。數(shù)據(jù)傳輸時(shí)先傳數(shù)據(jù)位。

主設(shè)備在SCL線上產(chǎn)生每個(gè)時(shí)鐘脈沖的過(guò)程中將在SDA線上傳輸一個(gè)數(shù)據(jù)位,當(dāng)一個(gè)字節(jié)按數(shù)據(jù)位從高位到低位的順序傳輸完后,緊接著,從設(shè)備在每個(gè)字節(jié)后的第9個(gè)時(shí)鐘周期將SDA保持低電平進(jìn)行確認(rèn)數(shù)據(jù),回傳給主設(shè)備一個(gè)ACK,此時(shí)才認(rèn)為一個(gè)字節(jié)真正的被傳輸完成。

當(dāng)然,并不是所有的字節(jié)傳輸都必須有一個(gè)ACK,比如:當(dāng)從設(shè)備不能再接收主設(shè)備發(fā)送的數(shù)據(jù)時(shí),從設(shè)備將回傳一個(gè)否定ACK,SDA線為高表示否定ACK。

應(yīng)答:當(dāng)IIC主機(jī)(不一定是發(fā)送端還是接受端)將8位數(shù)據(jù)或命令傳出后,會(huì)將SDA信號(hào)設(shè)置為輸入,等待從機(jī)應(yīng)答(等待SDA由高電平拉為低電平)。若從機(jī)正確應(yīng)答,表明數(shù)據(jù)或者命令傳輸成功,否則傳輸失敗,注意,應(yīng)答信號(hào)是數(shù)據(jù)接收方發(fā)送給數(shù)據(jù)發(fā)送方的。

3、IIC的一些拓展知識(shí)

參考文章:華清遠(yuǎn)見:史上講得最清楚的I2C和SPI總線協(xié)議

1)10位設(shè)備地址

任何IIC設(shè)備都有一個(gè)7位地址,理論上,現(xiàn)實(shí)中只能有127種不同的IIC設(shè)備。實(shí)際上,已有IIC的設(shè)備種類遠(yuǎn)遠(yuǎn)多于這個(gè)限制,在一條總線上出現(xiàn)相同的地址的IIC設(shè)備的概率相當(dāng)高。為了突破這個(gè)限制,很多設(shè)備使用了雙重地址——7位地址加引腳地址(external configuration pins)。IIC 標(biāo)準(zhǔn)也預(yù)知了這種限制,提出10位的地址方案。

2)設(shè)備沖突的解決辦法

如果有兩個(gè)設(shè)備同時(shí)向SCL線和SDA線發(fā)送信息,基于IIC總線的設(shè)計(jì),線路上不可能出現(xiàn)電平?jīng)_突現(xiàn)象。如果一支設(shè)備發(fā)送邏輯0,其它發(fā)送邏輯1,那么線路看到的只有邏輯0。也就是說(shuō),如果出現(xiàn)電平?jīng)_突,發(fā)送邏輯0的始終是“贏家”。

總線的物理結(jié)構(gòu)亦允許主設(shè)備在往總線寫數(shù)據(jù)的同時(shí)讀取數(shù)據(jù)。這樣,任何設(shè)備都可以檢測(cè)沖突的發(fā)生。當(dāng)兩支主設(shè)備競(jìng)爭(zhēng)總線的時(shí)候,“贏家”并不知道競(jìng)爭(zhēng)的發(fā)生,只有“輸家”發(fā)現(xiàn)了沖突——當(dāng)它寫一個(gè)邏輯1,卻讀到0時(shí)——而退出競(jìng)爭(zhēng)。

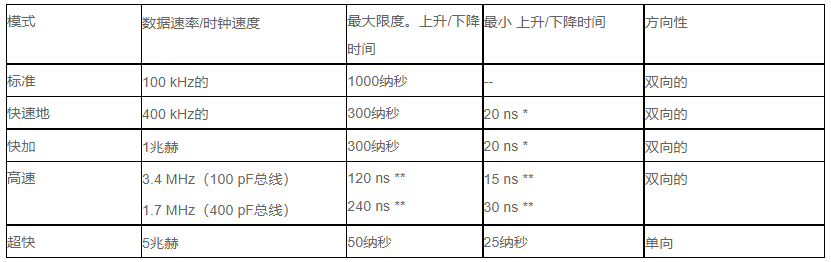

3)IIC的傳輸速率

IIC 數(shù)據(jù)傳輸速率有標(biāo)準(zhǔn)模式(100 kbps)、快速模式(400 kbps)和高速模式(3.4 Mbps),另外一些變種實(shí)現(xiàn)了低速模式(10 kbps)和快速+模式(1 Mbps)。

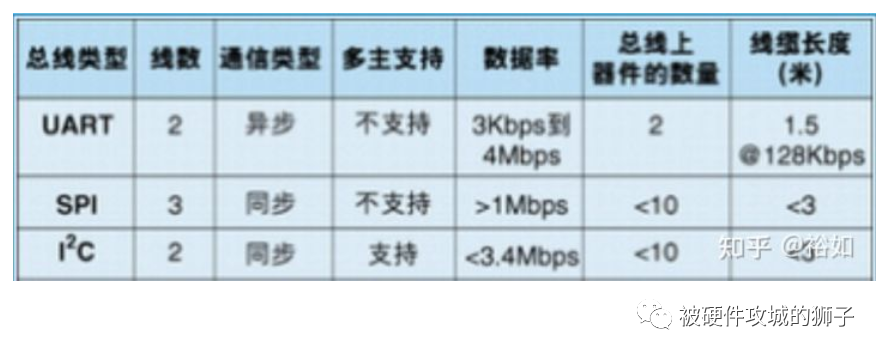

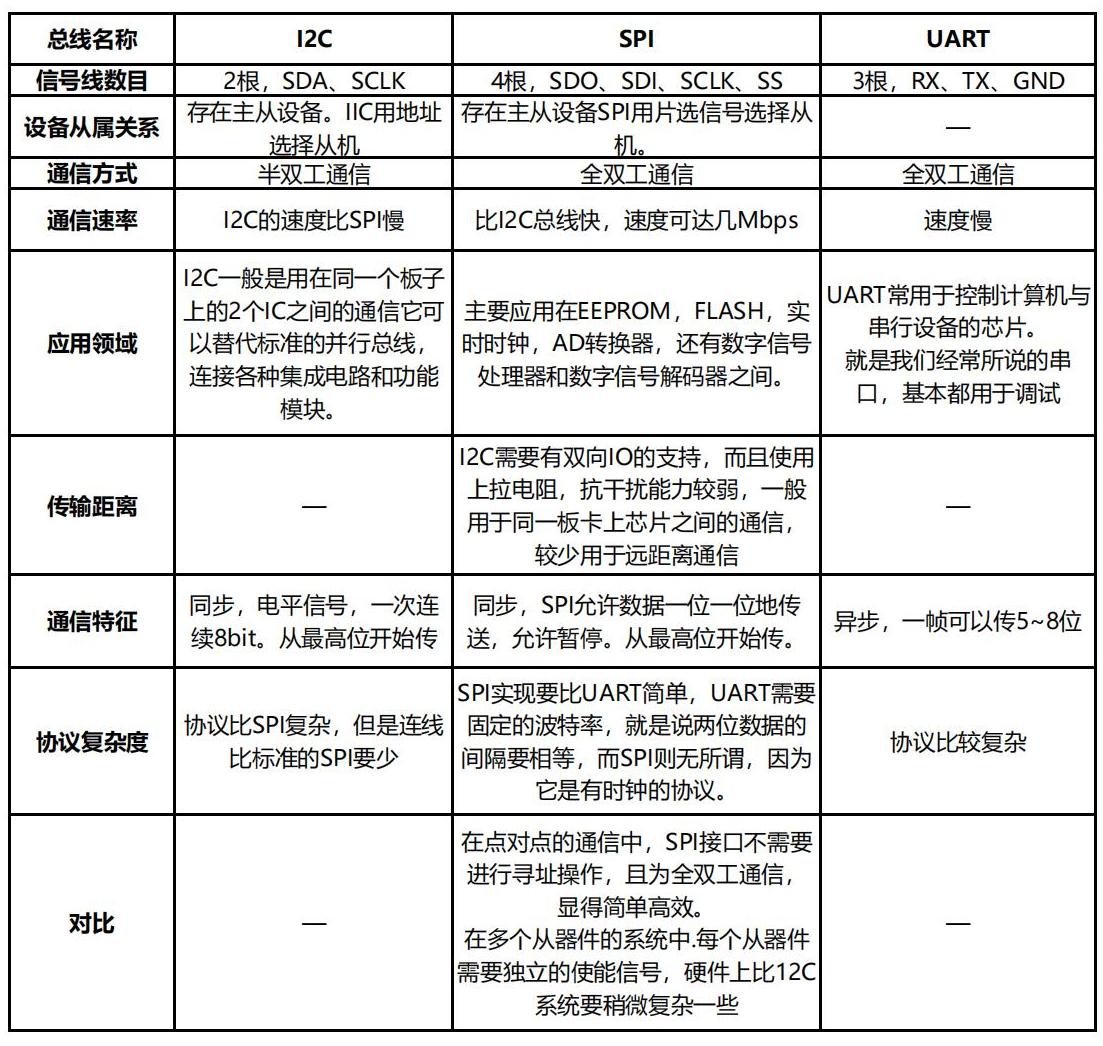

四、三種通訊方式的特點(diǎn)與區(qū)別:

同步通訊:I2C,SPI 異步通訊:UART

采集數(shù)據(jù)是否用的是時(shí)鐘的沿,如果是時(shí)鐘沿采數(shù)據(jù),同步傳輸,如果電平采集數(shù)據(jù)是異步。串口接受數(shù)據(jù)其實(shí)就是一個(gè)串轉(zhuǎn)并的過(guò)程。

SPI和UART可以實(shí)現(xiàn)全雙工,但I(xiàn)2C不行

IIC 和 SPI 這兩種通信協(xié)議非常適合近距離低速芯片間通信。通信方式都是短距離的,芯片和芯片之間或者其他元器件如傳感器和芯片之間的通信。SPI和IIC是板上通信,IIC有時(shí)也會(huì)做板間通信,不過(guò)距離甚短,不過(guò)超過(guò)一米,例如一些觸摸屏,手機(jī)液晶屏那些薄膜排線很多用IIC,IIC能用于替代標(biāo)準(zhǔn)的并行總線,能連接的各種集成電路和功能模塊。

I2C是多主控總線,所以任何一個(gè)設(shè)備都能像主控器一樣工作,并控制總線。總線上每一個(gè)設(shè)備都有一個(gè)獨(dú)一無(wú)二的地址,根據(jù)設(shè)備它們自己的能力,它們可以作為發(fā)射器或接收器工作。多路微控制器能在同一個(gè)I2C總線上共存這兩種線屬于低速傳輸。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論