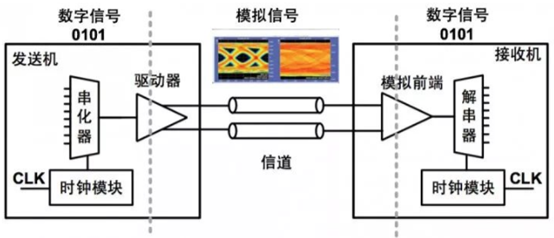

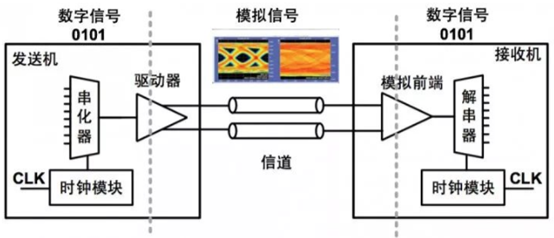

SerDes是SERializer(串行器)/DESerializer(解串器)的簡稱,是一種主流的時分多路復用(TDM)、點對點(P2P)的串行通信技術。

2023-11-14 09:32:39 2479

2479

LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術,LVDS 數據線連接廣泛應用于高速數據信號傳輸,例如

2020-10-30 16:07:34

通信,該SERDES接口方案具有成本低、靈活性高、研發周期短等特點。 1 硬件接口: 硬件的接口如上圖所示,主要包括發送與接收模塊。 發送模塊包括8b/10b編碼器,并串轉換器,鎖相環(PLL

2019-05-29 17:52:03

芯片差,CS5211的供貨周期較短方案的可行度和穩定性要比龍迅LT8911 LT7211、普瑞PS8625、昆泰CH7511這些方案要更好。CS5211是一種DP轉LVDS轉接芯片方案,可將eDP輸入

2021-08-02 20:00:42

一種基于TDM的工業串行實時通訊協議

2012-08-06 13:30:17

描述TIDA-00137 參考設計是一種高速串行視頻接口,通過此接口,可將采用 DVP (LVCMOS) 接口的遠程汽車 WVGA TFT LCD 顯示屏連接到視頻處理系統。此設計使用 TI

2022-09-19 07:05:20

求一種DSP+CPLD新型的智能儀器的設計方案

2021-05-08 07:54:25

求一種FOC電流采樣方案

2021-09-28 09:34:36

Jini的基本原理是什么?其結構是怎樣的?藍牙技術的基本原理是什么?其結構是怎樣的?求一種Jini與藍牙技術的結合應用方案

2021-06-04 06:05:46

求一種LCD和LED沖突的解決方案

2022-01-25 07:12:11

求一種MCU Specific Package單片機的具體解決方案

2021-12-10 07:46:15

NFC電子錢包總體結構是怎樣構成的?求一種NXP最新的NFC電子錢包解決方案

2021-05-24 06:44:09

求一種PCIe接口的視頻采集解決方案。

2021-04-30 06:29:43

求一種RK3326 android10.0橫屏修改方案

2022-02-17 08:03:13

求一種基于DSP平臺的低成本高速USB接口方案

2021-05-10 07:13:30

求一種便攜式RC測量儀的設計方案

2021-05-11 06:32:02

求各位大神指點一下,求一種正負5V的雙電源,是用到儀表放大器上,功率非常小,電路板只有DC24V輸入,希望電路占用的空間盡量的小。

2017-06-11 11:41:15

本文提出一種利用復雜可編程邏輯器件(Complex Programmable Logic Device,CPLD)設計技術[3]實現專用鍵盤接口芯片的方案。

2021-04-15 06:55:36

漂移及漂移形成的原因是什么?光纖漂移引起的SERDES FIFO溢出問題分析BBU SERDES 雙系時鐘方案及具體實現

2021-04-19 08:35:11

求大神分享一種基于LVDS接口的PCM解碼板設計

2021-04-20 07:09:15

求一種基于ARM Cortex-M處理器的音頻解決方案

2021-06-01 06:32:51

求一種基于FPGA的HDLC協議控制器設計方案

2021-04-30 06:53:06

求一種基于FPGA的永磁同步電機控制器的設計方案。

2021-05-08 07:02:07

求大神分享一種基于FPGA的誤碼性能測試方案

2021-04-30 06:39:46

求大神介紹一種基于FPGA的高速通信系統,通過電纜驅動器和接收均衡器,拓展了LVDS信號的傳輸距離。

2021-04-30 06:50:19

求一種基于QT的線材檢測方案

2021-09-28 07:58:56

求一種基于STM32的Modbus主機實現方案

2021-12-10 07:25:48

本文提出了一種基于TMS320C6xll接口的圖像獲取方案。

2021-06-03 06:53:07

求一種基于TMS320VC5410的會議電話解決方案

2021-05-28 07:23:38

求一種基于ZigBee的駕駛輔助系統解決方案

2021-05-14 06:22:01

求一種基于openmv競速小車的設計方案

2022-03-01 07:16:14

求一種基于單片機的簡易洗衣機系統仿真設計方案

2022-01-17 08:09:52

求一種多路溫度儀硬件方案及下位機程序開發方案

2022-02-24 07:17:42

求一種多通道同步數據采集及壓縮系統的設計方案。

2021-04-28 06:13:04

求一種射頻開關的解決方案

2021-05-21 06:46:38

求一種嵌入式Linux平臺的軟硬件的設計方案

2021-04-27 06:56:56

求一種基于FPGA芯片的嵌入式PLC處理器的設計方案。

2021-05-06 08:24:19

求一種應對壓電效應失效的電容器解決方案

2021-06-08 06:39:35

求一種數字式溫度測量電路的設計方案

2021-05-17 06:16:41

求一種以CPLD為核心處理電路的數字電壓表的設計方案

2021-04-28 07:14:04

求一種新型WCDMA直放站PA的設計方案

2021-05-26 06:14:52

求一種新型系統級可編程芯片的設計方案

2021-05-06 07:44:32

求一種智能物品清點系統的設計方案

2021-05-20 07:29:31

求一種汽車專用的供電方案

2021-05-13 07:01:20

求一種測試平臺上的阻抗測試方案

2021-05-06 09:13:47

RK818是什么?求一種用RK818實現電源管理的解決方案

2022-02-10 06:21:02

求一種電能質量無線監測系統的方案

2021-05-20 06:50:45

求一種過程分析儀器CAN網絡通信的設計方案

2021-05-27 06:40:53

求一種遠程智能垃圾桶報警系統的設計方案

2021-05-19 07:10:01

求一種基于FPGA的鎖相環位同步提取電路的設計方案。

2021-04-29 06:52:21

求一種陶瓷揚聲器系統的放大器設計方案

2021-06-04 07:10:45

求一種高保真24位兜CODEC的解決方案

2021-06-02 06:20:04

求大佬分享一種多光譜可見光遙感圖像壓縮系統的設計方案

2021-06-02 06:39:48

求大佬分享一種小型通信系統的設計方案

2021-05-28 06:13:52

求大佬分享一種空調遙控器破解方案

2022-02-15 06:02:22

求大神分享一種高速突發模式誤碼測試儀的FPGA實現方案

2021-04-29 06:58:18

折疊式手機面臨哪些問題?一種滿足手機高速圖像數據傳輸的差分串行接口方案

2021-06-01 06:51:04

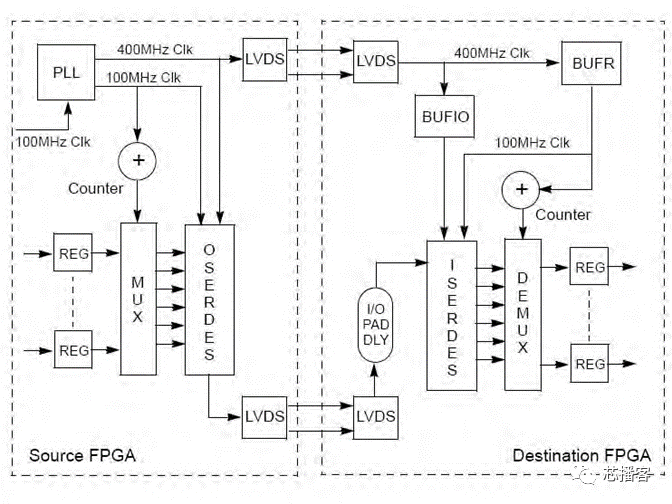

嗨, 我計劃在我的設計中使用SERDES(LVDS)作為背板。我已經瀏覽了virtex5用戶指南中的advnced IO部分,并看過ISERDES_NODELAY和OSERDES宏。我已經看到了一

2020-07-13 15:54:49

分享一種CH451與AMEG32的接口方案

2021-06-04 06:06:16

分享一種實用的WiFi語音解決方案

2021-05-19 06:49:24

分享一種智能卡接口的設計方案

2021-05-27 06:01:19

遵循信號走線限制,這些接口的抖動余地仍然是非常小的。固定頻率振蕩器可用于很多通用的SERDES標準;但是,這些解決方案價格昂貴。此外,這種做法缺乏靈活性,并且使調試、測試和生產變得困難。另一種解決方案

2019-05-21 05:00:13

一種FPGA與DSP的高速通信接口設計與實現方案

2021-06-02 06:07:16

如果不使用FPGA自帶的SERDES,可否適用LVDS接口實現其功能?

2023-05-08 17:37:48

描述TIDA-00135 參考設計是一種高速串行視頻接口,通過此接口,可將采用 OpenLDI (LVDS) 接口的遠程汽車 XGA TFT LCD 顯示屏連接到視頻處理系統。此設計使用 TI

2018-08-01 07:33:23

The SN65LVDS93 LVDS serdes (serializer/ deserializer) transmitter contains four 7-bit parallel-

2010-09-09 21:17:42 40

40 The SN65LVDS94 LVDS serdes (serializer/deserializer) receiver contains four serial-in 7-bit

2010-09-09 21:21:54 31

31 The SN65LVDS95 LVDS serdes (serializer/deserializer) transmitter contains three 7-bit parallel-load

2010-09-09 21:29:10 19

19 The SN65LVDS95 LVDS serdes (serializer/deserializer) transmitter contains three 7-bit parallel-load

2010-09-09 21:44:32 38

38 TDM網絡,TDM網絡是什么意思

TDM是一種復用技術,它基于時間將一個線路分為多個信道。該技術與電話公司語音服務有關。使用時分復用技術時,T1

2010-04-03 15:32:27 12550

12550 如何為 LVDS SERDES約束Arria 10 器件 IOPLL 位置

2018-06-22 08:47:00 5539

5539

本方案是以CME最新的低功耗系列FPGA的HR03為平臺,實現8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data

2019-05-24 15:33:25 4072

4072

電子發燒友App

電子發燒友App

評論