一、實驗目的??????????????????????????????????????????????????????????????????????

1. 熟悉CPLD的開發軟件的基本使用。

2. 掌握CPLD邏輯電路設計方法。

3. 會用邏輯分析儀進行數字電路的測試分析。

二、實驗任務和內容

1. 在CPLD中設計一個多位計數器電路,設計要求為:

(1)6位十進制加法/減法計數器,運行過程中可改變加法或減法;

(2)輸入計數信號頻率最高1MHz,信號電平為0~5V的脈沖信號。

(3)6位數碼管動態掃描顯示,顯示亮度均勻,不閃爍。

(4)有手動清零按鍵。

2.對設計的電路進行軟件仿真

3.計數器電路的CPLD下載、實驗調試。

4.使用虛擬邏輯分析儀進行調試和測試

三、實驗器材

1. 1.SJ-8002B電子測量實驗箱 ????????????????????????? 1臺

2.計算機(具有運行windows2000和圖形化控件的能力?????? 1臺

3.函數發生器? ?????????????????????????????????????? 1臺

4. SJ-7002 CPLD實驗板 ??????????????????????????????? 1塊

5 . 短接線若干

?? 4.1 CPLD介紹

?? 可編程邏輯器(PLD)是70年代發展起來的一種劃時代的新型邏輯器件,一般來說,PLD器件是由用戶配置以完成某種邏輯功能的電路。80年代末,美國ALTERA和XILINX公司采用E2CMOS工藝,分別推出大規模和超大規模的復雜可編程邏輯器件(CPLD)和現場可編程邏輯門陣列器件(FPGA),這種芯片在達到高度集成度的同時,所具有的應用靈活性和多組態功能是以往的LSI/VLSI電路無法比擬的。到90年代,CPLD/FPGA發展更為迅速,不僅具有電擦除特性,而且出現了邊緣掃描及在線編程等高級特性。另外,外圍I/O模塊擴大了在系統中的應用范圍和擴展性。較常用的有XILIN X公司的EPLD和ALTERA及LATTICE公司的CPLD。

??? CPLD/FPGA的設計開發采用功能強大的EDA工具,通過符合國際標準的硬件描述語言(如VHDL或VERILOG-HDL)來進行電子系統設計和產品開發,開發工具的通用性,設計語言的標準化以及設計過程幾乎與所用的CPLD/FPGA器件的硬件結構沒有關系,所以設計成功的邏輯功能軟件有很好的兼容性和可移植性,開發周期短;易學易用,開發便捷。

??? 盡管CPLD、FPGA以及其它類型的PLD器件的結構各有其特點和長處,但是概括起來它們都是由三大部分組成的:(1)一個二維的邏輯塊陣列,構成器件的邏輯組成核心;(2)輸入/輸出塊(3)連接邏輯塊的互聯資源,連線資源由各種長度的線段組成,也包括用于連接邏輯塊之間,邏輯塊與輸入輸出部分的可編程連接開關。

??? 本CPLD實驗電路板選用ALTERA公司的EPM7128SLC84器件,EPM7128SLC84的特點為:84引腳Pin,內部有128個宏單元、2500個等效邏輯門、15ns的速度、PLCC84封裝形式。除電源引腳、地線引腳、全局控制引腳和JTAG引腳外,共提供了64個可用I/O腳,這些引腳可以任意配置為輸入、輸出和雙向方式。

? ????????????????????

????????????????????????? 圖1?? CPLD芯片EPM7128SLC84外形圖

?? 4.2 CPLD(FPGA)器件的設計和驗證步驟

?? 一般可分為設計輸入、編譯、功能仿真和時延仿真、器件下載(編程)、硬件電路三個設計步驟以及相應的功能仿真、時序仿真和器件測試三個設計驗證過程。

?? (1).設計輸入:設計輸入有多種方式,目前最常用的有電路圖和硬件描述語言兩種,對于簡單的設計,可采用原理圖的方式設計,對于復雜的設計可使用原理圖或硬件描述語言(Verilog、AHDL、VHDL語言),或者兩者混用,采用層次化設計方法,分模塊層次地進行描述。原理圖設計方法主要是按照數字系統的功能采用具體的邏輯器件組合來實現的,把這些由具體器件實現邏輯功能的電路圖輸入到軟件當中。這種設計方法比較直觀。硬件描述語言設計方法主要把數字系統的邏輯功能用硬件語言來描述

? (2)編譯:編譯前先選擇器件的系列、型號,分配輸入/輸出管腳進行管腳,然后開始編譯編譯是指從設計輸入文件到熔絲圖文件(CPLD)或位流文件(FPGA)的編譯過程。在該過程中,編譯軟件自動地對設計文件進行綜合、優化,并針對所選中的器件進行映射、布局、布線、產生相應的熔絲圖或位流數據文件。

? (3)仿真:分為功能仿真(Functional)和時延(Timing)仿真:編譯成功的設計并不一定完全正確,可通過仿真來驗證電路是否達到設計要求,基本思路是首先用波形編輯器編輯仿真文件,給輸入加載不同的激勵信號,然后運行仿真器,產生對應的輸出,根據輸入和輸出的關系,以此判別設計的正確性。

? (4)器件編程:器件編程就是將熔絲圖文件或位流數據文件下載到相應的CPLD或FPGA器件中。

? (5)系統硬件電路測試

????????????????????????

?????????????????????? ? ?? 圖2??? CPLD設計流程

?? 4.3 設計軟件的使用

??? 對CPLD的設計可使用ALTERA公司的MAX-PLUSⅡ或Quartus Ⅱ,設計的主要步驟為:

? (1)創建或打開一個工程。

? (2)原理圖輸入方式:新建一個圖形文件,輸入符號(代表子模塊或元件、輸入輸出引腳),連線,存盤。如圖4所示為采用兩片74190級聯的兩位十進制計數器電路,文件名為Z74190.gdf。

? (3)文本輸入方式:新建一個文本文件,輸入HDL語言編寫的電路,存盤。

? (4)選擇芯片為CPLD實驗電路板選用的EPM7128SLC84器件,分配引腳。

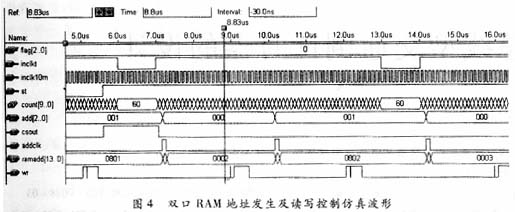

? (5)波形仿真,首先新建空白的波形文件,導入本設計電路的輸入輸出節點,給輸入節點按照需要指定時鐘信號和高低電平,開始仿真,得到結果,再分析結果。如圖5為Z74190.gdf的仿真文件波形。

? (6)CPLD程序的下載:我們采用的是并口下載電纜ByteBlaster,它可以對MAX7000S系列進行在線編程。該下載電纜具有以下幾個部分:與PC機并行口相連的25針插座頭、與PCB板插座相連的10針插頭。其示意圖如3所示。

???????? ????????

????????????????????????????? 圖 3?? 并行電纜下載示意圖

? 設計舉例:圖 4和圖 5分別是用原理圖方式設計的2位十進制計數器的原理圖和軟件仿真波形圖。

? ????

????

???????????????圖4兩位十進制計數器電路圖??? ???? ??????????????????????????????????????? ??圖11-5 兩位十進制計數器電路仿真波形圖?????

?? 4.4 CPLD實驗電路板原理和虛擬邏輯分析儀使用?? 實驗電路板的組成和虛擬邏輯分析儀的使用在本實驗指導書的“實驗四 邏輯分析儀的原理和應用”中已作了說明,請讀者參考。圖6 為CPLD板的詳細電路圖。CPLD與62芯插座定義表見表1和CPLD可供用戶自定義的引腳見表2。

- 使用CPLD板的1.000MHz的晶振時鐘,需放置CPLD板上S1短路塊位置在右面。

| 引腳名稱 |

CPLD |

62芯插座引腳 |

說明 |

引腳名稱 |

CPLD對應腳 |

62芯插座引腳 |

說明 | |

|

DO0 |

P40 |

16 |

連接邏輯分析儀的24個輸入通道 |

DO24 |

P63 |

28 |

系統保留 | |

|

DO1 |

P36 |

48 |

DO25 |

P76 |

60 | |||

|

DO2 |

P41 |

17 |

DO26 |

P64 |

29 | |||

|

DO3 |

P44 |

49 |

DO27 |

P75 |

61 | |||

|

DO4 |

P45 |

18 |

DO28 |

P68 |

30 | |||

|

DO5 |

P46 |

50 |

VCC |

P3,P13, |

31,62 |

+5V電源 | ||

|

DO6 |

P48 |

19 | ||||||

|

DO7 |

P49 |

51 | ||||||

|

DO8 |

P50 |

20 | ||||||

|

DO9 |

P51 |

52 |

GND |

P1,P7, |

13,44 |

電源地 | ||

|

DO10 |

P55 |

21 | ||||||

|

DO11 |

P52 |

53 | ||||||

|

DO12 |

P54 |

22 | ||||||

|

DO13 |

P65 |

54 | ||||||

|

DO14 |

P57 |

23 |

CPLD時鐘源 |

P83 |

45 |

由S1短路 | ||

|

DO15 |

P67 |

55 | ||||||

|

DO16 |

P56 |

24 | ||||||

|

DO17 |

P69 |

56 | ||||||

|

DO18 |

P58 |

25 |

outsideclk |

P39 |

15 |

選擇接(P83) | ||

|

DO19 |

P70 |

57 |

allCLR |

P35 |

47 |

系統總清零 | ||

|

DO20 |

P61 |

26 |

outside_tri |

P37 |

14 |

外部觸發 | ||

|

DO21 |

P73 |

58 |

||||||

|

DO22 |

P60 |

27 |

||||||

|

DO23 |

P74 |

59 |

表2??? 用戶可用的CPLD自定義I/O引腳

P4 |

P5 |

P6 |

P8 |

P9 |

P10 |

P11 |

P15 |

P16 |

P17 |

P18 |

P20 |

P21 |

|

P22 |

P24 |

P25 |

P27 |

P28 |

P29 |

P30 |

P31 |

P77 |

P79 |

P80 |

P81 |

?

?????????????????????????????????? 圖6 ? CPLD實驗板電路原理圖

?? 設計和調試的過程是:①任務分析,層次分解,得到頂層設計框圖,大致確定每個子模快(子電路)的功能、輸入和輸出;②子模快電路設計和軟件仿真;③完成頂層電路設計,頂層仿真;④分配引腳,下載,連線和調試。

?? 軟件仿真注意盡量給定符合實際電路工作的輸入電平、時鐘,仿真最小間隔不小于20ns,仿真時間長短適中。

?? 5.1 設計任務分析

?? 根據設計任務,可分為兩大部分:多位計數器電路和計數結果動態顯示電路。根據CPLD電路的層次化設計功能,設計出如圖7所示的頂層設計框圖。

?? 6位十進制的計數器對輸入的脈沖計數,有加減計數控制和清零計數值控制,輸出6位十進制計數值,每位都用4位BCD碼表示,共有24根線。

?? 根據動態掃描顯示的需要,必須設計一個6位BCD選1的多路數據選擇器,輸出的一位BCD碼(4根線)送給BCD-七段譯碼器譯成段信號,從CPLD輸出給數碼管的7段。同時多路數據選擇器的控制選通信號需要3根,必須與6位數碼管的位選信號同步。

?? 位選信號來自電路板的時鐘(1MHz)分頻,在用譯碼器譯碼(每次只能選中一個數碼管)。要保證多位顯示均勻和不閃爍,請計算和設計分頻的頻率和電路。

? ??????????

??????????????????????????????????? 圖7?? 計數器頂層設計框圖

?? 5.2 部分電路設計和軟件仿真提示

?? 電路的設計均有原理圖設計和HDL語言文本設計兩種方法,根據電路的特點和各人的情況,自己選用。

?? 對每個子模快進行軟件仿真,先創建波形文件,設定時間間隔和解釋時間,編輯輸入波形,運行仿真,分析結果是否正確。若不正確,則修改設計,重新編譯后,再仿真,直到正確為止。

? (1)6位十進制的計數器子模塊設計:

?? 沒有現成電路可用,所以必須自己設計。

?? 為什么不選用二進制計數器?(從顯示要求、二進制轉換為BCD電路的難易等考慮)

?? 設計方法一:選用6個1位的可逆帶清零十進制計數器級聯得到。注意進位/借位信號的時序。

?? 設計方法二:使用HDL語言編程,注意同時滿足十進制、加、減的進位和借位。

?(2)6位BCD選1的多路數據選擇器設計:

? 沒有現成電路可用,所以必須自己設計。

? 可選用多個數據選擇器來組合。要求控制選通信號需要3根,按000-001-010-011-100-101變化,只有6個狀態。

?(3)BCD-七段譯碼器設計:

? 有現成電路選用,注意共陰和共陽數碼管的區別。

? 位選信號產生

? ①位選譯碼:每次選中一個,可選用什么譯碼器?注意位選電平是高電平有效還是低電平有效。

? ②位選控制:要求為6個狀態,設計電路可采用狀態機的方法,但仔細分析6個狀態之間的關系后,可得出符合_________的計數器。

? 設計方法:語言和圖形均可。

?? 分頻電路:位選信號來自電路板的時鐘(1MHz)分頻,要保證多位顯示均勻和不閃爍,先計算分頻電路要求的輸出頻率,在設計分頻電路。可使用計數器分頻。

?? 5.3分配引腳和編譯、下載

?? 引腳分配要滿足CPLD電路板上已有的連線情況,把主要的輸入信號和重要的中間結果同時分配給邏輯分析儀的輸入通道A0~A23,可以利用邏輯分析儀進行測試,觀察到電路實際的內部工作時序。每次分配引腳后,需重新編譯后,再下載。

?? 6.1實驗硬件連接

?? 根據各人設計的計數器電路和分配的引腳連線,計數器輸入控制信號連接開關和按鍵,計數脈沖信號連接到函數發生器的TTL(CMOS)輸出端。計數器的輸出位選分別連接6個數碼管的為選端L1~L6注意,左邊的數碼管為低位,7段信號分別連接。

?? 6.2調試和測試

?? 按照以下順序對計數器電路進行測試,如不正確,請按下面步驟檢查:連線——引腳分配——CPLD電路設計。改正錯誤,再測試,若是CPLD電路錯誤,需重新編譯和重新下載。

?? ①檢查動態掃描電路

?? 數碼管7段信號全部直接接地,位選分別連接CPLD輸出位信號,這時,6個數碼管應該穩定顯示“888888”。

?? ②檢查加法計數器是否正確

?? 連接數碼管7段信號到CPLD指定輸出引腳,位選分別連接CPLD輸出位信號,選計數器輸入連接函數發生器的TTL電平信號輸出端,設置函數發生器為方波,頻率為1~2Hz,加/減控制信號輸入“加”有效,觀察數碼管的顯示,應是加1計數,更新頻率即為輸入信號頻率。提高輸入信號頻率,使計數更新快,檢查計數器進位和高位計數是否正確。

?? ③檢查減法計數器是否正確

?? 加/減控制信號輸入“減”有效,測試方法同上。

?? ④檢查“清零”控制是否正確。

???????????????????? ?????????? 圖8 實驗硬件組成圖

電子發燒友App

電子發燒友App

評論