ADF4350簡介

ADF4350具有一個集成電壓控制振蕩器(VCO),其基波輸出頻率范圍為2200MHz至4400MHz。結合外部環路濾波器和外部基準頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。所有片內寄存器均通過簡單的三線式接口進行控制。該器件采用3.0V至3.6V電源供電,不用時可以關斷。

ADF4350特性

輸出頻率范圍:137.5MHz至4400MHz

小數N分頻頻率合成器和整數N分頻頻率合成器

低相位噪聲VCO

可編程1/2/4/8/16分頻輸出

均方根(RMS)抖動:0.5ps(典型均方根值)

電源電壓:3.0V至3.6V

模擬和數字鎖定檢測

在寬帶寬內快速鎖定模式

周跳減少

1.8V邏輯兼容

可編程雙模預分頻器:4/5或8/9

可編程輸出功率水平

RF輸出靜音功能

三線式串行接口

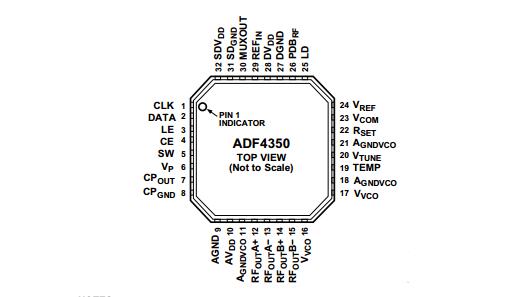

adf4350引腳圖及功能

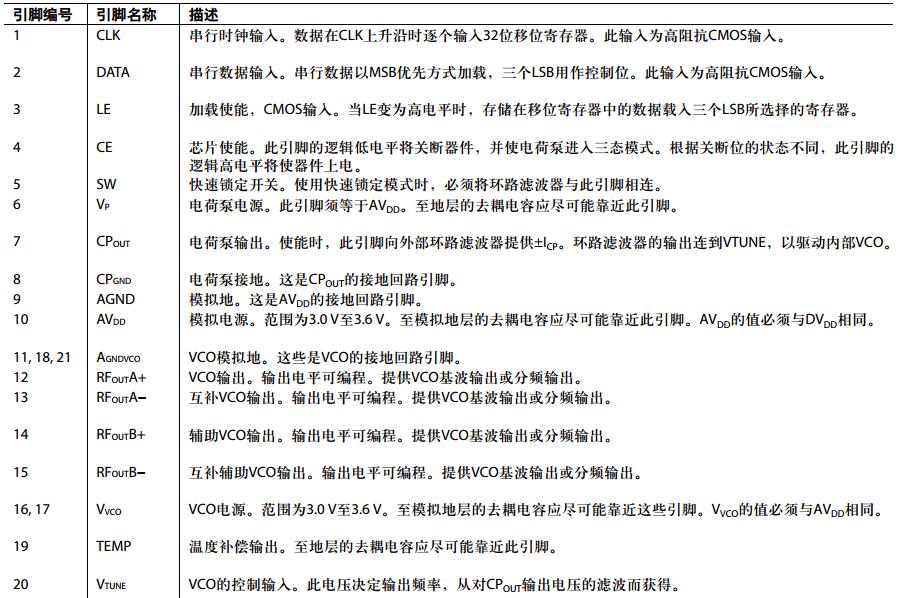

adf4350時序特性

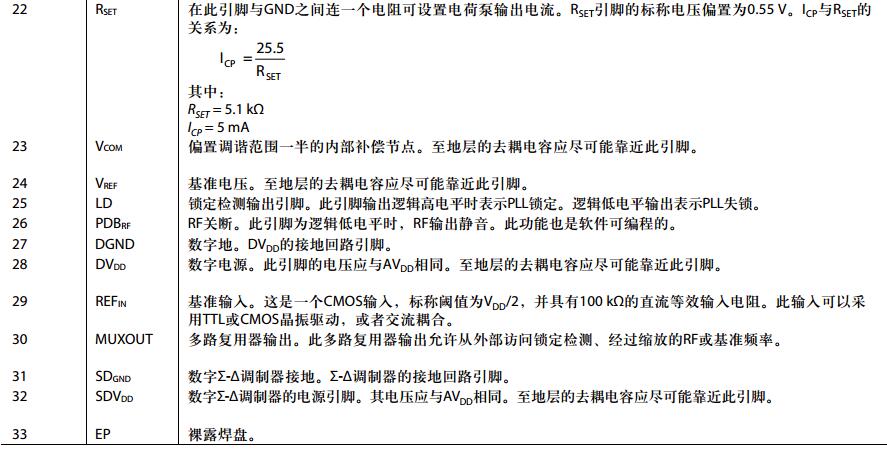

adf4350應用電路

本電路利用低噪聲、低壓差(LDO)線性調節器為寬帶集成PLL和VCO供電。寬帶壓控振蕩器(VCO)可能對電源噪聲較為敏感,因此,為實現最佳性能,建議使用超低噪聲調節器。

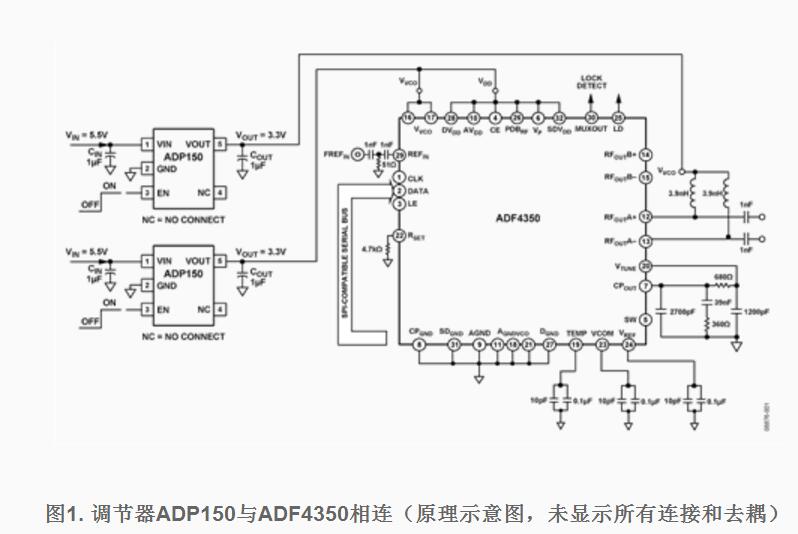

圖1所示電路使用完全集成的小數N分頻PLL和VCO ADF4350,它可產生137.5 MHz至4400 MHz范圍內的頻率。ADF4350采用超低噪聲3.3 V ADP150調節器供電,以實現最佳LO相位噪聲性能。

ADP150 LDO的積分均方根噪聲較低,僅為9 μV(10 Hz至100 kHz),有助于盡可能降低VCO相位噪聲并減少VCO推壓的影響(等效于電源抑制)。

圖2是評估板的照片,它利用ADP150 LDO為ADF4350供電。ADP150代表業界噪聲最低、封裝最小、成本最低的LDO,采用4引腳、0.8 mm x 0.8 mm、0.4 mm間距WLCSP封裝或方便的5引腳TSOT封裝。因此,在設計中加入ADP150對系統成本和電路板面積的影響極小,但卻能顯著改善相位噪聲性能。

adf4350編程使用總結

近來項目中使用了ADI公司的ADF4350芯片來產生3.45GHz的本振信號。調試中也遇到了一些問題,現在跟大家分享一下設計的過程和調試經歷。

一、設計原理

鎖相環的基本原理,相信大家都很熟悉,在此就不陳述了。設計中使用10MHz晶振或者信號源做為參考輸入,差分3.45GHz輸出。采用小數分頻模式,低噪聲模式,鑒相器頻率為20MHz(芯片內部將輸入時鐘倍頻),環路濾波器帶寬為100KHz,分頻比172.5。設計中使用FPGA(XilinxV5FX70T)來進行SPI配置。

另外,設計時將LD管腳連接上一個LED燈,程序中配置成模擬鎖定,來觀察鎖相環是否鎖定。相關的verilog配置程序在附件中[hide][/hide]。

寄存器配置的數據為:

Regisiter5:

32‘h00C00005;

Regisiter4:

32’h000803FC;

Regisiter3:

32‘h000101B3;

Regisiter2:

32’h06005E42;

Regisiter1:

32‘h0800FD01;

Regisiter0:

32’h00563E80;

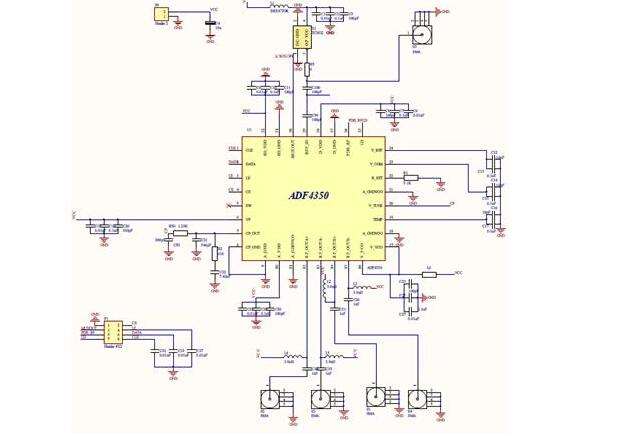

鎖相環原理圖設計主要包括電源電路設計,FPGA輸入信號電路設計,管腳去藕設計,外接環路濾波器設計,輸出電路匹配設計,具體電路圖見圖1。

圖1ADF4350外圍電路圖

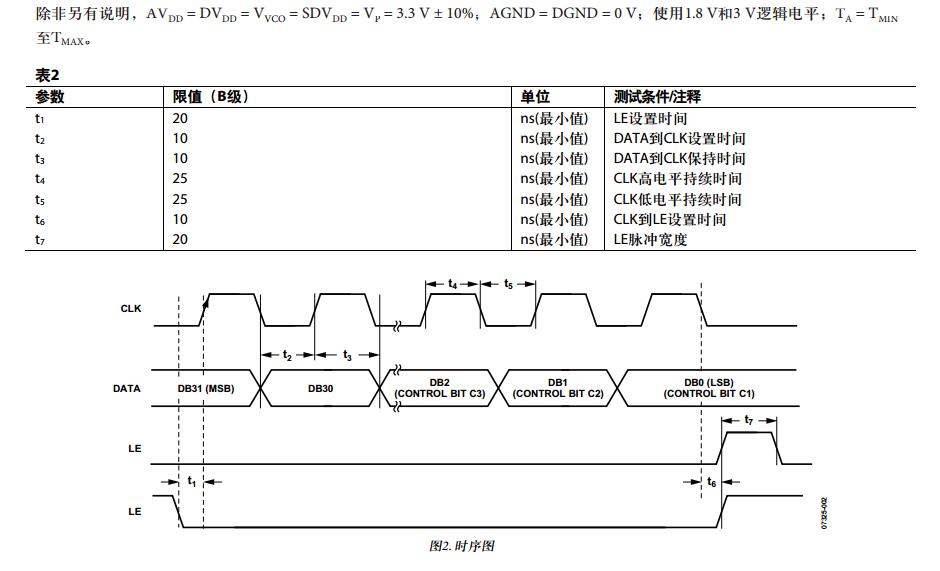

1.1管腳去藕設計:

由于PLL電源和電荷泵電源質量要求比較高,所以電源要具有良好的退耦,相比之下,電荷泵的電源具有更加嚴格的要求。具體實現如下:

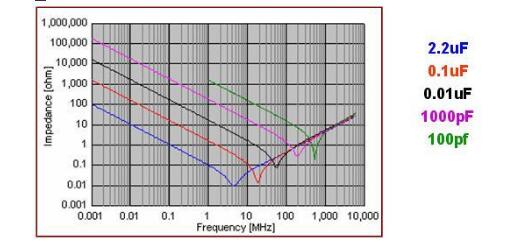

在電源引腳出依次放置0.1μF,0.01μF,100pF的電容。最大限度濾除電源線上的干擾。大電容的等效串聯電阻往往較大,而且對高頻噪聲的濾波效果較差,高頻噪聲的抑制需要用小容值的電容。如圖2可以看到,隨著頻率的升高,經過一定的轉折頻率后,電容開始呈現電感的特性。不同的電容值,其轉折頻率往往不同,電容越大,轉折頻率越低,其濾除高頻信號的能力越差。

圖2電容阻抗特性分析

1.2環路濾波器設計

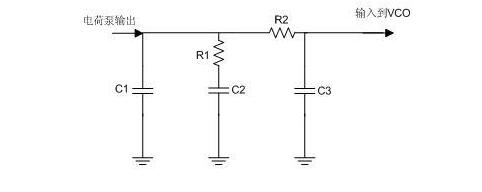

環路濾波器使用ADI公司的ADIsimPLL來設計,使用的是無源低通濾波器,帶寬100KHz(如圖3)。圖中電容器C1來自電荷泵(ADF4350的CP引腳的脈沖轉化為直流電壓,但是根據對開環傳遞函數分析,它存在一個二階極點,會引起環路的不穩定。所以引入了R1和C2穩定環路。它給直流控制電壓帶來的紋波干擾,可由C3濾除。

圖3環路濾波器原理圖

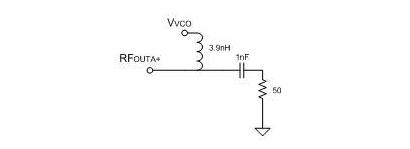

1.3輸出電路匹配

輸出電路采用datasheet建議的匹配電路來實現(如圖4)。

圖4RF輸出匹配2圖

二、測試過程

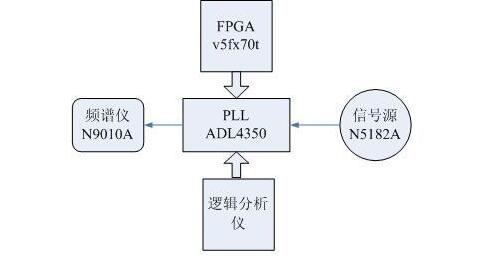

2.1測試平臺如圖5所示。

2.2測試步驟

1、檢查電路焊接無誤,上電查看電流在正常值范圍,電路中電壓測量正常。

2、為了測試外接晶振性能,先使用信號源產生20MHz的時鐘輸入信號接到CLK管腳。再接上信號源、頻譜儀,用FPGA將配置信息下載到PLL,PLL輸出隨每次通斷電結果時有時無,有輸出時頻率也不對。

圖5測試平臺

3、檢查電路連接,發現FPGA和PLL沒有共地,共地后測試,仍然沒有結果,此時電流在80mA左右,datasheet上查看正常工作時電流在140mA左右。

4、分析:有幾次信號輸出,說明電路能夠正常工作,主要可能是配置數據不正確或者沒有配置下去。

5、將這些電容拿掉,重新配置,結果還是不對,是否是SPI配置速度太快,PLL芯片來不及響應,當前配置速度為10MHz,雖然PLL的datasheet上說明配置速度最高可以支持到20MHz,但也只是給出了最大值,沒有典型值,決定將速度改低試試。

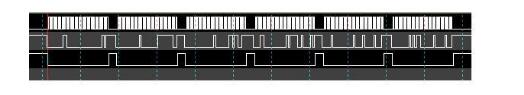

6、將速度改為1M,重新配置,結果還是不對,使用邏輯分析儀抓取PLL這邊SPI數據。

7、再次使用邏輯分析儀抓取PLL這邊SPI數據。發現在數據和LE上有很多毛刺,持續時間達到100ns,PLL的datasheet顯示LE引腳只要持續高電平20ns即可將數據鎖存進PLL,毛刺會干擾數據鎖存。

圖6配置數據抓取結果

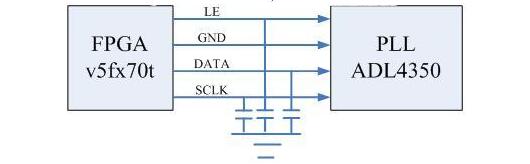

11、在DATA,SCLK管腳上焊接并聯到地的電容,另外在LE引腳也加上并聯到地的電容,以濾除毛刺(如圖)。重新配置,此時抓取的波形顯示已沒有毛刺(如圖8),但是依然無法鎖定。

圖7FPGA與ADF4350控制接入圖示

圖8配置數據抓取結果

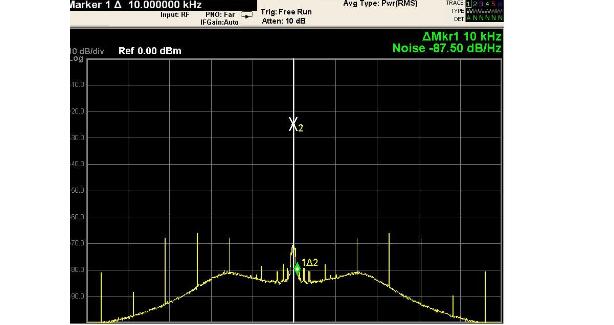

12、重新焊接環路濾波器,鎖定,LED燈亮,輸出3.45GHz信號。測試的相位噪聲結果如下:10KHz的相位噪聲如圖9所示

-76.09dBc/Hz1KHzoffset@3.45GHz

-87.50dBc/Hz10KHzoffset@3.45GHz

圖[font=Verdana]9

10KHzoffset@3.45GHz相位噪聲

三、測試中的注意事項

測試中還遇到了一些其它的問題,在此不一一詳述,現在分享下總結的測試步驟及問題總結。

1.檢查電路連接無誤,排除短路等一些問題。

2.上電,測試電源電壓,電流是否正確,參考時鐘有無輸出。

3.先把ADF4350板子上電,然后進行SPI配置。要注意上電順序相當重要,如果ADF4350和FPGA同時供電,可在程序上作一定的延時來避免同時上電。如果配置沒有結果,可以通過邏輯分析儀來抓取配置數據,分析程序是否正確。如果配置數據無問題,可以在clk,data,le管腳并聯10K的電阻來保證數據能下進ADF4350。

4.如果配置數據沒有問題,輸出鎖定的頻率不正確,很大的可能是環路濾波器焊接的問題,根據調試經驗,這種情況下,大部分都能通過重新焊接來鎖定。

5.因為小數分頻雜散比較大,所以可以選擇整數分頻模式。調試中也進行了相關的實驗,影響不是很大,大家也可以做相關的實驗。

6.參考時鐘的信號質量對芯片的時鐘輸出質量影響很大,所以盡量選用質量好的時鐘源。

7.環路濾波器的帶寬選擇,測試最終選擇了100KHz的環路帶寬,測試中也嘗試了更低的環路帶寬,比如50KHz,但是影響鎖定時間或者無法鎖定。

電子發燒友App

電子發燒友App

評論