1 引言

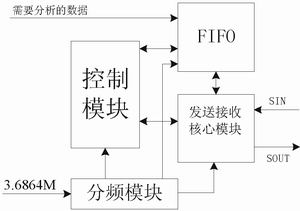

美國德州儀器公司(TI)的TMS320VC54XX系列DSP芯片與PC機實現異步通信通常有兩種方法:第一種是使用通用I/O信號XF和BIO作為串口發送和接收信號,用軟件逐位發送和接收數據,即軟件異步通信方法,這種方法需要占用很多CPU時間,因此,只能在DSP不太忙、實時性要求不高的情況下采用;第二種是通過擴展異步通信芯片來實現高速串行通信,本文選用的就是此方法。

在筆者設計數字調幅廣播系統中的基帶處理子系統時,復用器與信道編碼器之間的通信采用的是異步串行通訊方案。復用器則使用通用PC機來實現,信道編碼器使用TI公司生產的DSP芯片TMS320VC5421來設計實現。

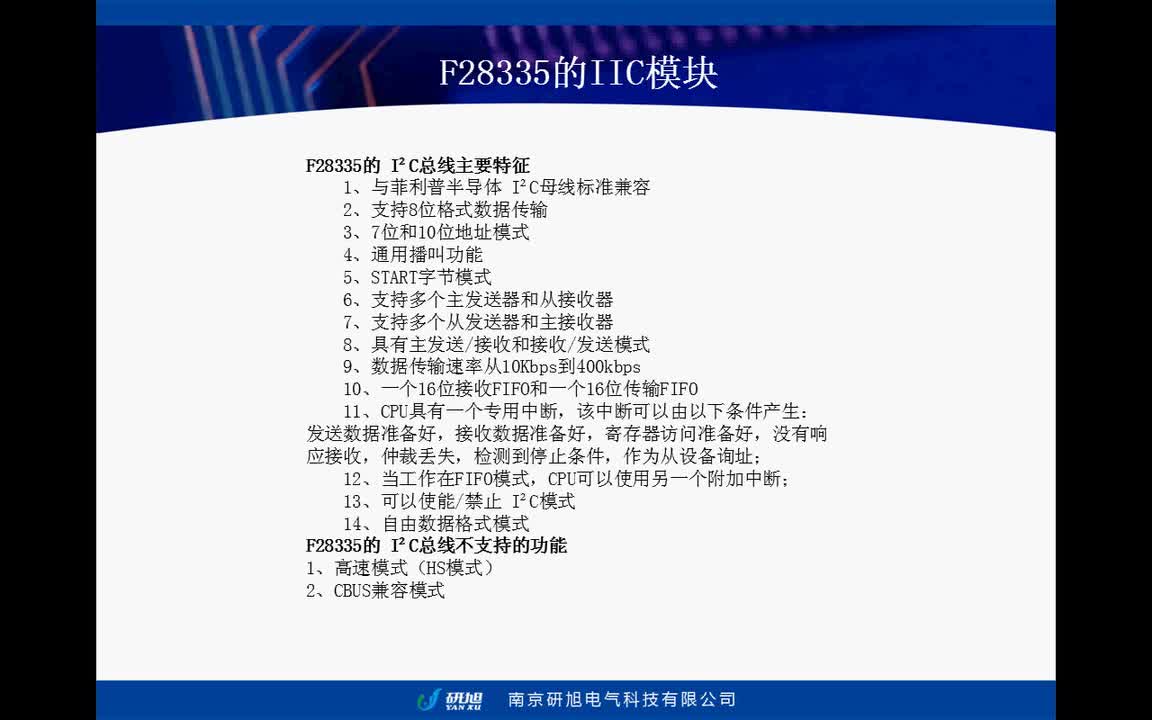

2 UART芯片TL16C752B簡介[1]

2.1 主要特點

TL16C752B是TI公司推出的新型UART(Universal Asynchronous Receiver and Transmitter )收發器。該器件的主要特點如下:

●引腳和ST16C2550兼容,內置兩套UART系統,可獨立工作;

●工作時,最高波特率可以達到1.5Mbps(使用24MHz晶體時)或3Mbps(使用48MHz振蕩器或時鐘源時);

●具有64字節發送/接收FIFO(接收FIFO包含錯誤標志)。由于收、發FIFO的觸發等級可通過軟件編程實現,因而減少了CPU的中斷次數;

●接收FIFO的啟動和停止等級可以通過軟件編程來實現;

●具有兩種控制模式:其中軟件流控制模式可通過編程Xon/Xoff字符來實現;而硬件流控制模式則可通過設置RTS和CTS引腳及相應的寄存器來實現;

●波特率可編程;

●可編程下列串行數據格式:

——5、6、7、8 四種字符;

——數據奇偶校驗或者無校驗;

——1、1.5、2bits 停止位;

●內部閉環。

2.2 TL16C752B的引腳功能

TL16C752B內含雙UART,并自帶64字節收發FIFO,可自動進行軟件流和硬件流控制,最大波特率可達3Mbps。此外,TL16C752B還提供了其它一些增強功能,可通過設定EFR寄存器的相關位來實現。通過FIFO RDY 寄存器可讀取TXRDY/RXRDY引腳的狀態;而通過片內寄存器則可為使用者提供接收數據的錯誤識別、操作狀態以及MODEM的接口控制信號。

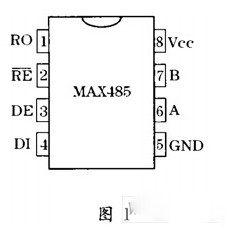

TL16C752B的引腳排列如圖1所示,各主要引腳的功能如下:

A0~A2:地址線,通過這幾個引腳以及讀寫信號IOR和IOW可以訪問及設定片內寄存器?

D0~D7:雙向8位數據線?

CSA、CSB:兩套UART的片選信號?

TXA/RXA、TXB/RXB:分別表示所要發送和接收的數據端口?

INTA/INTB:中斷信號?

RESET:芯片復位信號?

XIN/XOUT:時鐘輸入/輸出信號。

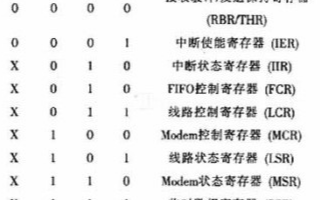

2.3 TL16C752B的內部寄存器

圖2所示是TL16C752B的內部功能模塊圖,該器件內部共有20個寄存器,這些寄存器可分別用于實現通信參數的設置、對線路及MODEM狀態的訪問、數據的發送和接收以及中斷管理等功能。其地址可分別通過A0~A2地址線和某些寄存器的特定位來確定,由于有些寄存器的地址是重疊的,所以還必須通過讀/寫信號加以區分。TL16C752B內部寄存器的映射如表1所列。表中:

“*” 表示僅當LCR的第7位為1時,訪問DLL/DLH。

“** ”表示僅當LCR為0xBF時,訪問EFR以及Xon1/2,Xoff1/2。

“+” 表示當EFR[4]為1,且MCR[6]為1時,訪問TCR/TLR。

“++”表示當片選信號有效、MCR[2]為1且處于非閉環模式時,訪問 FIFO RDY。

此外,對于MCR[7],只有當EFR[4]為1時才可以更改。在上述說明中,[]表示該寄存器的第幾位。

表1 TL16C752B的內部寄存器映射表

| A[2] | A[1] | A[0] | 讀 模 式 | 寫 模 式 |

| 0 | 0 | 0 | 接收保持寄存器(RHR) | 發送保持寄存器(THR) |

| 0 | 0 | 1 | 中斷使能寄存器(IER) | IER |

| 0 | 1 | 0 | 中斷標示寄存器(IIR) | FIFO控制寄存器(FCR) |

| 0 | 1 | 1 | 線路控制寄存器(LCR) | LCR |

| 1 | 0 | 0 | MODEM控制寄存器(MCR) | MCR |

| 1 | 0 | 1 | 線路狀態寄存器(LSR) | LSR |

| 1 | 1 | 0 | MODEM狀態寄存器(MSR) | MSR |

| 1 | 1 | 1 | 臨時寄存器(SPR) | SPR |

| 0 | 0 | 0 | *除數鎖存低位(DLL) | DLL |

| 0 | 0 | 1 | *除數鎖存高位(DLH) | DLH |

| 0 | 1 | 0 | **增強功能寄存器(EFR) | EFR |

| 1 | 0 | 0 | ** Xon-1字符值 | Xon-1字符值 |

| 1 | 0 | 1 | ** Xon-2字符值 | Xon-2字符值 |

| 1 | 1 | 0 | ** Xoff-1字符值 | Xoff-1字符值 |

| 1 | 1 | 1 | ** Xoff-2字符值 | Xoff-2字符值 |

| 1 | 1 | 1 | +傳輸控制寄存器(TCR) | TCR |

| 1 | 1 | 0 | +觸發等級寄存器(TLR) | TLR |

| 1 | 1 | 1 | ++FOFO狀態寄存器(FIFO RDY) | FIFO RDY |

2.4 TL16C752B工作流控制模式

TL16C752B有2種工作流控制模式:硬件流控制和軟件流控制。使用前者可降低軟件消耗,通過RTS和CTS引腳信號的硬件連接可自動控制串行數據流,從而提高系統的有效性;后者則通過使用可編程的Xon/Xoff字符來自動控制數據傳輸。本文主要介紹軟件流控制模式。

軟件流控制模式的使能可通過EFR和MCR這2個寄存器來實現。不同流模式的組合如表2所列(可通過設定EFR的低4位實現)。

表2 軟件流控制模式

| EFR[3] | EFR[2] | EFR[1] | EFR[0] |

TX RX軟件流控制組合模式 |

| 0 | 0 | X | X | 無發送流控制 |

| 1 | 0 | X | X | 發送Xon1,Xoff1 |

| 0 | 1 | X | X | 發送Xon2,Xoff2 |

| 1 | 1 | X | X | 發送Xon1,Xoff1;Xon2,Xoff2 |

| X | X | 0 | 0 | 無接收流控制 |

| X | X | 1 | 0 | 接收器比較Xon1,Xoff1 |

| X | X | 0 | 1 | 接收器比較Xon2,Xoff2 |

| 1 | 0 | 1 | 1 | 發送Xon1,Xoff1;接收器比較Xon1,Xoff1;Xon2,Xoff2 |

| 0 | 1 | 1 | 1 | 發送Xon2,X0ff2;接收器比較Xon1,Xoff1;Xon2,Xoff2 |

| 1 | 1 | 1 | 1 | 發送Xon1,Xoff1;Xon2,Xoff2;接收器比較Xon1,Xoff1;Xon2,Xoff2 |

| 0 | 0 | 1 | 1 | 無發送流控制;接收器比較Xon1,Xoff1;Xon2,Xoff2 |

具體工作流程(從接收的角度)為:接收時,若操作達到接收中斷等級,則產生中斷,但這時傳輸還在進行(這里假設中斷有一定延時);而當RHR中的數據數目達到接收停止等級規定的數值時,接收端發送Xoff1/2,以通知發送端停止發送數據,這時接收端將讀取RHR中的數據。當RHR中的數據數目降到接收啟動等級規定的數值時,接收端發送Xon1/2,以通知發送端可以繼續發送數據。

3 TL16C752B與PC的通信電路

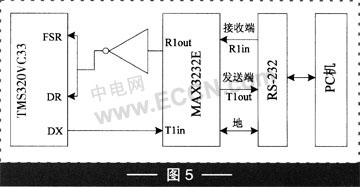

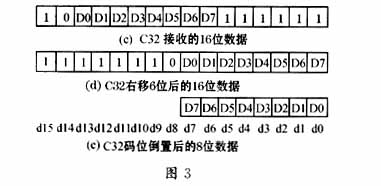

TL16C752B與PC的串行通信部分的硬件連接電路如圖3所示。圖中,地址線A0~A2、數據線D0~D7分別和DSP的地址總線A0~A2、外部數據線D0~D7直接相連,而選通信號CSA/CSB、讀寫信號IOR/IOW、復位信號RESET以及中斷信號INTA/B則接入CPLD并由CPLD處理。同時DSP端的PS、DS、IS、IOSTRB、R/ W、MSTRB也同時接入CPLD以用于生成控制信號。電路中使用CPLD一方面可以對UART的地址靈活配置,另一方面也可以靈活生成UART的復位、選通和讀寫信號,從而增強系統的靈活性,方便系統調試。

由于PC端串口采用RS232電平標準,因此UART之后需要連接MAX3221以完成電平轉換。TL16C752B的數據發送引腳和數據接收引腳分別與MAX3221的數據輸入引腳和數據輸出引腳連接。這里只使用一套UART來完成TL16C752B和PC的通信。數據收、發采用中斷方式,UART_INTA通過CPLD和TMS320VC5421的外部中斷INT0相連接。而3.072MHz晶振則連接到XIN和XOUT兩引腳。波特率設定為38400,故DLL/DLH分別為06和00h。

具體調試時,可先從查詢方式開始,若沒有問題,再使用中斷方式。

圖3

4 TL16C752B和PC通信的軟件編程

該系統的軟件設計部分主要包括PC機程序、DSP初始化、TL16C752B初始化和數據發送/接收以及雙方的通信協議等。下面介紹TL16C752B的初始化程序。

TL16C752B初始化程序主要包括以下幾部分:

(1)波特率的設定;

(2)增強功能的使能及設置EFR的相關位;

(3)完成有關收、發FIFO的設定,主要是MCR/TCR/TLR 3個寄存器的設置;

(4)軟件流控制模式使能以及Xon/Xoff字符的設置;

(5)傳輸數據格式設定,包括8位數據位、2位停止位、DMA傳輸模式1、偶校驗、不使用強制校驗模式、暫停控制位無效等;

(6)設置FIFO控制以及中斷控制寄存器。

此外,在完成設置前,還應注意以下幾點:

(1) 設定DLL和DLH前,LCR[7]應為1。

(2) 設定MCR前,EFR[4]應為1,LCR應為00h。地址相重疊的寄存器不能同時使能。

(3) 讀寫RHR和THR時,由于DSP的讀寫速度很快,故最好不要連續讀寫,而是在每讀、寫一次后延時一段時間,然后再進行下一次讀寫。

(4) 這里,DMA只是一個名稱,而并非是 “直接存儲器訪問”。

TL16C752B的地址分配在I/O空間的0020h~0027h,讀寫通過PORTR和PORTW指令完成。TL16C752B初始化程序如下:

ini_uart_start:

;設置 baud rate=38400 ; divi-sor=0006h

stm #temp1_reg,ar1

nop

st #80h;*ar1 ;除數鎖存使能 LCR=bfh

portw *ar1,#k_LCR_addr

st #k_DLL_value,*ar1

portw *ar1,#k_DLL_addr

st #k_DLH_value,*ar1

portw *ar1,#k_DLH_addr

;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;

st #k_LCR_value?*ar1 ;LCR=bfh

portw *ar1,#k_LCR_addr

st #k1 EFR value?*ar1 ;增強功能使能

portw *ar1,#k_EFR_addr

st #0,*ar1 ;設定LCR= 0

portw *ar1?#k LCR addr

st #k_FCR_value,*ar1 ;設定FIFO控制寄存器

portw *ar1,#k_FCR_addr

st #k_MCR_value,*ar1 ;設定MCR/TCR/TLR寄存器

portw *ar1,#k_MCR_addr

st #k_TCR_value,*ar1

portw *ar1,#k_TCR_addr

st #k_TLR_value,*ar1

portw *ar1,#k_TLR_addr

st #k1_MCR_value,*ar1

portw *ar1,#k_MCR_addr

st #k_LCR_value,*ar1 ;為訪問Xon/Xoff/EFR,LCR重設定為BFh

portw *ar1,#k_LCR_addr

st #k_Xoff1_value,*ar1 ;設置軟件流控制

portw *ar1,#k_Xoff1_addr

st #k_Xon1_value,*ar1

portw *ar1,#k_Xon1_addr

st #k_Xoff2_value,*ar1

portw *ar1,#k_Xoff2_addr

st #k_Xon2_value,*ar1

portw *ar1,#k_Xon2_addr

st #k_EFR_value,*ar1 ;設置軟件流控制組合方式

portw *ar1,#k_EFR_addr

st #k_LCR_dlatch_disable,*ar1

portw *ar1,#k_LCR_addr ;設定傳輸數據格式

st #k_IER_value,*ar1 ;設置中斷

portw *ar1,#k_IER_addr

5 結束語

通過擴展串口完成TMS320VC5421與PC機串行通信硬件接口比較簡單、數據傳送距離遠、使用經濟。該電路及其軟件經與微機的通信實驗證明,在波特率為38400時,能夠可靠地實現與PC機的通信。

電子發燒友App

電子發燒友App

評論