網絡測試 NetWork 分析儀

2024-03-14 22:30:52

ADXRS910AWBRGZ-RL 特性高性能、層內滾動速率陀螺儀溫度補償,高精度偏移和靈敏度性能陀螺儀噪聲:2°/s rms(最大值)16位數據字串行端口接口(SPI)數字輸出靜態功耗:

2024-02-26 11:06:37

目前用到以下的電源芯片,請問以下的芯片thermalpad 是否需要加過孔到gnd層呢,還是直接在top層直接連接到地網絡:

如果在thermalpad 上打過孔,應該打幾個

LT3042

2024-01-05 08:25:19

薄TEM薄片+TEM觀察分析對于芯片膜層很薄的結構層,一般是幾個納米的芯片膜厚,透射電鏡TEM分辨率比SEM高,透射電子顯微鏡的分辨率比光學顯微鏡高的很多,可以達到0.1~0.2nm,放大倍數為幾萬

2024-01-02 17:08:51

厚度建議全部采用1oZ,厚度為1.6mm。

板厚推薦疊層如下圖(上)所示(8層通孔1.6mm厚度推薦疊層),阻抗線寬線距如下圖(下)所示(8層通孔1.6mm厚度各阻抗線寬線距)。

10層1階HDI

2023-12-25 13:48:49

厚度建議全部采用1oZ,厚度為1.6mm。

板厚推薦疊層如下圖(上)所示(8層通孔1.6mm厚度推薦疊層),阻抗線寬線距如下圖(下)所示(8層通孔1.6mm厚度各阻抗線寬線距)。

10層1階HDI

2023-12-25 13:46:25

具體分析,我們來看看以下兩個只設計1個接地層的6層板分層方案,分析只有1個接地層時,會帶來哪些不好的影響。

方案一: 該方案的問題是電源層和地層相隔較遠,中間隔了兩個信號層。所以其電源與地的耦合比較

2023-12-08 10:49:19

具體分析,我們來看看以下兩個只設計1個接地層的6層板分層方案,分析只有1個接地層時,會帶來哪些不好的影響。

方案一: 該方案的問題是電源層和地層相隔較遠,中間隔了兩個信號層。所以其電源與地的耦合比較

2023-12-08 10:34:06

AD9164 JESD204B接口的傳輸層是如何對I/Q數據進行映射的

2023-12-04 07:27:34

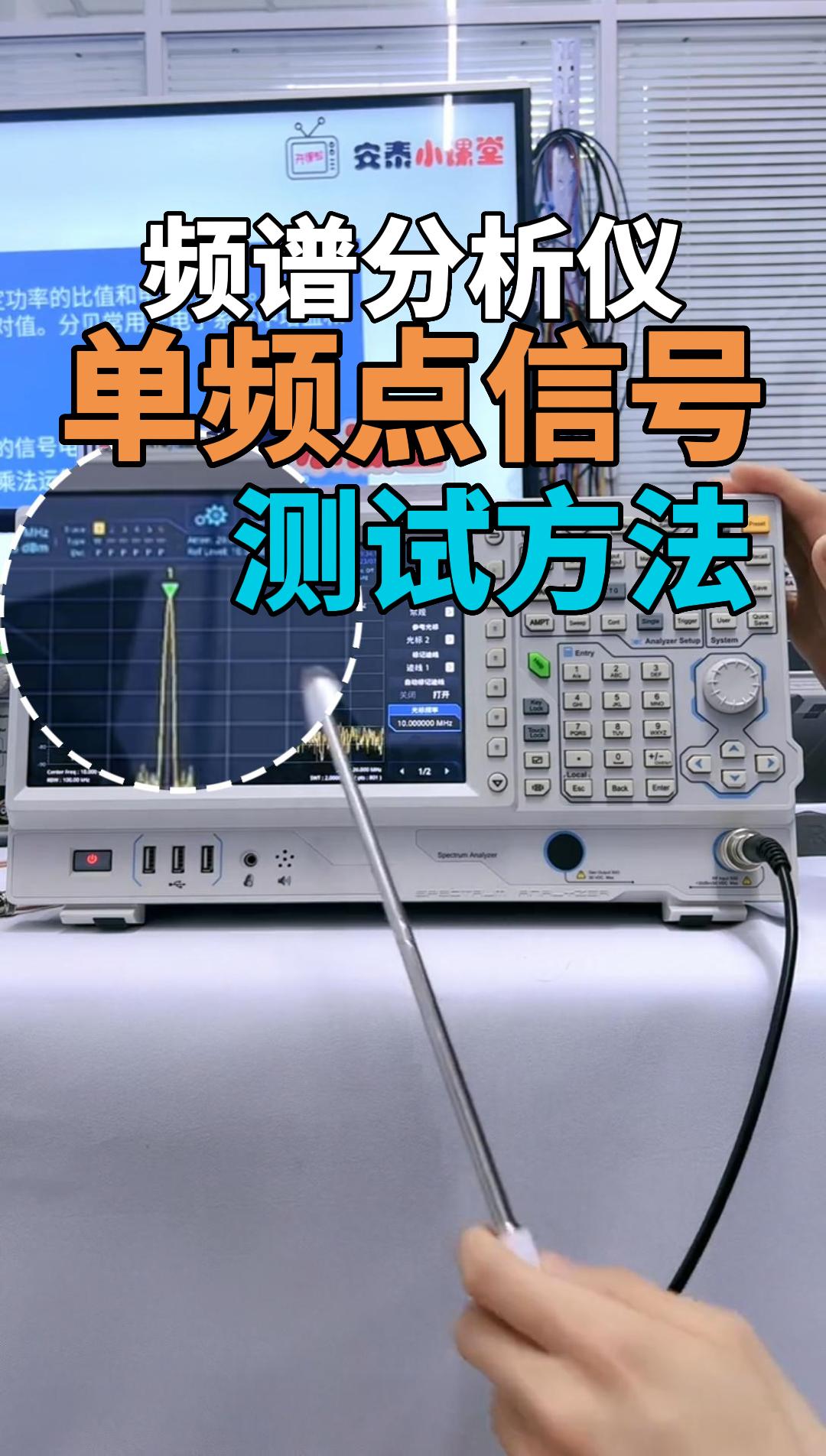

想畫出設計的電路THD值,隨頻率增益變化的曲線,怎么用分析儀測量。

2023-11-17 06:05:15

最近改了幾組電機線(3相線+接地線+屏蔽層):

1、地線電機與變頻器端都已經接地;

2、屏蔽層入柜處接地;

運行一天下來,發現以下幾個現象:

1、如果將屏蔽層在入柜處接地,電機在運行過程中,間隔

2023-11-13 07:50:31

PCB設計時,在那種情況下會使用跨層盲孔(Skip via)的設計?一般疊構和孔徑怎么設計?

2023-11-09 16:21:10

請問帶顯示的和不帶顯示的USB邏輯分析儀的原理是什么 有沒有開源的資料分享?上位機分析軟件都是專用的嗎?

2023-11-09 06:48:01

在以TCP/IP5層模型中,應用層是如何與傳輸層連接的 “封裝”又是指什么?顯示全部

2023-10-28 06:53:10

OPVXG便攜式網絡綜合協議分析儀 1-7層網絡全面透視,有線、無線集成式測試,網絡負載、壓力、吞吐量。。。全面的網絡故障診斷和數據包捕捉,現貨庫存。產品型號說明

2023-10-16 09:41:49

pcb裸銅的logo放在哪一層?

2023-10-16 07:29:19

紙張層間剝離強度試驗儀層間結合強度是指紙或紙板抵抗層間分離的能力,是紙張內部粘結能力的反映。強度較低會導致紙張和紙板,在使用粘性油墨印刷時出現拉毛問題,強度過高會給紙張的生產加工帶來難度,同時加大了

2023-10-12 16:40:13

邏輯分析儀測的波形是亂的

2023-09-27 07:07:13

復合膜層間剝離試驗機 復合膜剝離力測試儀是一款專業用于測試復合膜、薄膜等相關材料剝離強度的儀器。該儀器采用先進的電子測量技術,能夠快速、準確地測定復合膜或薄膜材料的剝離力。該設備主要由主機

2023-09-20 15:29:25

4層藍牙產品PCB設計素材

2023-09-20 07:43:16

我們的應用層和內核層是不能直接進行數據傳輸的。我們要想進行數據傳輸,要借助下面的這兩個函數。

static inline long copy_from_user(void *to, const

2023-08-29 09:54:29

如煙笑著說討厭。

趙理工,在七夕前一天投了一個板,一個8層,2.0mm的軟硬結合板。軟板2層,硬板是6層,內層銅厚1OZ,線寬線距沒有走極限,且都滿足工藝能力,疊層如下:

從疊層中,我們可以看出

2023-08-22 16:48:12

的分析方法。利用干涉儀圖樣的分析,可以直接獲得相關參數(如膜層厚度、表面粗糙度、膜層折射率等),從而得到準確的測量結果。

2、對于非同質材料,由于其光學特性的差異性,分析方法相對更為復雜,通常需要借助

2023-08-21 13:46:12

在兩個 tensorflow 模型上運行模型優化器,其中包含一個ctc_greedy_decoder和tf.keras.backend.ctc_decode的 CTC 層

這兩個錯誤均未

2023-08-15 08:26:07

在 OpenVINO? 工具套件 2021.4 中使用 IENetwork.層 。

收到錯誤:openvino.inference_engine.ie_api。IENetwork 對象沒有屬性“層”

2023-08-15 06:41:56

類型的不同,各參數的最佳工藝存在差異。 在恒壓模式下,隨電壓的升高,氧化膜生長速率增大,膜層厚度、表面孔隙率及防腐性均增加,

2023-07-19 16:45:41

使用NUC970 官網自帶的mtd層nuc970_nand.c 驅動,硬件BCH ECC 已正確開啟,如何制造一個nandflash 層ECC錯誤,并觸發數據糾錯,有什么辦法? 有沒有誰做過類似測試的。

2023-06-27 15:09:52

“ 不同EDA對于PCB中物理層的定義基本相同,比如信號層、絲印、阻焊、助焊等。但對于工藝層(輔助層)的定義會略有不同,比如Altium Designer沒有專門的板框層及Courtyard層,通常

2023-06-21 12:13:20

?“ 使用Allegro的小伙伴應該很清楚Courtyard層的用法,但使用Altium Designer的小伙伴可能對Courtyard層完全沒有概念。Courtyard層到底是什么?在KiCad

2023-06-13 13:01:24

)。

添加Logo或其他圖形(也可以在絲印層)。

在阻焊層上添加文本或圖形,可能不如絲印層引人注目。露銅的文字或圖形看起來是不是很酷,取決于銅的表面處理方式。與絲印層相比,阻焊層可以做到更高的分辨率

2023-06-12 11:03:13

我的客戶需要在 i.MX8mini ( iMX8MMINI ) 上有一個可用的 AVS SDK,我發現了以下可能適合的元層:

https://github.com/nxp-imx-support

2023-06-08 06:45:15

頻域上去分析。時域的話,雷豹已經在信號眼圖上有對比過了,那么想繼續分析這個串擾的改善的話,就有在頻域上去做文章了。

Chris對雷豹調整疊層前后的走線結構進行建模,利用cadence的3D

2023-06-06 17:24:55

“ 經常看到小伙伴們詢問KiCad中的Margin層有什么用,和板框層Edge.Cut有什么區別?雖然實際實際中可以完全忽略Margin層,但理解它并合理的加以使用,可以為設計帶來一定的便利

2023-06-06 09:46:43

。內層的加工成本相同,但敷箔/核結構明顯的增加外層的處理成本。

奇數層PCB需要在核結構工藝的基礎上增加非標準的層疊核層粘合工藝。與核結構相比,在核結構外添加敷箔的工廠生產效率將下降。在層壓粘合以前

2023-06-05 14:37:25

為了比demo板有更好的成本優勢,在設計上使用了相鄰層走線的這個方法,也就是我們所說的GSSG的疊層結構,這樣的話的確在層數上可以省下幾層,但是就會帶來其他方面的一些壞處。雷豹一直都是在關注走線

2023-06-02 15:32:02

電解質支撐,但是歐姆電阻很大,正常在1以內,我的歐姆電阻4-15甚至更多,開路電壓可以達到1V,集流層采用銀乙醇,想知道怎么改進?謝謝,這個是燒后的SOFC

2023-05-20 16:46:05

的PCI Express Gen6,也開始采用了多通道技術。 安立的信號質量分析儀-R MP1900A系列是一款具備8個模塊插槽的高性能BERT,通過PPG/ED、及抖動/噪聲發生器等擴展測量

2023-05-17 17:59:55

的PCI Express Gen6,也開始采用了多通道技術。 安立的信號質量分析儀-R MP1900A系列是一款具備8個模塊插槽的高性能BERT,通過PPG/ED、及抖動/噪聲發生器等擴展測量

2023-05-17 17:57:44

的PCI Express Gen6,也開始采用了多通道技術。 安立的信號質量分析儀-R MP1900A系列是一款具備8個模塊插槽的高性能BERT,通過PPG/ED、及抖動/噪聲發生器等擴展測量

2023-05-17 17:54:39

由于運輸 SAM 要求高性能,客戶希望在做出決定之前看到一些預測試。我們與唯冠 DFAE 合作開發 SW 小程序。SAM卡中的這個小程序可以按照客戶算法進行辦理和充值交易。

交易時間是客戶可以接受的。所以客戶研發團隊已經完成了JCOP4.5 中的applet 移植。

2023-05-08 08:28:35

在多層電路板里是不是所有電源都必須放在內電層呢?

2023-05-06 10:20:36

PCB四層板的電源和地的內層到底怎么布線?

2023-05-06 10:19:18

PCB 四層板里面的電源層和地層是什么意思,或者多層板里面的電源層和地層是什么意思?

我只是把四層板里面的中間兩層當做是裝換的或連接的,為什么教材里面說是電源層和地層呢?

2023-05-06 10:15:14

1.PCB中,兩個不同電壓的電源層可以共用一個地層嗎?

2.如果可以共用地層的話,對于兩個不同電壓的電源層是各自用一個地層好,還是共用一個地層好?

3. “兩個電源層:3.3V,2.1V; 兩個信號層 ;地層” 怎樣布局最好?

2023-05-06 10:12:52

我們正致力于為基于 IMX8MPlus 的定制板開發 Windows IOT 支持。我們使用 DP83867 以太網物理層代替 IMX8MPlus 板中使用的 RTL8211F 以太網物理層。

我們

2023-05-06 07:34:35

我建板s32g274ardb2,它可以制作圖像。現在我想向項目添加新層,所以我設置了新的 layaer meta-mylayer,我創建了 .bb .c 和 makefile。

然后我將

2023-04-25 09:59:34

層將再次被“百分比覆蓋率”方法,假設的50%的銅覆蓋和1盎司/ ft2(35μm)厚度。第4層仍然和以前一樣不連接到任何一個器件。 因此,4層結構總結在圖8中。層4仍然是一個覆蓋整個底面的固體平面

2023-04-21 15:04:26

4.3.6 實驗設計6:一個4層的PCB板與熱散熱過孔 為了完整性,“4層+散熱過孔”結構也被實驗設計為1層銅的幾個尺寸,并再次疊層,如圖8所示。結果如圖13所示。 (1)單層板。 (2

2023-04-21 14:51:37

SDK 軟件組件和抽象層文檔

2023-04-21 07:18:06

走線組成,而不是大型連續面積。對這些層進行詳細的實驗設計顯然是不可行的,因此采用了“百分比覆蓋率”方法。采用這種方法,計算出結構的平均電導率,以銅層厚度占總面積的百分比計算。這些實驗設計的目的,我們將

2023-04-20 17:10:43

我遇到了一個與 meta-rust 層相關的 I.MX yocto 構建錯誤,這是我之前在 bitebake 構建過程中沒有看到的。在它下面是錯誤線, 錯誤:任務(虛擬:本機:/home/dand

2023-04-20 08:49:07

4層PCB是一種常見的多層PCB類型,具有多種用途。您是否有興趣了解更多關于它們的信息,特別是它們的堆棧設計和類型?它們的優點是什么,與2層PCB相比如何?

2023-04-14 15:38:20

功率分析儀進行諧波測試是采用FFT算法還是其他算法呢?

2023-04-13 11:09:35

PCB四層板中我將中間兩層設置成了信號層,能否給點實用的布線的經驗???當布完線后該怎么進行敷銅呢?需要在哪層進行敷銅,最好是能說說為啥。如果將中間層設置成電源層和地層,那中間層還能走信號線嗎???需要注意些什么???在此謝過。。。。

2023-04-11 17:33:46

多層PCB如何定義疊層呢?

2023-04-11 14:53:59

請教一下大神PCB多層板為什么都是偶數層呢?

2023-04-11 14:52:31

將BLE抽象層添加到新項目的正確方法是什么,應該從哪里下載抽象。

2023-04-11 07:06:33

PCB板阻抗設計:阻抗線有無參考層阻抗如何變化?生產PCB時少轉彎的阻抗線的阻抗更容易控制穩定性?

2023-04-10 17:03:31

矢量網絡分析儀串擾如何測試,設備如何設置

2023-04-09 17:13:25

看到有f.cuf.adhes f.paste f.silks f.mask dwgs.user cmts.user eco1.user margin 有這些預定義的層,分別代表什么意思呢?分別在什么時候用呢?

2023-04-02 17:58:34

FPC基本結構材料介紹 從撓性印制線路板的基本結構分析,構成撓性印制線路板的材料有絕緣基材、膠粘劑、金屬導體層(銅箔)和覆蓋層 。 01.銅箔基板(Copper Film) 銅箔:基本分

2023-03-31 15:58:18

大家好,我正在研究 VAR-SOM IMX8,我正在構建 Qt5 圖像,yocto 版本是dunfell-fslc-5.4-2.1.x-mx8-v1.5。當我嘗試將 meta-webkit 層添加到

2023-03-30 07:45:15

我正在研究 MBDT 中 BMS 與新 S32K344 和 MC33775 與先前版本 BMS MC33771 和 MC33664 的集成。我發現最新的 MBDT 使用 MCAL 層通過

2023-03-30 07:05:40

PADS設計4板,第一層基板挖一個大矩形槽,露出第二層基板,再在第二層基板挖一個小矩形槽,嵌套的。請問怎么實現?

2023-03-24 11:16:33

電子發燒友App

電子發燒友App

評論