電子發(fā)燒友網(wǎng):不管您是否注意到,我們正被各類被廠商冠以“智能”概念的產(chǎn)品圍繞著,無處不在!智能,也成了激發(fā)工程師創(chuàng)意靈感的新源泉。2013年,我們都走在智能化的道路上。智能地球、智能能源、智能交通、智能工業(yè)、智能電網(wǎng)、智能醫(yī)療、智能通信、智能家居、智能互聯(lián)等智能化概念,層出不窮。智能化大潮正以迅雷不及掩耳之勢,席卷全球半導(dǎo)體大市場及各細(xì)分產(chǎn)業(yè)鏈。智能化創(chuàng)新正如春風(fēng)化雨般沐浴著每一個人。誰都“逃”不掉!賽靈思再次抓住了大勢發(fā)展新機遇,持28nm已領(lǐng)先競爭對手整整一代之力,再蓄以勢如破竹之勢,開創(chuàng)可編程邏輯軟硬件平臺智能化創(chuàng)新的新世界。

嵌入式系統(tǒng)的未來:更智能的專業(yè)化軟硬件平臺

未來的嵌入式系統(tǒng)將需要數(shù)以百計的Gops實時計算和Gbps通信帶寬,以滿足多通道無線射頻、數(shù)據(jù)中心安全設(shè)備、嵌入式視覺、Nx100Gbps網(wǎng)絡(luò)等眾多不同產(chǎn)業(yè)應(yīng)用需求。與此同時,這些組件也必須滿足嚴(yán)格的功耗要求,并盡可能降低成本。

物聯(lián)網(wǎng)將進(jìn)一步增加共享、處理和存儲的“大數(shù)據(jù)”的絕對數(shù)量。這就產(chǎn)生了更智能化嵌入式系統(tǒng)的全球需求,這種系統(tǒng)也將為我們的日常工作生活提供充分的資訊,讓我們能夠做出更好更明智的決策。

賽靈思公司資深副總裁兼CTO Ivo Bolsens

近年來,系統(tǒng)設(shè)計人員一直在從單處理器向多核并行計算平臺轉(zhuǎn)移,以不斷提高計算效率,滿足嚴(yán)格的性價比和功耗要求。兒提高計算效率的關(guān)鍵步驟在于專業(yè)化,也就是各種計算單元和互聯(lián)基礎(chǔ)架構(gòu)可以滿足特定的應(yīng)用要求,從而實現(xiàn)高度優(yōu)化的異構(gòu)多核架構(gòu)。

靈活、高度集成的全新系列器件平臺將會因此而問世,系統(tǒng)專家可以采用軟件編程流程對器件進(jìn)行編程,軟件設(shè)計流程不僅能捕獲各種應(yīng)用特性,而且還可將這種高級描述語言嵌入到專業(yè)化的可編程架構(gòu)中。

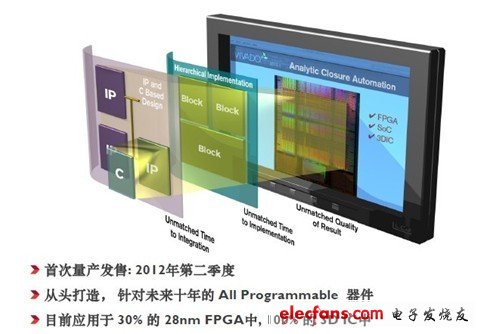

2012年,賽靈思推出了全球首款A(yù)ll Programmable SOC平臺,結(jié)合了嵌入式處理器軟件可編程功能和FPGA硬件靈活性。 Zynq?-7000器件系列在一個高密度、可配置的互聯(lián)模塊網(wǎng)絡(luò)中, 把多ARM ?核、可編程邏輯結(jié)構(gòu)、DSP數(shù)據(jù)路徑、存儲器和I/O完美集成在一起。這個協(xié)同處理器可以采用賽靈思新一代Vivado?設(shè)計套件工具鏈中獨特的高層次綜合功能進(jìn)行C語言的編譯。

這個突破 是產(chǎn)業(yè)向以系統(tǒng)為中心的設(shè)計流程發(fā)展的一個重大里程碑,新的設(shè)計流程將充分利用并行編程、高層次綜合和SoC多核技術(shù)領(lǐng)域的最先功能。這種以軟件為中心的編程流程可充分挖掘?qū)I(yè)化硬件架構(gòu)的全部潛能,同時又不需揭示硬件的實現(xiàn)細(xì)節(jié)。

All Programmable SOC 軟硬件協(xié)同平臺將讓眾多領(lǐng)域的不同工程師均能受惠于Zynq All Programmable SoC架構(gòu)的全部功能,使他們能夠在設(shè)計新一代更智能的電子系統(tǒng)時,實現(xiàn)最高的生產(chǎn)力和最佳的結(jié)果質(zhì)量。

?

2.5D封裝+28nm,F(xiàn)PGA迎來革命性突破

68億只晶體管、1,954,560個邏輯單元(容量相當(dāng)于市場同類最大28nm FPGA的兩倍)、305,400個CLB切片的可配置邏輯塊(CLB)、21,550Kb的分布式RAM容量、以及2,160個DSP slice、46,512個BRAM、24個時鐘管理模塊、4個PCIe模塊、36個GTX收發(fā)器(每個性能達(dá)12.5 Gbps)、24個I/O bank和1,200個用戶I/O、19W功耗……是的,您沒有看錯,這一連串令人眼花繚亂的數(shù)字,就是賽靈思(Xilinx)日前宣布可正式供貨的“世界最大容量”FPGA Virtex-7 2000T為我們呈現(xiàn)出的令人震撼的性能指標(biāo)。

2010年10月,Xilinx高調(diào)宣布推出業(yè)界首項堆疊硅片互聯(lián)技術(shù)(SSI,Stack Silicon Interconnect)。該公司全球高級副總裁兼亞太區(qū)執(zhí)行總裁湯立人強調(diào)說,之前曾有廠商試圖通過將兩個或多個FPGA進(jìn)行邏輯互聯(lián),創(chuàng)建出更大型的“虛擬FPGA”,最終實現(xiàn)復(fù)雜設(shè)計。但往往由于可用I/O數(shù)量有限,再加之FPGA間信號傳輸造成的時延限制性能,以及使用標(biāo)準(zhǔn)的器件I/O來創(chuàng)建多個FPGA之間的邏輯連接增加功耗等因素,這些努力都宣告失敗。而SSI技術(shù)的核心則來自于賽靈思專利的ASMBL架構(gòu)、微凸塊技術(shù)以及TSMC的硅通孔(TSV)技術(shù)。

2.5D SSI的主要技術(shù)突破

Virtex-7 2000T是Xilinx采用臺積電(TSMC)28nm HPL工藝(低功耗高介電層金屬閘技術(shù))推出的第三款FPGA。更重要的是,這將是“世界上第一個采用SSI技術(shù)的商用FPGA”。賽靈思方面將該項技術(shù)命名為2.5D SSI。湯立人堅持認(rèn)為,2.5D并不意味著就比傳統(tǒng)意義上的3D封裝性能差。事實上,如果將邏輯單元與內(nèi)存進(jìn)行垂直堆疊(Vertical Stacking),也就是所謂的3D封裝,現(xiàn)在面臨著散熱、RAM/Logic等有源層之間因為膨脹系數(shù)不同,導(dǎo)致內(nèi)部應(yīng)力不均,影響晶體管性能等多項重要挑戰(zhàn)。“賽靈思同樣看好不帶中介層的完全3D IC堆疊技術(shù)前景,但從目前來看,該技術(shù)在整個產(chǎn)業(yè)中實現(xiàn)標(biāo)準(zhǔn)化還要花更長的時間。”

“我們的2.5D SSI結(jié)構(gòu)采用并排式芯片布局,將4個經(jīng)ASMBL架構(gòu)優(yōu)化的FPGA Slice 并排排列在硅中介層上,Slice之間擁有超過10,000個過孔走線,時延僅為1納秒。然后再通過微凸塊將硅片連接至硅中介層。”湯立人進(jìn)一步解釋說, “由于采用的是大量低延時、芯片間互連,并連接至球形柵格陣列,從而也避免了垂直硅片堆疊方法出現(xiàn)的熱通量和設(shè)計工具流問題。”

肉搏開始了!賽靈思28nm 7系列FPGA加速取代ASIC!

如果把FPGA與ASIC之間的競爭看成一場戰(zhàn)斗,那么目前這場戰(zhàn)斗正從遠(yuǎn)觀、叫陣、近戰(zhàn)發(fā)展到它的最后階段――肉搏!6月22日,賽靈思基于統(tǒng)一架構(gòu)的28nm 7系列FPGA閃亮登場,本次發(fā)布的FPGA新品最大的亮點是功耗大幅度降低,同時性能、容量大幅提升!“7系列最大的目標(biāo)是降低功耗!整個系列功耗降低50%!”在新聞發(fā)布會上,賽靈思公司質(zhì)量管理和新產(chǎn)品導(dǎo)入全球高級副總裁亞太區(qū)執(zhí)行總裁湯立人(Vincent Tong) 指出,“同時容量大大提升,高達(dá)200萬個邏輯單元!除了取代高端ASIC,7系列FPGA還將瞄準(zhǔn)更多新興應(yīng)用。”

不再回避功耗、尺寸敏感話題

和以前FPGA叫板ASIC的策略不同,這次賽靈思不再強調(diào)FPGA的靈活性了(或許大家早認(rèn)同這個優(yōu)勢了),這次賽靈思選擇了很多FPGA供應(yīng)商想回避的話題的同時也是很多ASIC廠商總拎來打擊FPGA的兩個特性:功耗和尺寸。

“預(yù)計40nm FPGA市場到2014年的規(guī)模可以達(dá)到70億美元,而那時ASIC/ASSP的規(guī)模會是600億美元,如果FPGA要擴(kuò)大規(guī)模,就必須有更低的成本(更高的性價比)、更高的系統(tǒng)性能、更大的容量和更低的功耗,我們認(rèn)為這其中最主要的關(guān)鍵是降低功耗!” 湯立人指出,“我們此次推出的7系列28nm FPGA系列,在系統(tǒng)性能上翻番,同時容量擴(kuò)大兩倍,功耗降低一半,我們預(yù)計28nm 7系列FPGA可以將FPGA市場規(guī)模擴(kuò)大到110億美元!”

與Virtex-6 FPGA 相比,Virtex-7 系列的系統(tǒng)性能翻了一番,功耗降低一半,速度提升30%,該系列產(chǎn)品針對通信系統(tǒng)進(jìn)行了精心優(yōu)化,以最大型的 FPGA 支持最高性能和最高帶寬串行連接功能。Virtex-7 系列包含 Virtex-7T 和 Virtex-7XT 兩個子系列產(chǎn)品,屬于超高端產(chǎn)品之列,在嵌入式收發(fā)器、DSP 切片、存儲器模塊和高速 I/O 的數(shù)量與性能方面將 FPGA 技術(shù)發(fā)揮到了極致,為業(yè)界樹立了新的基準(zhǔn)。

賽靈思20nm技術(shù)戰(zhàn)略Roadmap曝光:繼續(xù)領(lǐng)先一代

“熟悉FPGA行業(yè)和對賽靈思有一定了解的業(yè)界人士都知道,賽靈思在28nm技術(shù)上取得了多項重大突破, 其產(chǎn)品組合處于整整領(lǐng)先一代。基于28nm技術(shù)突破之上的20nm產(chǎn)品系列,必將為創(chuàng)造更高的客戶價值提供了巨大的機會!”11月5日,在賽靈思媒體見面 會上,賽靈思公司全球高級副總裁,亞太區(qū)執(zhí)行總裁湯立人分享了Xilinx 繼續(xù)領(lǐng)先一代的20nm 產(chǎn)品戰(zhàn)略,“此外,下一代FPGA及第二代SoC和3D IC將與Vivado設(shè)計套件‘協(xié)同優(yōu)化’,為行業(yè)提供最具吸引力的ASIC和ASSP可編程替代方案。”

湯立人談起賽靈思領(lǐng)先一代的技術(shù)時非常興奮

強大根基為賽靈思20nm技術(shù)產(chǎn)品繼續(xù)領(lǐng)先一代注入強心劑?

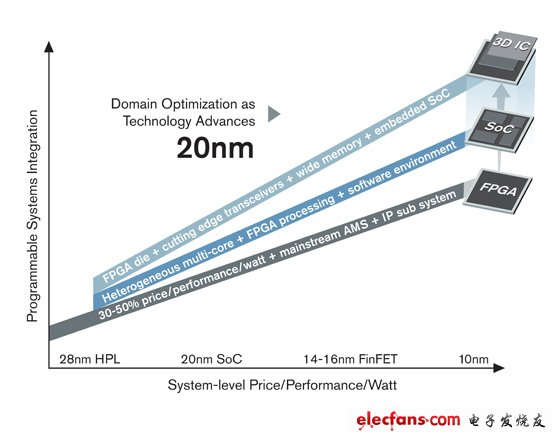

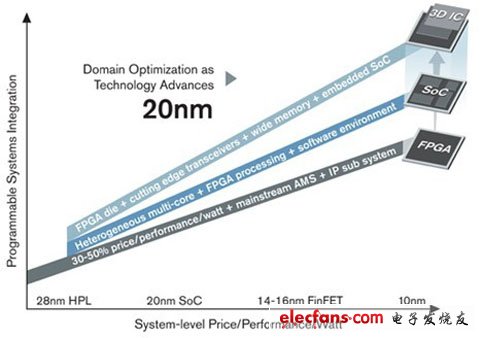

賽靈思在28nm 7系列FPGA的創(chuàng)新,把工藝技術(shù)上的創(chuàng)新(與臺積電(TSMC)共同開發(fā)的高性能低功耗(HPL)技術(shù))與針對最小化靜態(tài)和動態(tài)功耗、最大化主要構(gòu)建模 塊性能的眾多優(yōu)化完美結(jié)合,讓賽靈思能夠提供超越節(jié)點的性能/瓦價值優(yōu)勢。“其20nm產(chǎn)品系列發(fā)展戰(zhàn)略,包括下一代8系列All Programmable FPGA以及第二代3D IC和SoC。20nm產(chǎn)品系列建立在業(yè)經(jīng)驗證的28nm技術(shù)突破之上,在系統(tǒng)性能、功耗和可編程系統(tǒng)集成方面領(lǐng)先競爭企業(yè)整整一代。”湯立人強調(diào),“賽 靈思在 28nm 節(jié)點上推出的多種新技術(shù)為客戶帶來了重大的超前價值,并使賽靈思領(lǐng)先競爭對手整整一代。賽靈思并不是簡單地將現(xiàn)有的 FPGA 架構(gòu)遷移到新的技術(shù)節(jié)點上,而是力求引領(lǐng)多種 FPGA 創(chuàng)新,并率先推出了 All Programmable 3D IC 和 SoC。”

如何擴(kuò)大下一代的競爭優(yōu)勢?

從28nm 7系列FPGA的創(chuàng)新為到20nm8系列FPGA為賽靈思在20nm繼續(xù)保持領(lǐng)先一代的地位奠定了基礎(chǔ)。這些器件將利用與臺積電的28nm HPL工藝性能/瓦特征相似的20nm SoC工藝。將系統(tǒng)級性能提升2倍,內(nèi)存帶寬擴(kuò)大2倍,總功耗降低50%,邏輯功能集成和關(guān)鍵系統(tǒng)建模加速1.5倍多。湯立人表示,“所有應(yīng)用都將受益于 賽靈思的下一代路由體系結(jié)構(gòu),可以輕松地擴(kuò)展超過90%的資源利用率,實現(xiàn)更高的結(jié)果質(zhì)量及更快的設(shè)計收斂。”

怎樣發(fā)現(xiàn)并滿足20nm節(jié)點市場需求?

湯立人強調(diào),“半導(dǎo)體行業(yè)的領(lǐng)導(dǎo)者正在逐步發(fā)現(xiàn)20nm的價值,而且一些設(shè)計已經(jīng)正在進(jìn)行中。”賽靈思公司看到了這個工藝節(jié)點所擁有的巨大潛力,因此也在不斷地探索新的方式,致力于通過28nm已經(jīng)建立且在20nm將繼續(xù)擴(kuò)展的創(chuàng)新技術(shù)持續(xù)發(fā)掘這些潛在的價值。

龐大的20nm市場需求體現(xiàn)在各大熱門應(yīng)用領(lǐng)域,它包括Nx100G有線網(wǎng)絡(luò)、嵌入式視覺、多通道無線射頻、數(shù)據(jù)中心的安全性及交換機應(yīng)用等。賽靈思為滿足市場對20nm技術(shù)產(chǎn)品的需求,再次領(lǐng)先一步,進(jìn)行全面且具前瞻性的市場戰(zhàn)略部署。

20nm FPGA性能進(jìn)一步得到優(yōu)化

湯立人指出,“在20nm,賽靈思目前正在開發(fā)其第二代SoC和3D IC技術(shù),以及下一代的FPGA技術(shù)。相比于競爭對手,賽靈思擁有多年前率先創(chuàng)新的先發(fā)優(yōu)勢。其中包括FPGA性能/瓦的突破,與客戶一起更好微調(diào)的更成 熟的SoC和3D IC技術(shù),與其下一代Vivado設(shè)計套件“協(xié)同優(yōu)化”的器件。”賽靈思在系統(tǒng)中重新定義了高性能收發(fā)器的設(shè)計和優(yōu)化。這讓賽靈思能夠更有效地把20nm 的附加價值引入領(lǐng)先的和業(yè)經(jīng)證明的28nm技術(shù)之中,讓客戶的創(chuàng)新繼續(xù)保持領(lǐng)先一代。

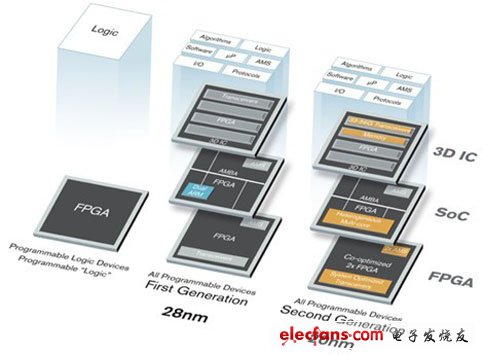

第一代到第二代All ProgrammableSoC#e#

第一代到第二代All ProgrammableSoC

為在20nm繼續(xù)居于領(lǐng)先一代的地位,賽靈思將借助一個新的異構(gòu)處理系統(tǒng),有效地提供更高的系統(tǒng)性能。這個嵌入式系統(tǒng)將被用超過 2倍的互連帶寬耦合到下一代FPGA架構(gòu)中。在芯片上的模擬混合信號性能將翻一番,同時可編程I/O將隨著下一代DDR4和PCI Express接口而升級。

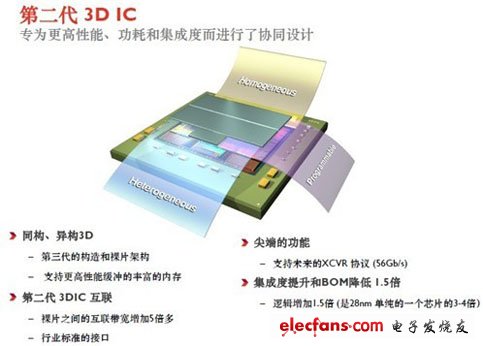

從第一代到第二代All Programmable 3D IC

和一個純粹的單芯片解決方案所可能達(dá)到的結(jié)果相比,湯立人表示賽靈思28nm同構(gòu)和異構(gòu)Virtex? 3D IC把設(shè)計容量、系統(tǒng)級性能和系統(tǒng)集成的水平均整整翻了一番,提供了領(lǐng)先一代的價值優(yōu)勢。

為在20nm繼續(xù)領(lǐng)先一代,賽靈思將利用一個兩級接口擴(kuò)大其3D IC的架構(gòu),讓同構(gòu)和異構(gòu)裸片的集成均能基于開放的行業(yè)標(biāo)準(zhǔn)實現(xiàn)。從而把邏輯容量擴(kuò)展1.5倍或增加30-40M ASIC等效門的設(shè)計。

對于如何應(yīng)對支持最高級別、最高性能和簡便設(shè)計的問題,湯立人表示,“為達(dá)成該高級別設(shè)計要求,可編程互聯(lián)的帶寬要增加5倍以上。因此,賽靈思正在著手開發(fā)第二代 All Programmable 3D IC技術(shù),致力于實現(xiàn)最高層次的可編程系統(tǒng)集成。”

FPGA智能之路該如何走?

FPGA目前已經(jīng)在逐漸占據(jù)高端ASIC的領(lǐng)地,并向更多新興應(yīng)用挺進(jìn),所以賽靈思CEO Moshe Gavrielov稱“ASIC日益變?yōu)閚iche,而FPGA應(yīng)用日益擴(kuò)大變?yōu)椤ㄓ谩保俚浆F(xiàn)在不斷集成新器件功能,使之更為智能化。這真是一個非常有意思的變化。未來,賽靈思的FPGA智能化之路將如何演進(jìn)?FPGA是否可以成為下一代嵌入式處理器智能化平臺?FPGA在成為下一代嵌入式處理器智能化平臺前還要應(yīng)對什么挑戰(zhàn)?歡迎大家討論。

?

電子發(fā)燒友App

電子發(fā)燒友App

評論