?

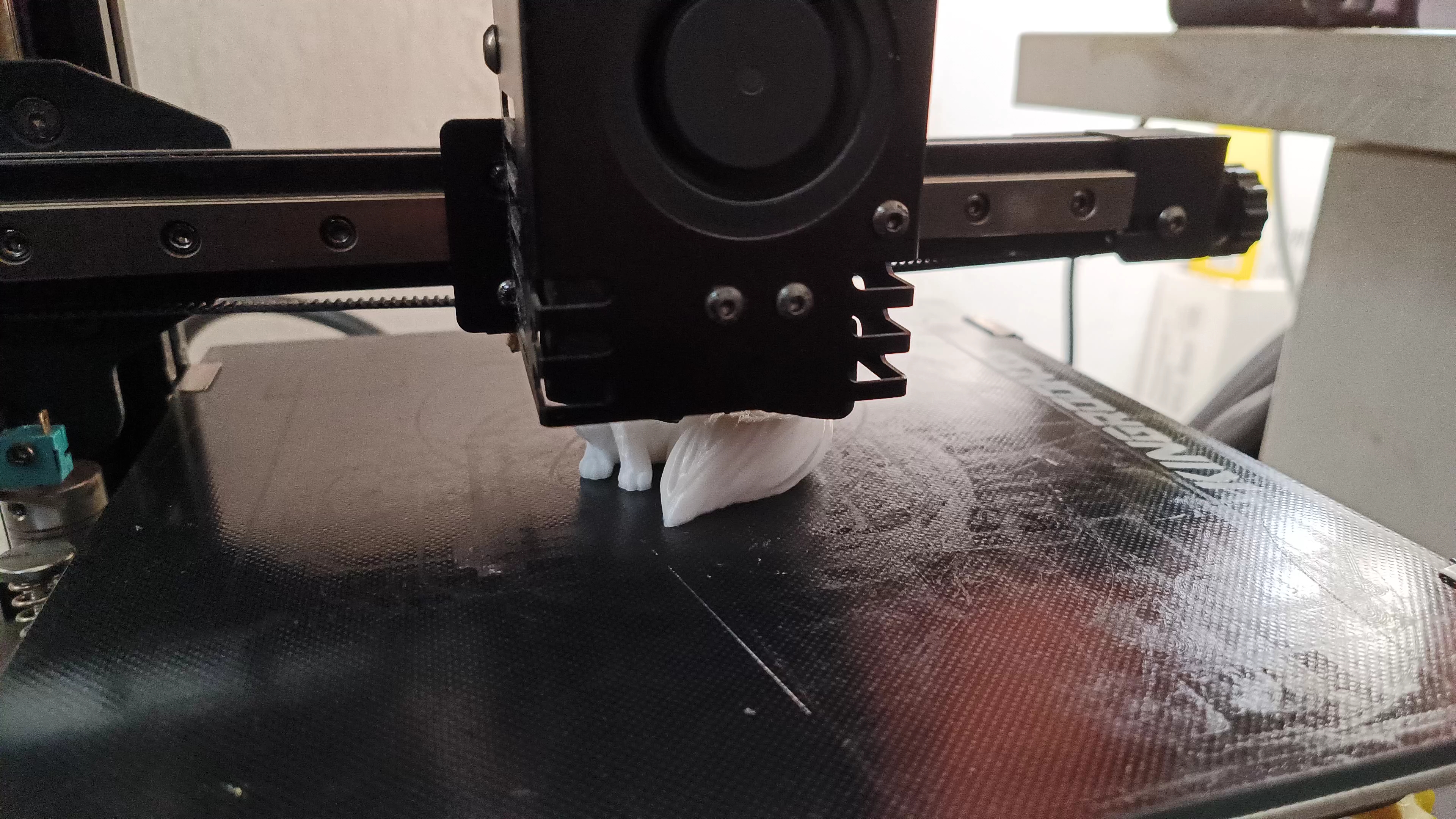

隨著目前平面化的芯片開(kāi)始出現(xiàn)多層式結(jié)構(gòu),半導(dǎo)體制造的基礎(chǔ)將在未來(lái)幾年發(fā)生轉(zhuǎn)變。在全球主要的半導(dǎo)體工程領(lǐng)域花費(fèi)近十年的時(shí)間致力于使得這種結(jié)構(gòu)實(shí)現(xiàn)可制造化之后,立體的三維芯片(3DIC)終于可望在明年開(kāi)始商用化──但這其實(shí)也已經(jīng)遠(yuǎn)落后于先前規(guī)劃的時(shí)程多年了。

過(guò)去幾年來(lái),芯片制造商們一直在努力地使與3DIC互連的TSV技術(shù)更加完善。現(xiàn)在,TSV已經(jīng)可針對(duì)2D作業(yè)實(shí)現(xiàn)最佳化了,例如從平面芯片的正面?zhèn)魉蛿?shù)據(jù)到背面的微凸塊,采用堆棧芯片的3DIC時(shí)代即將來(lái)臨。

去年冬天所舉行的國(guó)際固態(tài)電路會(huì)議(ISSCC)上所探討的主題幾乎都是3D芯片,例如三星(Samsung)公司大肆宣傳其1Gb行動(dòng)DRAM,并計(jì)劃在2013年前量產(chǎn)4Gbit芯片。透過(guò)三星的2.5D技術(shù),可使采用TSV的堆棧DRAM與系統(tǒng)級(jí)封裝(SiP)上的微凸塊密切配合。

預(yù)計(jì)今年秋天就能看到在2.5D技術(shù)方面的重大成就──賽靈思(Xilinx)公司將提供一種多級(jí)FPGA解決方案,它透過(guò)封裝技術(shù)而使四個(gè)平行排列的Virtex-7FPGA與硅晶內(nèi)插器上的微凸塊實(shí)現(xiàn)互連。***集成電路制造公司(TSMC)正在制造這種可為FPGA重新分配互連的硅晶內(nèi)插器──采用一種以‘塌陷高度控制芯片連接’(C4)技術(shù)接合基板封裝上銅球的TSV技術(shù)。臺(tái)積電承諾可望在明年為其代工客戶(hù)提供這種突破性的2.5D至3D過(guò)渡技術(shù)。

然而,2011年所發(fā)布最令人驚喜的3DIC消息來(lái)自于IBM公司。該公司最近透露已經(jīng)秘密地大規(guī)模生產(chǎn)可用于大量行動(dòng)消費(fèi)電子設(shè)備的成熟3DIC,不過(guò)使用的仍是低密度的TSV技術(shù)。由于累積了相當(dāng)?shù)募夹g(shù)經(jīng)驗(yàn),IBM聲稱(chēng)目前已掌握了3D的其它工程障礙,并預(yù)計(jì)能在2012年時(shí)克服這些挑戰(zhàn)。

“憑借一招半式闖天涯的時(shí)代已經(jīng)結(jié)束了,”IBM公司研究副總裁BernardMeyerson指出,“如果只想依賴(lài)于某種材料、芯片架構(gòu)、網(wǎng)絡(luò)、軟件或整合,就無(wú)法在3D性能戰(zhàn)中取得勝算。為了要在3D戰(zhàn)場(chǎng)上致勝,就必須盡可能地同時(shí)使用所有的資源。”

IBM在今年九月宣布已經(jīng)與3M公司商討共同創(chuàng)造一種新的設(shè)計(jì)材料──這種材料可望解決3DIC最后剩余的工程障礙:過(guò)熱問(wèn)題。3M公司的任務(wù)在于創(chuàng)造一種適合于堆棧芯片之間的填充材料,也是一種類(lèi)似電介質(zhì)的電絕緣體,但比硅晶的導(dǎo)熱性更佳。3M承諾可在兩年內(nèi)使這種神奇的材料商用化。

“現(xiàn)在,我們一直在進(jìn)行試驗(yàn),希望能在2013年以前發(fā)展出一個(gè)可行的方案,以實(shí)現(xiàn)廣泛的商用化,”3M公司電子市場(chǎng)材料部門(mén)的技術(shù)總監(jiān)程明說(shuō)。

然而,對(duì)于IBM-3M共同開(kāi)發(fā)的努力能否使雙方公司處于3DIC競(jìng)賽的領(lǐng)先位置,一些分析師們對(duì)此仍存疑。

“3M正在制造一種可為3D堆棧解決散熱問(wèn)題的填充材料,”MEMSInvestorJournal先進(jìn)封裝技術(shù)的首席分析師FrancoisevonTrapp說(shuō)。“雖然這絕對(duì)是在3DIC量產(chǎn)前必需解決的挑戰(zhàn)之一,但我認(rèn)為它不見(jiàn)得就是解決3D堆棧其余問(wèn)題的最后關(guān)鍵。”

3D無(wú)處不在

即使IBM公司聲稱(chēng)已在3DIC生產(chǎn)方面領(lǐng)先,但市場(chǎng)上也不乏其它競(jìng)爭(zhēng)廠商。事實(shí)上,美國(guó)TezzaronSemiconductor已經(jīng)為其鎢TSV制程提供3DIC設(shè)計(jì)服務(wù)多年了。Tezzaron的FaStack制程可從厚度僅12亳米晶圓的異質(zhì)芯片中制造出3D芯片。它能以每平方毫米1百萬(wàn)TSV深次微米互連的密度為堆棧DRAM提供WideI/O。

連續(xù)創(chuàng)業(yè)的企業(yè)家ZviOr-Bach指出,3DIC設(shè)計(jì)的焦點(diǎn)必須跳脫TSV至超高密度的單片式3D。Or-Bach會(huì)這么說(shuō),一點(diǎn)都不令人意外,因?yàn)樗罱€成為了IP開(kāi)發(fā)公司MonolithIC3DInc.的總裁兼CEO。另一家新創(chuàng)的BeSang公司也聲稱(chēng)即將制造出不必使用TSV技術(shù)的單片式3D內(nèi)存原型芯片,可望在2012年首次亮相。

然而,當(dāng)今最先進(jìn)的技術(shù)還是采用TSV的3D芯片堆棧,幾乎每一家主要的半導(dǎo)體公司都專(zhuān)注于這項(xiàng)技術(shù)的研發(fā)。“IBM公司更挑戰(zhàn)該技術(shù)極限,透過(guò)與3M公司的合作以尋求超越當(dāng)前架構(gòu)的其它可能性。然而,IBM在3D方面取得的每項(xiàng)進(jìn)展也將激起像三星(Samsung)、英特爾(Intel)與臺(tái)積電等競(jìng)爭(zhēng)廠商的創(chuàng)造力,這些廠商們都已在3DIC方面各自展開(kāi)相關(guān)開(kāi)發(fā)工作,”市場(chǎng)觀察公司TheEnvisioneeringGroup總監(jiān)RichardDoherty表示。

用于制造3DIC的技術(shù)并不是最近才開(kāi)發(fā)的,而當(dāng)今的工作重點(diǎn)在進(jìn)于一步提升這些技術(shù)。例如,目前許多CMOS成像器以TSV將畫(huà)素?cái)?shù)據(jù)從基板前面?zhèn)髦帘趁妫酒褩5母拍羁勺匪莸?a target="_blank">晶體管先驅(qū)WilliamShockley早在1958年時(shí)的專(zhuān)利。此后,堆棧芯片的配置常常被加以利用──例如在ASIC上堆棧MEMS傳感器,或在處理器核心上堆棧一個(gè)小型DRAM--但通常是使用焊線接合的方式來(lái)實(shí)現(xiàn)互連。

從焊線接合過(guò)渡到TSV的方式,使得互連更為密集。它還讓設(shè)計(jì)者們免于嚴(yán)格的矩形布局要求,讓他們能像設(shè)計(jì)電路板一樣地進(jìn)行芯片設(shè)計(jì)。缺乏電路的地區(qū)則可用于其它結(jié)構(gòu),如垂直互連總線或甚至是制冷劑氣體的煙囪等。異質(zhì)的3D堆棧芯片還提高了整合度,讓整個(gè)系統(tǒng)可組合成一個(gè)單一的硅晶塊。

“3DIC最重要的是帶來(lái)一個(gè)擺脫農(nóng)場(chǎng)般架構(gòu)的機(jī)會(huì),每個(gè)芯片分割為毗鄰的矩形區(qū)域,”Doherty說(shuō)。“3D芯片設(shè)者所使用的方式并不是試圖使用芯片上的所有空間,而是開(kāi)始從芯片上切割出正方形、三角形和圓形以實(shí)現(xiàn)垂直互連,并使其得以散熱。

“3D技術(shù)啟發(fā)了更多的芯片設(shè)計(jì)新思維。設(shè)計(jì)人員們現(xiàn)在能以創(chuàng)新的方式來(lái)結(jié)合CPU、內(nèi)存與I/O功能,使他們必須采取不同的思考方式來(lái)進(jìn)行設(shè)計(jì)。這在過(guò)去一切都得并排設(shè)計(jì)的傳統(tǒng)方式是無(wú)法實(shí)現(xiàn)的。”

全球主要的的半導(dǎo)體組織都為3D技術(shù)展開(kāi)各種標(biāo)準(zhǔn)建立工作。國(guó)際半導(dǎo)體設(shè)備材料產(chǎn)業(yè)協(xié)會(huì)(SEMI)成立了四個(gè)致力于3DIC標(biāo)準(zhǔn)制定的工作小組。此外,其3DS-IC標(biāo)準(zhǔn)委員會(huì)包括SEMI會(huì)員Globalfoundries、HP、IBM、英特爾、三星與聯(lián)華電子(UMC),以及Amkor、ASE、歐洲的IMEC、***工研院(ITRI)、Olympus、高通(Qualcomm)、Semilab、TokyoElectron與賽靈思等公司。

半導(dǎo)體制造聯(lián)盟(Sematech)已經(jīng)成立了一個(gè)3D芯片設(shè)計(jì)中心。參與成員包括Altera、ADI、LSI、安森美半導(dǎo)體(Semiconductor)和高通等公司。Sematech聯(lián)盟還在紐約州立大學(xué)阿爾巴尼分校科學(xué)與工程院設(shè)置一條300毫米的3DIC試產(chǎn)線。

比利時(shí)微子研究中心(IMEC)與CascadeMicrotech公司合作為3DIC進(jìn)行測(cè)試與特征化。德國(guó)研究機(jī)構(gòu)FraunhoferIZM表示可望在2014年以前將處理器、內(nèi)存、邏輯、模擬、MEMS和RF芯片整合于單片式3DIC中。

***工研院贊助成立了一個(gè)3DIC聯(lián)盟,目前已有超過(guò)20家成員聯(lián)盟。聯(lián)盟中的許多廠商們均可望從明年初開(kāi)始提供端至端的3DIC代工服務(wù)。

今年九月,在國(guó)際半導(dǎo)體展(Semicon)的3DIC技術(shù)論壇中,英特爾表示正致力于堆棧3DIC的開(kāi)發(fā)工作(但這并不是指其FinFET三閘晶體管)。此外,在Semicon上,爾必達(dá)(Elpida)據(jù)稱(chēng)其與力成科技(PowertechTechnology)和聯(lián)電在2GbitDRAM的共同研發(fā)上己取得了進(jìn)展,該合作團(tuán)隊(duì)采用了以高密度TSV連結(jié)的堆棧DDR3芯片。

聯(lián)合電子裝置工程協(xié)會(huì)(JEDEC)可望在今年底前率先為3DIC開(kāi)發(fā)出WideI/O標(biāo)準(zhǔn)。JEDEC規(guī)格將支持512位寬的接口。

法國(guó)半導(dǎo)體研究機(jī)構(gòu)CEA-LETI與意法半導(dǎo)體(STMicroelectronics)和硅晶內(nèi)插器制造商ShinkoElectricIndustriesCo.共同合作,以推動(dòng)2.5D至3DIC的順利過(guò)渡。該合作小組現(xiàn)于一座300毫米晶圓制造廠生產(chǎn)原型組件,預(yù)計(jì)最早在2012年推出商用化設(shè)計(jì)。

歐洲CMOSAIC項(xiàng)目則展開(kāi)更長(zhǎng)程的計(jì)劃,期望在2013年以前找到冷卻單片式3DIC堆棧的創(chuàng)新辦法。這項(xiàng)四年期的計(jì)劃還包括了蘇黎世IBM公司、巴黎高等洛桑聯(lián)邦理工學(xué)院(EcolePolytechniqueFederaledeLausanne)以及蘇黎世瑞士聯(lián)邦理工學(xué)院(theSwissFederalInstituteofTechnologyZurich)等組織的共同參與。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論