近日,小馬智行宣布與盧森堡大公國政府簽署諒解備忘錄,促進自動駕駛汽車及技術在盧森堡的發展。

2024-03-12 12:20:48 229

229 WitDisplay消息,今年,新質生產力被寫入中國政府工作報告,并被列為2024年政府工作十大任務的首位。這向行業和企業釋放出鮮明信號,凸顯出我國對加快發展新質生產力的重視和迫切。

2024-03-08 15:09:57 549

549 是德科技(Keysight Technologies, Inc.)全力支持Autotalks,通過其PathWave V2X解決方案對TEKTON3車聯網(V2X)系統級芯片(SoC)進行驗證。此次

2024-03-08 10:33:42 258

258 近日,長電科技旗下長電科技汽車電子(上海)有限公司獲增資44億元協議生效后,首期增資款項人民幣15.51億元已于2月22日到位,全力支持公司打造首座車規級芯片智能制造、精益制造燈塔工廠。

2024-03-01 18:21:25 797

797 世聞名的臺積電(TSMC)作為世界頂級合約芯片制造商,日本之行被譽為引爆了業內的產業安全投資熱潮,即便面對日本政府全力支持自家晶圓代工商Rapidus以期獲取更高回報。

2024-02-26 09:48:06 125

125 其中,電池中心堪稱該四期項目的重中之重。隨著沃爾沃汽車全力投入電動汽車科技領域,未來由先進的電池、電機及電控技術提供全力支持的電動化轉型將勢不可擋。沃爾沃汽車正在規劃中的中國電池中心,將涵蓋從后期維護到回收和再生產原材料的全線電池業務

2024-02-22 11:24:25 125

125 美國政府日前宣布,將向全球領先的芯片制造商格芯(GlobalFoundries)發放高達15億美元的補助金。這筆資金將主要用于支持格芯在紐約州和佛蒙特州的設施建造與擴建計劃,標志著美國政府重振國內芯片生產戰略的首筆重大投資。

2024-02-21 11:21:05 301

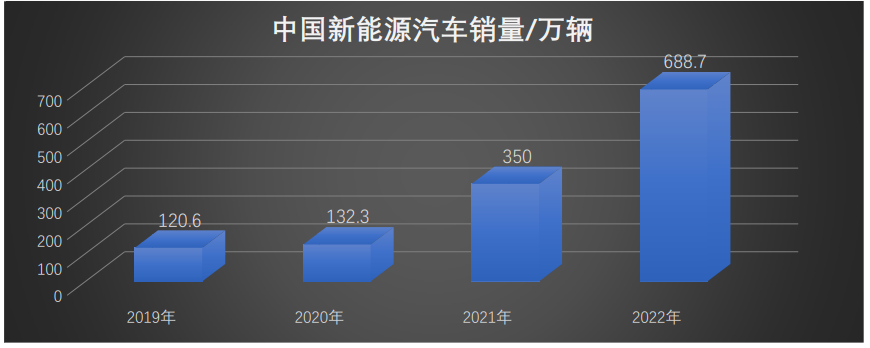

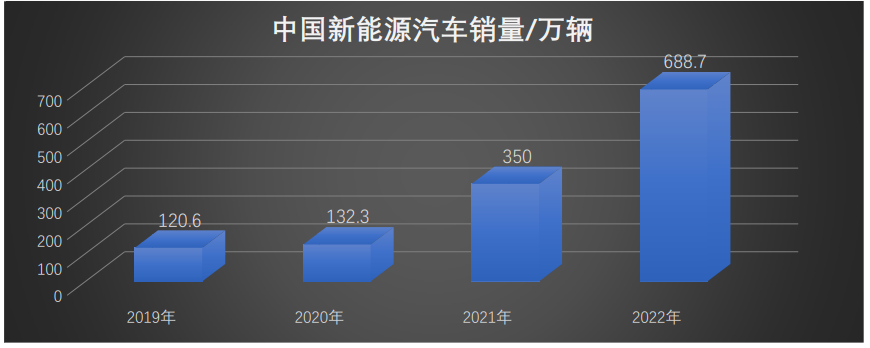

301 據市場研究機構預測,全球電池化成分容產線市場規模在未來幾年將繼續保持增長態勢。其中,亞洲市場增長速度最快,尤其是中國市場。中國政府對于新能源汽車和儲能領域的支持力度不斷加大,推動了電池化成分容產線的市場需求不斷增長。

2024-02-20 15:09:58 152

152

發展等新發展理念。中國科協主席萬鋼作序推薦。

2、解讀政府頂層設計和政策引導,洞察新能源汽車未來發展趨勢

本書是對我國新能源汽車產業變革的觀察手記,是對新能源汽車產業發展脈絡的沉思筆錄。聚焦新能源

2024-01-18 16:36:51

1. 中國啟動石墨出口管制,向韓國電池企業發放出口許可 ? 去年12月,中國政府開始控制電池正極材料的關鍵材料石墨的出口,但有報道稱,允許向韓國主要電池公司出口石墨。但不排除未來進一步加強對包括中國

2024-01-15 11:23:27 592

592

從互聯網、到移動互聯網,再到產業互聯網,中國互聯網發展已經有20多年,近十年則是產業互聯網迅猛發展的十年。近幾年,隨著中國數字經濟的高速發展及國家的利好政策,產業數字化正迎來了十年來最好的時間窗口

2024-01-04 11:57:40

官方透露,openEuler自捐贈給開放原子開源基金會后迅猛發展;該基金會于2022年12月宣布將openEuler升級為獨立項目群,以此提升其治理章程、社區運行效率、資源籌集機會等水平,并歡迎其他開源項目融入openEuler項目群,共享基礎設施、運營和營銷資源。

2023-12-15 14:33:41 145

145 在物聯網迅速發展的今天,藍牙網關作為連接設備的關鍵組件,發揮著越來越重要的作用。北京桂花網公司作為一家專業的物聯網解決方案提供商,其藍牙網關在功能和應用場景方面表現出色。本文將詳細介紹桂花網藍牙網關

2023-12-12 16:06:00

和分析。這就像農業物聯網的“智慧大腦”,為農業生產提供及時、準確的氣象預報和決策支持。提供的精準氣象數據,讓農民朋友們能夠在第一時間了解天氣變化情況,提前做好防范措

2023-12-11 13:33:08

為了塑造新的產業生態,辛國斌提出了多項措施,包括加強政策規劃交流、規范標準接口、實現基礎設施互聯互通等。他強調,我國將著力推進新能源與智能網聯汽車的創新發展,全力支持新一代動力電池、新型底盤、智能駕駛等關鍵技術的研發和產業化

2023-12-11 10:26:48 195

195 哥斯達黎加總統羅德里戈·查韋斯·羅夫萊斯表示:“該法令的重點是促進國家安全,防止間諜活動,因此政府做出了相關決定。”他還補充說,中國政府有義務讓企業提供哥斯達黎加要求的所有信息。

2023-12-08 11:59:46 1048

1048 產業服務模式。

隨著國家《數字中國建設整體布局規劃》、《“十四五”數字經濟發展規劃》等政策的出臺,數字經濟被提到了前所未有的高度。數字技術和實體經濟的深度融合,傳統產業數字化轉型,互聯網+智能制造

2023-12-04 10:01:18

產業服務模式。

隨著國家《數字中國建設整體布局規劃》、《“十四五”數字經濟發展規劃》等政策的出臺,數字經濟被提到了前所未有的高度。數字技術和實體經濟的深度融合,傳統產業數字化轉型,互聯網+智能制造

2023-12-04 09:58:30

但就在上周,德國聯邦憲法法院作出一項裁決,其裁定此前聯邦政府為應對新冠危機所冗余的600億歐元資金,不得轉移至“氣候與轉型基金”,這是有違憲法的。這也讓德國政府不得不尋找替代資金來源,并對包括擴建充電基礎設施在內的計劃項目產生了懷疑。

2023-11-27 10:01:37 229

229 為了推動儲能技術的發展和應用,中國政府加大了政策支持力度,儲能市場也在不斷擴大,在未來將有更廣闊的應用前景。兆越通訊緊隨其后,順勢而為,積極研發并推廣光伏儲能方案,旨在為綠色能源發展貢獻力量。

2023-11-23 15:28:01 188

188

西門子表示,隨著中國政府推進更多高科技制造業的發展,公司軟件和自動化產品的前景良好。該公司認為個人消費不會復蘇,正在關注中國市場,但認為2024年下半年將顯示出明顯的增長勢頭。

2023-11-17 09:40:30 253

253 。

在全球市場中,Xilinx、Altera兩大公司對FPGA的技術與市場仍然占據絕對壟斷地位。兩家公司占有將近90%市場份額,專利達6000余項之多,而且這種壟斷仍在加強。同時,美國政府對我國

2023-11-08 17:19:01

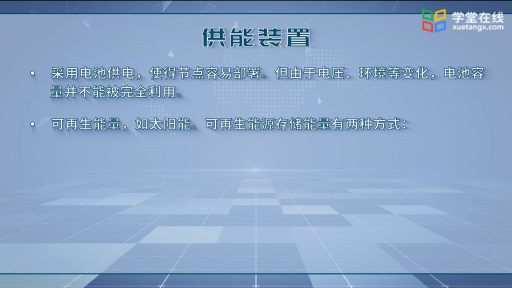

在物聯網里GPRS模塊耗電是很高的,那一般都是怎么控制功耗的。

2023-11-06 06:39:22

如何采用mqtt協議實現物聯網模塊消息推送

2023-11-03 06:55:53

首先,該計劃以消費類物聯網設備為焦點。目前,主要針對的是家庭物聯網設備,包括智能冰箱、智能空調、智能電視、智能溫控器、健身追蹤器等,并已經開始著手定義消費級路由器的安全標準。

2023-11-02 17:07:25 824

824

熱點新聞 1、美國政府通知英偉達:最新AI芯片管制提前生效! 英偉達10月24日發布8-K公告,表示其已收到美國政府題為“實施附加出口管制:某些先進計算項目;超級計算機和半導體最終用途;更新和更正

2023-10-25 18:55:02 2066

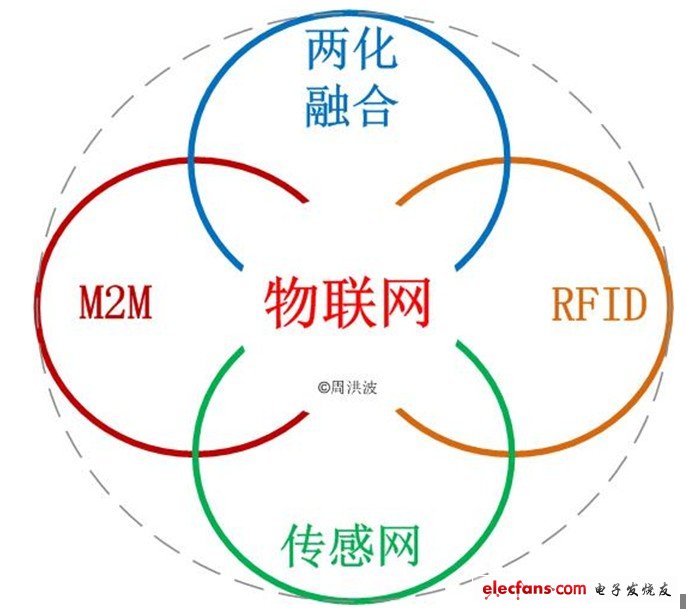

2066 物聯網專業前景怎么樣?

物聯網專業在當今技術發展迅速的背景下具有廣闊的前景。以下是物聯網專業的一些優勢和就業前景: 1.市場需求大:物聯網作為人工智能、云計算和大數據等技術的結合,已經成為許多

2023-10-20 09:48:41

MCU 是怎么為物聯網端點設備提高安全性的?

2023-10-17 08:53:03

▲支持傳感器300+; ▲采M2M雙向透傳通信技術、控制器之間靈活自組網;▲控制器多對多聯網雙向透傳通訊;▲智能聯網預警與聯動控制;▲支持遠程配置采集、控制參數;▲內置TTS智能AI語音

2023-10-08 17:43:52

細做,譜寫物聯網業務高質量發展新篇章。 近年來,中國移動全面落實國家物聯網新型基礎設施戰略,圍繞“連接+算力+能力”,以連接規模為基礎,向下延伸卡位入口,向上延伸拓展平臺和應用,向外建立產業生態,全力構建5G時代物聯網產品體系與物聯網

2023-09-27 11:32:41 436

436

起源于6 0年代末美國政府資助的一個分組交換網絡研究項目,到 9 0年代已發展成為計算機之間最常應用的組網形式。它是一個真正的開放系統,因為協議族的定義及其多種實現可以不用花錢或花很少的錢就可以公開

2023-09-26 06:18:35

IoT數智化為數字經濟提供了豐富的數據資源,推動經濟的發展和創新;同時,數字經濟的發展也為物聯網數智化提供了更多的應用場景和商業機會。IOTE 2023第二十屆深圳國際物聯網展以“IoT構建數字經濟

2023-09-22 15:41:02

IoT數智化為數字經濟提供了豐富的數據資源,推動經濟的發展和創新;同時,數字經濟的發展也為物聯網數智化提供了更多的應用場景和商業機會。IOTE 2023第二十屆深圳國際物聯網展以“IoT構建數字經濟

2023-09-22 15:39:23

2023年9月20日,由工信部中國電子信息產業發展研究院、珠海市人民政府以及橫琴粵澳深度合作區執行委員會共同主辦的2023琴珠澳集成電路產業促進峰會暨第十八屆“中國芯”頒獎儀式在珠海

2023-09-22 14:46:30

使用MQ-5傳感器、ESP8266和Arduino構建一個基于物聯網的LPG氣體泄漏檢測器。

2023-09-22 06:06:05

本帖最后由 zhh763984017 于 2023-9-21 16:53 編輯

今天給大家分享一個飛騰派的一個應用場景——邊緣物聯網關。邊緣物聯網關可以連接各種物聯網設備和傳感器,實現數據采集

2023-09-21 16:50:00

電池物聯網應用MCU都用哪些型號的

2023-09-20 07:57:10

昨日,高通公司通過高通無線通信技術(中國)有限公司向中國鄉村發展基金會捐贈人民幣800萬元,以支持在鄉村振興重點地區開展教育、農業、醫療等領域的項目。中國鄉村發展基金會副理事長陳志剛,高通公司企業

2023-09-13 20:45:01 358

358

產品

設備的集合,通常指一組具有相同功能的設備。物聯網平臺為每個產品頒發全局唯一的ProductKey。每個產品下可以有成千上萬的設備。

設備

歸屬于某個產品下的具體設備。物聯網平臺為設備

2023-09-11 07:41:47

物聯網(IoT)是由物理設備、車輛等組成的網絡,家用電器和嵌入有電子設備、軟件、傳感器等的其他物品,致動器,以及使這些物體能夠連接和交換數據。

2023-09-11 07:18:44

核心觀點 政府力量: 中國政府認清并抓住了發展新能源汽車的戰略機遇,帶領中國汽車產業打了一個翻身仗。我們千萬不要忽視市場經濟中政府的力量和影響,比如對產業和技術發展的導向作用。 雙管齊下: 我國

2023-08-29 17:20:02 205

205

美光公司負責全球運營的副總經理manish bhatia表示:“在中國20年時間里,美光公司在西安建立了dram成套設備及測試工廠等強有力的運營及客戶基礎。”李新明老師是一位經驗豐富的政府工作專家。

2023-08-29 09:58:19 540

540 ARM物聯網整體解決方案提供了一種獨特的基于解決方案的方法,將最新的專業處理能力與先進的軟件和工具相結合。

ARM物聯網整體解決方案可隨時實施或構建,從而簡化您的設計流程和產品開發。

2023-08-29 06:06:01

提起中國芯片,難免就會說到它的老對手臺積電。要知道,曾經臺積電也是中國眼中的香餑餑,臺積電作為全球晶圓代工一哥,無論是資源還是技術都是數一數二的。中國曾經也想過給臺積電足夠的支持,助力其發展。

2023-08-28 17:18:35 811

811 為了解決這個問題,據報道,英國政府正在向 Nvidia 訂購多達 5,000 個圖形處理單元 (GPU)。GPU,也稱為顯卡,對于芯片的處理能力至關重要,特別是對于人工智能模型所需的復雜動作。然而

2023-08-22 16:32:22 794

794 工業互聯網平臺

工業互聯網平臺的本質是在傳統云平臺的基礎上疊加物聯網、大數據、人工智能等新興技術,搭建對工業數據采集、存儲、分析和應用的模塊體系,實現工業互聯網輔助的生產功能。包含邊緣層、平臺層

2023-08-10 15:45:26

本指南供硬件和軟件架構師學習如何使用Alexa語音服務集成在受約束的物聯網設備上設置語音命令。AWS物聯網核心的Alexa語音服務集成(AIA)將與Alexa Voice Services集成所需

2023-08-02 12:53:08

隨著科技的飛速發展,芯片作為信息技術的核心部件,對于現代社會的發展具有舉足輕重的地位。近年來,中國政府高度重視芯片產業的發展,通過政策扶持、資金投入和人才培養等措施,推動中國芯片產業實現了快速發展

2023-08-02 11:27:02 5881

5881 近日,受臺風“杜蘇芮”影響,福建、華北、黃淮等地出現極端降雨過程,引發洪澇和地質災害。中興通訊第一時間啟動了臺風BCM應急響應及通信保障預案,全力助力運營商支持災區的通信搶險保障工作。 中興通訊調集

2023-08-01 20:15:02 306

306

隨著科技的飛速發展,芯片作為信息技術的核心部件,對于現代社會的發展具有舉足輕重的地位。近年來,中國政府高度重視芯片產業的發展,通過政策扶持、資金投入和人才培養等措施,推動中國芯片產業實現了快速發展

2023-07-31 16:51:23 2462

2462 中芯國際是中國芯片行業中的領軍企業之一,不過其在制程技術上已經落后了幾代,一直在積極研發14nm芯片。然而,根據最新消息,中芯國際不得不宣布,公司部分芯片制造設備被美國政府列入出口管制清單,導致無法

2023-07-31 16:13:26 1523

1523 近年來,美國在芯片領域遇到了來自中國的強大挑戰,這引發了美國主要半導體制造商的高管的關注。他們近日齊聚一堂,討論如何應對這一局面,并呼吁美國政府停止對中國芯片市場的限制。 這些高管們表示,過于嚴格

2023-07-19 10:21:18 273

273 7月4日,外交部發言人毛寧主持例行記者會。有記者提問,中國政府昨天發布了關于對鎵和鍺的出口管制,鎵和鍺是半導體的材料,有評論認為這是中國對美日荷對半導體設備出口管制的反擊,發言人是否同意?此外

2023-07-05 08:47:39 374

374 電子發燒友網站提供《支持物聯網的16x2 LCD屏幕.zip》資料免費下載

2023-06-28 14:35:40 0

0 近年來,物聯網相關技術逐步成熟并擴展至生活應用,在整合云端運算技術的發展下,其擁有快速反應服務需求、信息更新等優勢,導入云端服務更可節省服務器、帶寬等軟硬件大量建構成本,有效地提升開發效率。而物聯網

2023-06-25 06:55:30

2023中國工業互聯網展,工業軟件展,全力推動制造業數字化轉型升級

2023-06-16 16:46:39 599

599 他表示,中國政府高度重視促進數字經濟與實體經濟的深度融合,加快制造業高端化,智能化,綠色化的發展。工業和信息化部的制造業的全面推進高水平對外開放,營造市場化、法治化、國際化一流營商環境,智能制造等先進制造業領域的跨國公司在中國國內增加投資,支持促進中小企業的數字化轉型。

2023-06-15 11:02:29 337

337 電子發燒友網站提供《支持物聯網種植系統的構建.zip》資料免費下載

2023-06-15 09:47:56 0

0 隨著物聯網技術的不斷發展,超低功耗MCU已經成為了物聯網方案中主要的芯片處理技術。超低功耗MCU具有眾多的優點,其中一大所用就是能夠大大提高物聯網設備的續航能力,保證設備在長時間內不掉電不斷電。那么

2023-06-13 18:18:17

在5G全連接工廠的布局謀劃上,我國政府早就出臺了相應的政策鼓勵并支持我國5G+工業互聯網的發展。2021年1月,工信部發布《工業互聯網創新發展行動計劃(2021—2023年)》,提出到2023年,在10個重點行業打造30個5G全連接工廠。

2023-06-13 16:37:39 386

386 最新、最強大的模型GPT-4將向美國政府機構開放 此前微軟已向其商業客戶提供了OpenAI模型,現在微軟宣布將向azure government云計算客戶開放openai的人工智能模型。該客戶包括許多美國政府機構,他們可以接觸使用大型語言模型,如gpt-3和gpt-4。

2023-06-08 20:15:15 1182

1182 了600GW,其中中國的光伏發電總裝機容量已經超過了200GW。 光伏產業的發展受到了政策的支持。各國政府紛紛出臺了一系列的政策措施,以鼓勵企業加大對光伏產業的投入。例如,中國政府出臺的“光伏扶貧”政策,為貧困地區提供了光

2023-06-06 10:10:27 453

453 香港《南華早報》5月29日發表社論,批評美光過去曾170次游說美國政府提出和中國有關的問題,如今的下場是一種“反噬”。 報道稱,中國已經開始對美國芯片制造商美光公司的產品實施禁令。雖然外界看來這是

2023-05-31 08:41:06 207

207 免去了運行商的成本,但需要自己建基站。

目前看來,BLE在平衡功耗,速率,成本,組網能方面是做的最好的,目前的發展趨勢看來,將是短距物聯網連接的主流方案。根據藍牙組織的報告,低功耗藍牙的全球

2023-05-15 15:57:17

發展趨勢來看,預計中國無線電導航設備行業將會繼續保持較快的增長,主要是由于中國政府投入更多資金,以改善無線電導航設備行業的基礎設施,以及推動行業的技術創新和發展。同時,隨著我國海外市場的不斷擴大,無線電導航設備將有望進一步拓展海外市場,從而提高市場占有率。

2023-05-15 11:46:17 695

695 采用900MHz頻段,低于當前WiFi的2.4GHz和5GHz頻段。更低功耗,同時HaLow的覆蓋范圍可以達到1公里,信號更強,且不容易***擾。這些特點使得WiFi更加順應了物聯網時代的發展

2023-05-11 11:27:19

Internet of Things )、LoRa(long range)是國內主要發展的物聯網LPWA技術。國家政策、工作頻段、技術特性、網絡環境及應用場景需求等因素均會影響兩種技術在國內的發展

2023-05-11 10:14:49

的發展,一個好的 AI 技術產品該如何迭代與運營……

為了能夠與廣大開發者一起更好地擁抱 AI 技術的發展,5 月 13 日,由天工開物開源基金會、開源中國社區聯合發起的,面向廣大開發者的中國開源未來

2023-05-09 09:49:41

繼《一套支持中文C語言編程的鴻蒙Hi3861智能硬件開發套件》發布后,中文C語言編程玩轉物聯網華為鴻蒙Hi3861開發,多個基礎案例視頻,包括交通紅綠燈、數碼管、光電開關、手指偵測心率、超聲波測距等案例已陸續更新上傳到B站:

2023-05-08 23:50:35

Blynk 最近推出了一個新的物聯網平臺,對 ESP8266 提供開箱即用的支持,具有許多很酷的功能,包括設備配置和管理、云中的數據托管、固件無線更新、用戶和組織管理、數據分析、各種自動化等等。

2023-04-28 06:15:54

物聯網專業菜鳥,勞請哪位大神幫忙試做此道題目。

2023-04-26 13:51:34

安科瑞虞佳豪一、引言近幾年來,物聯網概念加快與產業應用融合,成為智慧城市和信息化整體方案的關鍵性技術思維。當前,物聯網已由概念炒作、碎片化應用、閉環式發展進入跨界融合、集成創新和規模化發展的新階段

2023-04-20 10:31:42

PSoC 6 RTT開發板在 RT-Thread 上外設支持情況:1、cypress_gateway_demoInfineon + RT-Thread 物聯網 Demo這是一個基于 PSoC 6

2023-04-13 13:46:31

電梯設備的運行狀態,為電梯物聯網系統決策提供及時、可靠、全面的信息,便于對電梯設備的精細化和預防性維護保養提供了有力的技術支撐,從而為電梯的安全運行提供保障。未來,隨著人工智能技術不斷發展,AI落地將

2023-04-11 10:14:02

制造業集群展以“科技帶動產業創新,協同聚合優質資源”為主題,在《深圳市科技創新“十四五”規劃》和《深圳市人民政府關于發展壯大戰略性新興產業集群和培育發展未來產業的意見》的“20+8”產業集群規劃指導下

2023-04-07 16:44:02

的高級計量基礎設施設備有助于從最終用戶收集數據,同時管理配電自動化設備。物聯網與智能電網的融合物聯網可以支持智能電網中的技術。物聯網和智能電網的結合有助于促進智能電表、設備和傳感器的發展。它還實現了

2023-04-07 09:22:47

的,并且有支持多種替代來源的空間。它還允許監測可再生能源和設備。 支持物聯網的智能電網優勢 智能基礎設施系統是智能電網的能源、信息和通信基礎設施。它促進了電力和信息的雙向流動。與傳統電網相比,智能電網有

2023-04-06 16:34:25

環境中以不同的速度部署,這取決于與現有技術、監管發展和投資框架的兼容性。 物聯網和智能電網 智能電網構成了物聯網框架的關鍵方面,可以遠程監控和管理幾乎所有內容。幫助建立一個清潔、安全和高效的未來

2023-04-06 16:29:53

1 引言為支持本次物聯網大賽,廣和通以借或優惠銷售的方式提供給參賽隊開發套件要點說明支持方案大賽特價大賽優惠券實付FM650開發套件5G標準模組開發套件,提供M.2轉USB接口借

2023-04-06 14:24:16

,推動產業互聯網各參與主體進行全方位的跨界碰撞與資源鏈接。為表彰過去一年為推動中國產業互聯網發展作出貢獻的優秀平臺企業、企業家以及投資機構,大會發布了系列榜單。作為值得信賴的電子產業一站式服務平臺,華秋

2023-03-24 14:05:32

,推動產業互聯網各參與主體進行全方位的跨界碰撞與資源鏈接。為表彰過去一年為推動中國產業互聯網發展作出貢獻的優秀平臺企業、企業家以及投資機構,大會發布了系列榜單。作為值得信賴的電子產業一站式服務平臺,華秋

2023-03-24 14:02:16

移動&中移物聯網、樂鑫信息科技、霍尼韋爾、CSA聯盟、廣和通、TI、兆易創新等物聯網知名企業支持,南京大學、鄭州大學、東北大學、北京工業大學、湖南大學、上海交通大學等共同承辦,機械工業出版社支持

2023-03-24 09:33:43

物聯網課程清單

課程類別

課程名稱

視頻課程時長

視頻課程鏈接

課程鏈接

硬件

L610模型組及開發板硬件信息介紹part1

11分49秒

https://t.elecfans.com/v

2023-03-24 09:18:03

電子發燒友App

電子發燒友App

評論