8237 可編程DMA控制器 altera提供

2012-08-10 18:09:17

有誰需要ALTERA的ip核,qq57694560,cjfwindy@163.com [此貼子已經被作者于2009-10-14 14:26:18編輯過]

2008-11-16 19:50:33

我用的是CYCLONEIII的芯片,定制DDR2 IP核,之后直接用SINALTAP進行信號抓取,發現無法讀寫的原因是local_init_done 一直為低,就像XILINX里

2013-04-27 09:46:54

本帖最后由 dybttkl 于 2015-11-1 13:26 編輯

用的cycloneiii 里面的ddr2 ip核。感覺網上的資料很少,仿真的倒很多,但是真正到用戶接口那段時序的解釋卻一個也沒有。為何沒人寫個教程

2015-11-01 13:24:54

模塊轉換方向(FFT/IFFT)可指定。?易于使用的IP工具臺(Toolbench)接口。?Altera支持的VHDL和Verflog HDL仿真器上的IP功能仿真模型。2.特點FFT 2.0.0版具有

2012-08-13 14:34:06

研究了很久,實在弄不出來了,有沒有人用過Altera的PCIe IP核???急求!!!謝謝!!!求大神幫忙......

2016-05-26 09:12:33

小弟用的quartus ii軟件,調用altera公司的一個乘法器lpm_mult,無結果輸出,是不是調用的IP核都要收費呢,有沒有辦法破解呢????

2015-06-05 11:23:31

以下主題概述了Altera的外部內存接口解決方案。

Altera提供最快、最高效、延遲最低的內存接口IP核。Altera的外部存儲器接口IP設計用于方便地與當今更高速的存儲器設備接口。

Altera

2023-09-26 07:38:12

語言編寫的浮點矩陣相乘處理單元[1],其關鍵技術是乘累加單元的設計,這樣設計的硬件,其性能依賴于設計者的編程水平。此外,FPGA廠商也推出了一定規模的浮點矩陣運算IP核[2],雖然此IP核應用了本廠家的器件,并經過專業調試和硬件實測,性能穩定且優于手寫代碼,但仍可對其進行改進,以進一步提高運算速度。

2019-08-22 06:41:38

Altera系列FPGA芯片IP核詳解

2020-06-28 13:51:01

Altera_IP核,僅供參考

2016-08-24 16:57:15

實現特權同學的例程 特權FPGA VIP視頻圖像開發套件例程詳解2——DDR2控制器讀寫測試 時,進行IP核配置時,進入下一步配置參數時,變成黑屏重裝軟件也不行

2018-01-24 08:23:17

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則

2012-08-12 12:21:36

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

實現特權同學的例程 特權FPGA VIP視頻圖像開發套件例程詳解2——DDR2控制器讀寫測試 時,進行IP核配置時,進入下一步配置參數時,變成黑屏重裝了軟件也不行,到這個頁面還是黑屏,軟件版本是13.0

2019-05-17 06:35:42

使用altera的FFTIP核的可變流結構進行FFT時,輸出為什么跟實際情況是倍數關系

2016-09-20 19:18:10

最近在使用altera的FIR IP核做半帶濾波器,quartus ii軟件也破解了,firIP核也破解了,modelsin仿真也通過了,但是下載不了.sof文件到開發板,大家有用FIR IP核成功實現下板的經驗嗎,求大神指點呀。謝謝!

2018-05-11 16:01:15

altera公司IP核使用手冊

2012-08-15 13:11:24

altera公司IP核使用手冊,分享給想學習altera公司FPGA的IP核使用的親們~~

2013-02-16 22:40:19

問題:采用altera公司的ep4ce6e22c8控制器的一對差分引腳實現差分輸入輸出配置功能嘗試方法:嘗試配置LVDS IP核,但發現只有單獨的輸入輸出,如圖

2019-10-20 22:13:05

機制對當前變長分組骨干網的流量控制還是具有重要的參考價值,所以有必要對ATM的流量控制及其實現方式進行深入的研究。 IP核是一段具有特定電路功能的硬件描述語言代碼,該程序與集成電路工藝無關,因而

2011-09-27 11:54:25

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

為任意或所有DDR3 SDRAM器件提供單獨的終端阻抗控制,提高了存儲器通道的信號完整性。圖2:DDR3存儲器控制器IP核框圖DDR3存儲器控制器應支持廣泛的存儲器速率和配置,以滿足各種應用需求。例如

2019-05-24 05:00:34

在quartus2中創建了一個DDR2 控制器的ip核 ,但是在選擇 DDR型號的時候,找不到我要用的DDR芯片信號 怎么辦?選擇了一個DDR芯片將它的行列bits數改了之后 發現 內存大小又不對 。求解答

2017-09-19 14:50:23

EVL6562A-35WFLB,評估板使用L6562A 35W寬范圍高功率因數反激式轉換器。它描述了基于過渡模式PFC控制器L6562A的產品評估板,并展示了其臺架演示的結果。該板是35 W,寬范圍

2019-10-11 08:40:07

的SOPC系統中設計了LCD顯示驅動IP核,并下載到Cyclone系列的FPGA中,實現了對LCD的顯示驅動。

2019-08-06 08:29:14

Rockchip I2C控制器支持哪些功能?

2022-03-02 09:56:27

(Intellectual Property Core)。本文介紹USB 2.0設備控制器IP中的AHB接口部分設計。1設計概述1.1協議概述 設計前首先需要了解USB和AHB數據傳輸的特點

2019-05-13 07:00:04

大家好,有沒有誰比較熟悉ALTERA公司的VIP系列ip核,我們用該系列IP核中的某些模塊(主要是scaler和interlacer)來實現高清圖像轉標清圖像(具體就是1080p50轉576i30

2015-04-13 14:12:18

你好任何人都可以指導我,Xilinx ISE中的DDR控制器是否有任何IP實現。如果沒有如何實現DDR控制器以上來自于谷歌翻譯以下為原文Hi can any one guide me

2019-02-27 12:13:51

大家好,應用altera Cyclone V外接DDR3,啟用HMC實現硬核控制,IP核在設計生成時出現如下錯誤:Error: Error during execution of script

2018-04-25 10:28:52

請教各位大神,小弟剛學FPGA,現在在用spartan-3E的板子,想用上面的DDR SDRAM進行簡單的讀寫,用MIG生成DDR核之后出現了很多引腳,看了一些資料也不是很清楚,不知道怎么使用生成的這個IP核控制器來進行讀寫,希望大神們稍作指點

2013-06-20 20:43:56

modelsim 仿真 altera IP核(ROM,RAM實例)急求大神們ROM和RAM 的綜合仿真代碼

2015-11-19 21:02:57

2.5MHz 振幅0-5V 的正弦信號,請問 data 端口應該輸入怎樣的信號?如果有Altera IP核相關的詳解資料推薦下更好。多謝了。

2014-10-28 12:34:41

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。Altera DDR2控制器使用IP的方式實現,一般很少自己寫控制器代碼。ddr22

2020-02-25 18:33:00

本文介紹一款USB OTG IP核的設計與實現,該設備控制器可作為IP核用于SoC系統中,完成與主機控制器的通信,并能與普通的USB從設備進行通信。

2021-04-29 06:47:00

在較大工程中由于其局限性使用的越來越少,不推薦再學習;Verilog HDL為當今主流的設計方式;用IP核代替用戶自己設計的邏輯,可以大大縮短開發周期,提供更加有效的邏輯綜合和實現。Altera IP

2019-03-04 06:35:13

的DDR2控制器IP核模塊進行讀寫操作。每1.78秒執行一次DDR2的寫入和讀出操作。先是從0地址開始遍歷寫256*64bits數據到DDR2的地址0-1023中;在執行完寫入后,執行一次相同地址的讀

2016-10-08 17:05:55

`例說FPGA連載41:DDR控制器集成與讀寫測試之DDR2 IP核接口描述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖

2016-10-27 16:36:58

用 quartus 生成一個ddr2的ip核,選擇了生成仿真模型,但生成不了,文件目錄下沒有example.v,只有一個對應 的sdc文件 。 另外生成報告里還有 一個warning ,,求指導

2017-09-07 11:48:09

想問下 怎樣 用 Altera DE2C35F672C6 進行視頻圖像采集。一個攝像頭采集,一個液晶顯示采集的圖像?謝謝各位啊 新手不會,希望能附上工程{:4:}

2012-04-27 21:57:13

Altera系列FPGA芯片IP核詳解

2016-08-19 17:24:48

`勇敢的芯伴你玩轉Altera FPGA連載63:PLL IP核創建于配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 可以復制上一個

2018-04-20 21:45:06

;nbsp;IP碎片;FPGA;RLDRAM控制器;最大傳輸單元;Abstract:In order to secure the&

2008-10-07 11:01:03

工具,經面向硬件電路的仿真驗證,本文的方法可實現OC-48接口(2.5Gb/s)上線速分組的IP碎片重組,并具有硬件開銷小,可擴展性好的特點。關鍵詞: IP碎片;FPGA;RLDRAM控制器;最大傳輸

2008-10-07 11:00:19

PCI接口控制器兆核函數(即接口IP)及相關測試平臺,通過選擇合適的芯片速度,可以滿足運行在33MHz或66MHzPCI時鐘下的時序要求,支持Altera的Stratix II、Stratix

2018-12-04 10:35:21

引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級設計集成到單個芯片中即實現片上系統SoC。IP核的復用是SoC設計的關鍵,但困難在于缺乏IP核與系統的接口標準

2019-06-11 05:00:07

Viterbi譯碼的基本過程,接著根據Viterbi譯碼器IP核的特點,分別詳細介紹了并行結構、混合結構和基于混合結構的增信刪余3種Viterbi譯碼器IP核的主要性能和使用方法,并通過應用實例給出了譯碼器IP

2010-04-26 16:08:39

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率[3]。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

2019-07-09 07:23:09

的CycloneIIEP2C35芯片上集成了NiosII軟核,相關的外圍控制器和自定義的電機控制模塊,完成了該設計的驗證工作。1基本原理步進電機是一種把電脈沖信號變換成直線位移或角位移的執行元件。步進

2019-05-31 05:00:07

性,因此本文選擇了PCI總線。33MHz、32位的PCI總線的數據傳輸速率最高可達133MBps, 完全可以滿足高速實時傳輸的需求。選擇了Altera公司的PCI編譯器軟件包來實現PCI接口控制

2018-12-07 10:34:34

任務需求來定制顯示控制功能,可以增強系統可靠性和設計靈活性,降低了成本。目前針對LCD 顯示屏設計的控制器IP 核文章較多[1-2],但對于TFT-LCD 觸控屏設計的控制器IP 核文章較少[3],而且

2018-11-07 15:59:27

,LCD液晶顯示器憑借功耗低、體積小、輕薄及控制驅動簡單等特點,在智能儀器、儀表和低功耗電子產品中得到了廣泛應用。以深圳秋田視佳實業有限公司的液晶顯示模塊CBGl28064為例,告訴大家, 如何在SOPC的NiosII中設計LCD顯示驅動IP核?實現了對LCD的顯示驅動。

2019-08-05 07:56:59

,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據

2022-02-08 07:08:01

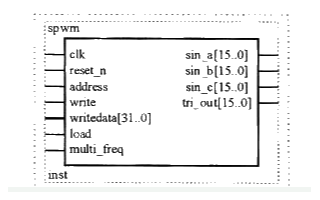

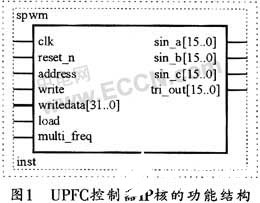

本文利用Altera公司的Quartus開發工具設計了一個基于Avalon總線接口的UPFC控制器IP核,以便于和NiosII組成一個完整的控制系統。

2021-04-08 06:25:12

我想通過JTAG在我的設計中內部訪問寄存器。1)如何掛鉤fpga JTAG鏈?2)是否有JTAG控制器IP?我看了,沒看到一個。謝謝,弗雷德

2020-05-29 06:13:24

本文介紹的是基于RISC體系結構的8位高速MCUIP軟核的設計與實現,采用Verilog HDL自上而下地描述了MCUIP軟核的硬件結構,并驗證了設計的可行性和正確性。在實際硬件電路中,該IP核的運行頻率達到75MHz,可應用于高速控制領域。

2021-04-19 07:28:21

請問誰手里還有原來ip-extreme免費版本的coldfire for altera軟核,能否分享給我一份?

2021-06-21 06:25:01

1、建立工程,2、調用DDR2 ip核。3、設置參數,選擇如上圖。其余保持默認。生成IP4、選擇ddr2_phy_ddr_timing.sdc、ddr2

2014-11-01 20:50:15

本人想使用altera的以太網IP核tse核,發現Quartus里面并沒有告訴怎樣控制這個核。請問大家是怎樣控制這個IP核的呢?完全用Verilog代碼編寫控制程序,好像很復雜呀,難道只能通過NiosII軟核嗎

2015-01-22 14:55:31

很多FPGA工程師陶醉于用硬件描述語言搞定龐大的邏輯難題,面對復雜的TCP/IP 協議時卻素手無策,怎么辦? 方案1、用ALTERA的NIOS II+免費的以太網第三方軟核,搞定!速度達到

2014-12-16 16:11:47

pc和一款控制器通過網線連接,arp-a命令查詢不到局域網內有控制器的ip,請問有沒有什么方法可以查詢到控制器的ip地址?

2021-06-18 10:53:37

數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言中的printf()函數),可以直接調用,非常方便,大大加快了開發速度。使用Verilog調用IP

2018-05-16 11:42:55

請問Altera RAM IP核怎么使用?

2022-01-18 06:59:33

本文介紹的在電能質量監測系統中信號采集模塊控制器的 IP核,是采用硬件描述語言來實現的。

2021-04-08 06:33:16

如題,調用altera公司的FFT IP核,用的是13.1版本,將modulsim仿真的結果輸入到matlab畫出頻譜圖,功能仿真結果沒有問題,但門級仿真中除了原頻率信息外,出現了很多不存在的頻率

2018-08-28 20:43:56

系統級設計,設計人員現在使用SOPC Builder工具時,可以選擇Freescale?、ARM?或者Altera軟核處理器以及50多種其他的知識產權(IP)模塊。 &

2008-06-17 11:40:12

IP核的Verilog程序進行綜合時,可選用Altera公司的CycloneIIEP2C35評估板。該板有33216個邏輯單元,105個M4k存儲模塊,35個18×18乘法單元,4個PLL和475個I

2019-06-03 05:00:05

,我國也迫切需要發展自己的IP核。本文針對I2C的主方式串行擴展通信的特點,詳細給出設計過程和結果。1 IP核簡介 IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM

2019-04-12 07:00:09

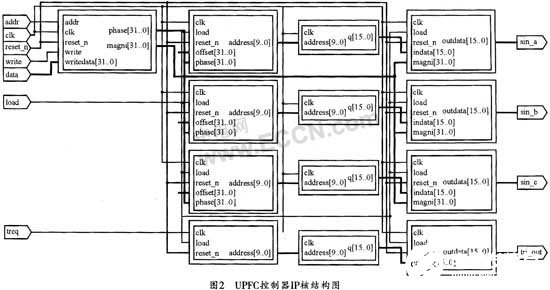

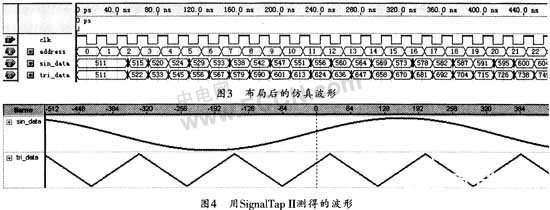

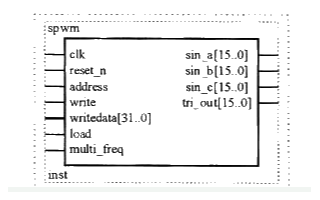

統一潮流控制器淵UPFC冤是柔性交流輸電系統淵FACTS冤的一種,其核心是控制系統設計遙文中根據正弦脈寬調制原理,并針對軟件和硬件實現正弦調制波形所存在的不同缺點,提

2009-03-07 10:07:08 15

15 本文介紹一款USB 設備控制器IP CORE 的設計與實現。論文首先介紹了USB 設備控制器的設計原理,模塊劃分及每個模塊的功能。然后介紹了該IP CORE 在ModelsimSE 中的功能仿真及FPGA 驗證結

2009-08-06 11:39:00 8

8 本文以改善UPFC 動態性能為出發點,指出了UPFC 研究中存在的問題:1 目前針對UPFC 系統所建立的模型不完整,使得控制系統設計中存在缺陷;2 沒有一個有效、合理的潮流調節器參數

2010-02-22 10:00:31 19

19 針對給定的UPFC 的控制目標,提出了一種在全論域范圍內帶有自調整因子的變間距模糊 交互控制 策略,并將其應用于UPFC 的控制系統設計中,減少了多個調整因子尋優的復雜性,克服了

2011-08-11 16:51:16 26

26 本設計基于FPGA的彩色觸摸屏控制器能夠實現顏色深度為24 bit,分辨率為480×272的TFT-LCD控制和ADS7843芯片的時序控制,為后續IP核的編寫工作打下了基礎。

2013-01-07 11:08:20 2731

2731

統一潮流控制器(Unified Power Flow Con-troller,簡稱UPFC)是一種可以較大范圍地控制電流使之按指定路經流動的設備,它可在保證輸電線輸送容量接近熱穩定極限的同時又不

2020-03-19 10:00:47 1290

1290

本文的目的是使用基于智能控制器的 UPFC 設備提高電力系統的穩定性和可靠性。 UPFC 設備在各種故障條件下由模糊邏輯控制器控制。 模糊邏輯控制器將電壓、相角等電力系統參數與參考值進行比較,產生

2021-11-29 16:04:59 0

0

![]()

電子發燒友App

電子發燒友App

評論