1、引言

傳統(tǒng)的測控網(wǎng)是將具有各種功能的儀器通過諸如VXI、CAN等專用總線連接起來構(gòu)成一套完整的測控系統(tǒng)。現(xiàn)在看來,傳統(tǒng)的測控網(wǎng)主要具有四個方面的不足:一、數(shù)據(jù)傳輸速率有限;二、傳輸距離有限;三、設(shè)備數(shù)量有限;四、成本高昂。傳統(tǒng)的測控網(wǎng)已經(jīng)很難滿足人們對大數(shù)據(jù)量,遠距離和低成本的要求。隨著Internet技術(shù)的發(fā)展和普及,通過將儀器接入Internet,儀器將測量的數(shù)據(jù)封裝成IP包的形式進行傳輸,不僅能夠解決傳統(tǒng)測控網(wǎng)的不足,而且可以共享網(wǎng)絡(luò)技術(shù)發(fā)展帶來的便利,跨越地域的限制,實現(xiàn)測量數(shù)據(jù)的共享。本文主要討論多路千兆以太網(wǎng)信號中IP數(shù)據(jù)收發(fā)的設(shè)計與實現(xiàn),詳細介紹了MAC接收控制器的設(shè)計,為儀器接入網(wǎng)絡(luò),組建高速的網(wǎng)絡(luò)化測控系統(tǒng)提供了一種經(jīng)濟高效的測試數(shù)據(jù)傳輸手段。

2、系統(tǒng)功能及介紹

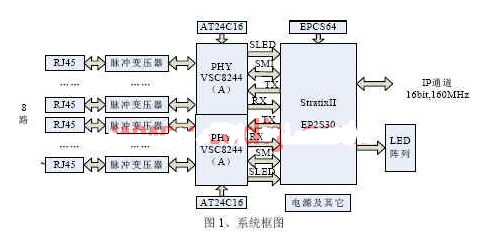

系統(tǒng)框圖如圖1所示:

本系統(tǒng)主要采用Altera公司的StratixII系列FPGA芯片EP2S30為主處理芯片,通過Vitesse公司的PHY芯片VSC8224及相關(guān)的外圍電路組成,實現(xiàn)了8路千兆以太網(wǎng)電信號中IP數(shù)據(jù)收發(fā)的功能。VSC8224主要實現(xiàn)物理層上的比特流和鏈路層上的數(shù)據(jù)相互轉(zhuǎn)換。IP數(shù)據(jù)接收和輸出部分由EP2S30通過VHDL程序來實現(xiàn)。EP2S30在整個系統(tǒng)中起著核心作用,它將2片VSC8224送來的數(shù)據(jù)進行重組,將MAC幀中的IP數(shù)據(jù)提取出來,保存在緩沖存儲器中,最后將8路數(shù)據(jù)依次從IP通道輸出給另外的設(shè)備,同時EP2S30也接收其它設(shè)備送來的IP數(shù)據(jù),然后封裝成MAC幀通過VSC8224發(fā)送到以太網(wǎng)上。EP2S30也控制LED陣列來指示當(dāng)前各個網(wǎng)口的連接狀態(tài)及系統(tǒng)工作狀態(tài)。

3、系統(tǒng)硬件設(shè)計

EP2S30是Altera公司推出的StratixII系列FPGA中的一款,它具有非常豐富的I/O資源,支持多種電平標準,它內(nèi)部資源豐富,可以實現(xiàn)復(fù)雜的應(yīng)用,特別是它內(nèi)部集成了M512/M4K/MRAM三種片上RAM,而且數(shù)量眾多,可以將它們配置成單口/雙口/FIFO等多種存儲器,特別適合大數(shù)據(jù)量的存儲轉(zhuǎn)發(fā)。

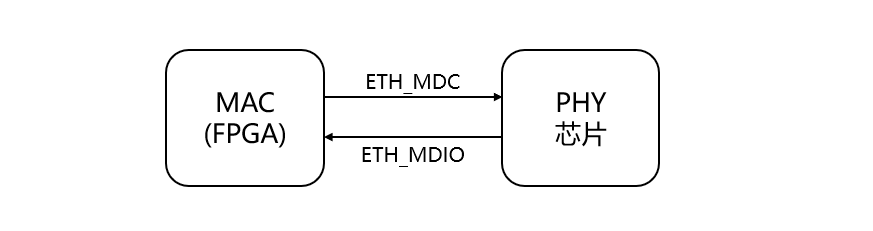

VSC8224是Vitesse公司推出的具有4個口的低功耗、支持10/100/1000BASE-T和1000BASE-X的高性能以太網(wǎng)PHY芯片。VSC8224支持最新的RGMII V2.0標準,這為PCB板設(shè)計提供了極大的便利,無須考慮非常嚴格的延時要求。圖1中2片VSC8224與FPGA之間的連接就是采用的RGMII接口的方式。VSC8224有3種配置方式可供選擇,這里使用EEPROM(AT24C16)對它進行配置,先將配置內(nèi)容通過編程器固化到EEPROM中,VSC8224在上電或者復(fù)位之后自動從EEPROM中讀取出配置數(shù)據(jù)來自己進行配置。FPGA通過2線的SMI串行管理接口對VSC8224內(nèi)部的狀態(tài)寄存器進行訪問,讀出VSC8224的工作狀態(tài),以確定進一步的操作。FPGA通過VSC8244的2線的串行LED狀態(tài)輸出口來讀出4個端口的狀態(tài),然后通過驅(qū)動器驅(qū)動發(fā)光二極管發(fā)光,這為設(shè)計提供了極大的靈活性,可以控制發(fā)光二極管顯示多種狀態(tài)。

4、 MAC控制器的VHDL實現(xiàn)

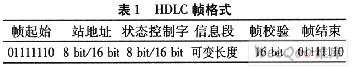

本系統(tǒng)采用VHDL實現(xiàn)MAC控制器和IP數(shù)據(jù)的接收與輸出。MAC幀的格式如圖2所示:

從MAC幀格式,可以看出,在接收的過程中只要我們找到了先導(dǎo)碼和分界符后就可以根據(jù)MAC幀格式得到整個MAC幀,進而根據(jù)長度/類型來判斷此MAC幀的內(nèi)容,從而獲得MAC幀中的IP數(shù)據(jù)。發(fā)送IP數(shù)據(jù)的過程是接收IP數(shù)據(jù)的逆過程,只要按照MAC幀的格式將IP數(shù)據(jù)封裝在一個MAC幀中,再通過PHY芯片依次發(fā)送出去就能實現(xiàn)IP數(shù)據(jù)的傳輸。

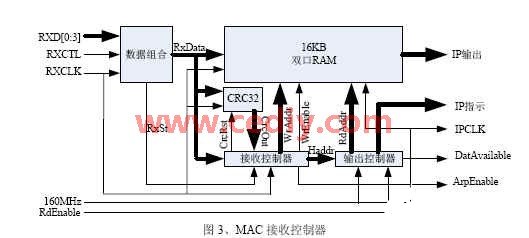

FPGA主要實現(xiàn)MAC幀的收發(fā)、MAC幀的組裝和分解、IP數(shù)據(jù)的收發(fā)功能,利用VHDL模塊化設(shè)計的優(yōu)點,只要實現(xiàn)1路的功能,另外7路就能很容易實現(xiàn)了。本文主要介紹MAC接收控制器的設(shè)計,這里利用VHDL設(shè)計如圖3所示的MAC接收控制器。

如圖3所示,根據(jù)RGMII接口規(guī)范,RXCLK為VSC8224從接收數(shù)據(jù)中提取的125MHz接收時鐘,RXD[3:0]和RXCTL在RXCLK的上下沿都有效,RxSt為RXCTL在RXCLK上下沿的與,RXD數(shù)據(jù)相當(dāng)于一個4bit×125MHz的DDR信號,為了便于后期處理,將數(shù)據(jù)組合成一個8bit×125MHz的信號。這一部分由圖3中的數(shù)據(jù)組合模塊組成。

為了實現(xiàn)MAC巨幀的處理,充分利用FPGA資源,實現(xiàn)異步數(shù)據(jù)的同步輸出,為每一路千兆以太網(wǎng)都生成了一個16K字節(jié)的雙口RAM作為緩沖器,雙口RAM的輸入是8比特,輸出為16比特的數(shù)據(jù),同時輸入時鐘是各路提取的125MHz的時鐘,輸出為同源時鐘產(chǎn)生的160MHz時鐘,這樣能夠?qū)崿F(xiàn)了異步信號的同步輸出。

IP數(shù)據(jù)的提取和存儲由接收控制器來實現(xiàn),IP數(shù)據(jù)的輸出由輸出控制器來實現(xiàn)。下面就分別介紹這兩種控制器。

4.1 接收控制器

接收控制器主要是由一個寫地址控制器和一個有限狀態(tài)機組成。

寫地址控制器主要控制3個信號,一個是14bit的寫地址寄存器WrAddr,一個是14bit的寫起始地址寄存器Haddr和一個寫使能WrEnable信號。在每次寫一幀數(shù)據(jù)之前都將寫起始地址寄存器的值賦給寫地址寄存器。在每幀數(shù)據(jù)CRC校驗正確之后,修改Haddr的值為當(dāng)前WrAddr的值加1,如果CRC校驗有誤則不修改Haddr的值,則下一幀從原來的地址開始,覆蓋上一幀接收錯誤的數(shù)據(jù)。由于雙口RAM的輸入是8bit,輸出為16bit,而且IP數(shù)據(jù)總長度可能為奇數(shù)也可能為偶數(shù),為了便于后面的數(shù)據(jù)輸出,Haddr的值始終應(yīng)該為偶數(shù),當(dāng)CRC校驗無誤后,如果IP數(shù)據(jù)包的長度為奇數(shù),應(yīng)將Haddr自動加上1變?yōu)榕紨?shù),作為下一次寫地址的起始地址。WrAddr在達到0x3FFF之后自動回到0x0000繼續(xù)遞增。

根據(jù)MAC幀格式,接收狀態(tài)機分別設(shè)置了9個狀態(tài):idle, preamble, sfd, destaddr, souaddr, typ_len, payload, padding, fcs。當(dāng)RxSt為0時,接收狀態(tài)機始終處于idle狀態(tài)。當(dāng)RxSt為1時,接收狀態(tài)機開始監(jiān)視RxData上的數(shù)據(jù),如果為0x55,則由idle態(tài)進入preamble態(tài),如果滿足7個連續(xù)的0x55,則進入sfd狀態(tài),否則返回idle狀態(tài)。在sfd狀態(tài)下,如果此時RxData上的數(shù)據(jù)為0xD5,則進入下一個狀態(tài),否則返回到idle狀態(tài)。在destaddr和souaddr狀態(tài)下,接收控制器可以獲得目的MAC地址和源MAC地址。在typ_len狀態(tài)下,接收控制器可以獲得該MAC幀的類型或長度,由于該系統(tǒng)主要是處理IP數(shù)據(jù),所以只關(guān)心類型為0x0800的IP數(shù)據(jù)和類型為0x0806的Arp請求幀。如果接收的類型不是0x0800或0x0806則放棄這次接收,返回到idle狀態(tài)。如果為Arp請求幀,在接收完后幀校驗無誤則使能ArpEnable信號,使能Arp應(yīng)答模塊發(fā)送Arp應(yīng)答幀。如果為IP數(shù)據(jù)包幀,在payload狀態(tài)下,如果destaddr狀態(tài)獲得的目的MAC地址與自身的MAC地址一致則繼續(xù)進行接收,否則放棄這次接收。在數(shù)據(jù)接收完之后,如果總長度大于46字節(jié),則進入fcs狀態(tài),以獲得幀校驗結(jié)果;如果長度小于46字節(jié),則還要進入padding狀態(tài),之后才能進入fcs狀態(tài)。在fcs狀態(tài)之后,將獲得的幀校驗結(jié)果和CRC32模塊計算獲得的結(jié)果進行比較,以保證傳輸?shù)恼_性。

4.2 輸出控制器

與接收控制器一樣,輸出控制器也是由一個讀地址控制器和一個有限狀態(tài)機組成。

讀地址控制器有一個13bit的讀地址信號RdAddr,這個讀地址信號與寫控制器輸出的寫起始地址信號Haddr的高13bit進行比較,如果相等則表明當(dāng)前雙口RAM中無新的IP數(shù)據(jù),如果不相等則表明RAM中至少有一幀新的數(shù)據(jù)。此時輸出一個DatAvailable信號給頂層模塊,頂層模塊根據(jù)各路情況,輸出一個RdEnable信號給下層模塊,下層模塊將RdAddr信號遞增以讀出RAM中的數(shù)據(jù),當(dāng)達到0x1FFF時自動回到0x0000進行遞增。

由于保存在RAM中的數(shù)據(jù)包括MAC幀的目的地址、源地址、類型/長度和數(shù)據(jù)部分,所以輸出狀態(tài)機設(shè)置了5個狀態(tài):Ridle,Rdestaddr,Rsouaddr,Rtyp_len,Rdat。在RdEnable信號無效時,狀態(tài)機始終處于Ridle狀態(tài),當(dāng)RdEnable信號有效時,由Ridle狀態(tài)依次進入Rdestaddr、Rsouaddr和Rtyp_len狀態(tài)。IPvalid用于指示IP數(shù)據(jù)有效,IPhead指示IP包的第一個字節(jié),IPtail指示IP包的最后一個字節(jié),HalfB用于指示在IP數(shù)據(jù)包為奇數(shù)時,IP包輸出的最后一個16bit數(shù)據(jù)的高8bit為有效的IP數(shù)據(jù)。IPCLK為160MHz的時鐘,是由外部輸入的50MHz時鐘經(jīng)過FPGA內(nèi)部的鎖相環(huán)得到。

4.3 頂層模塊設(shè)計

頂層模塊主要是協(xié)調(diào)與控制8路模塊的工作。頂層模塊依次對每一路進行輪詢,由于下層模塊的RAM中一旦有新的IP數(shù)據(jù)就會輸出一個DatAvailable信號,從第一路到第8路依次查詢各路的DatAvailable信號,如果有效則輸出一個RdEnable信號給該模塊,讀出一幀IP數(shù)據(jù)包。當(dāng)一幀IP數(shù)據(jù)包輸出后繼續(xù)進行下一路的查詢,而不管這一路是否還有新的IP數(shù)據(jù)沒有讀出,如果還有數(shù)據(jù)沒有讀出,在下次輪詢的時候再讀出,這樣將減小因為某一路一直占用IP數(shù)據(jù)輸出通道而其他路無法輸出IP數(shù)據(jù)而發(fā)生雙口RAM溢出的可能。

5 、結(jié)論

本文所設(shè)計的千兆以太網(wǎng)IP數(shù)據(jù)傳輸設(shè)備通過在現(xiàn)場的調(diào)試,運行良好,狀況穩(wěn)定,誤碼率低,而且支持IP數(shù)據(jù)包長達8K字節(jié)的巨幀,提高了網(wǎng)絡(luò)利用率,達到了高速測控數(shù)據(jù)傳輸?shù)囊蟆T撓到y(tǒng)的研制為儀器接入網(wǎng)絡(luò),利用網(wǎng)絡(luò)來收發(fā)測試數(shù)據(jù)成為可能,為網(wǎng)絡(luò)化儀器和網(wǎng)絡(luò)化測控系統(tǒng)的發(fā)展提供了經(jīng)濟可行的高速數(shù)據(jù)傳輸手段。

本文作者創(chuàng)新點:利用FPGA片上RAM為每一路千兆以太網(wǎng)設(shè)計了一個數(shù)據(jù)緩沖器及一個MAC接收控制器,解決了多路IP數(shù)據(jù)收發(fā)和異步數(shù)據(jù)同步輸出的問題。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論