1 引言

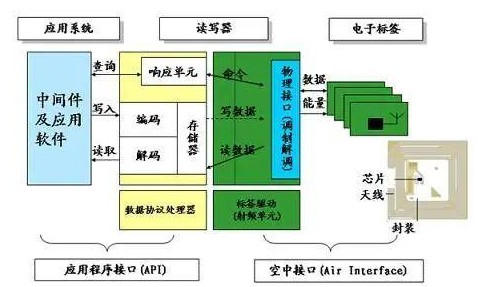

射頻識別技術(RFID)是利用射頻方式進行遠距離通信以達到物品識別目的,可用來追蹤和管理幾乎所有物理對象。在工業自動化、商業自動化、交通運輸控制管理、防偽等眾多領域,甚至軍事用途都具有廣泛的應用前景,并且引起了廣泛的關注。RFID系統一般包括讀寫器和電子標簽(或稱應答器)2個部分。RFID電子標簽(Tag)由芯片與天線(Antenna)組成,每個標簽具有惟一的電子編碼。標簽附在物體上以標識目標對象。RFID讀寫器(Reader)的主要任務是控制射頻模塊向標簽發射讀寫信號,并接收標簽的應答。對標簽信息進行解碼,并將信息傳輸到主機以供處理。根據應用的不同,閱讀器可以是手持式或固定式。本文重點介紹的就是讀寫器的開發。

EPC規范已經頒布第一代規范。規范把標簽細分為Class0,Class1,Class2三種。其中Class0和Class1標簽都是一次寫入多次讀取標簽,Class0標簽只能由廠商寫入信息,用戶無法修改,因而又稱為只讀標簽,主要用于供應鏈管理)Class1則提供了更多的靈活性,信息可由用戶寫入一次。Class0和Class1標簽采用不同的空中接口標準進行通信,因此兩類標簽不能互操作。Class2標簽具備多次寫入能力,并增加了部分存儲空間用于存儲用戶的附加數據。Class2標簽允許加入安全與訪問控制、感知網絡和AdHoc網絡等功能支持。目前EPCglobal正在制定第二代標簽標準,即UHFClasslGeneration2(C1G2)。C1G2具有隨時更新標簽內容的能力,保證標簽始終保存最新信息。EPC規范l_0版本包括EPCTag數據規范、Class0(900MHz)標簽規范、C1ass1(13.56MHz)標簽接口規范、Classl(860~930MHz)標簽射頻與邏輯通訊接口規范、物理標識語言(PhysicalMarkupLanguage,PML)。

本文重點介紹EPCClass1讀寫器系統設計、數字部分設計及FPGA在數字實現上的應用。由于U頻段RFID技術的應用還處在早期的發展階段,符合EPCClass1協議的讀寫器在國內還沒有相關產品面世。本文對相關開發有一定的參考價值。

2 EPCClasslb系統設計

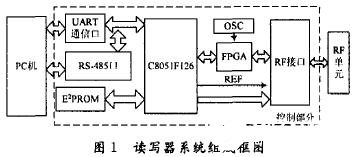

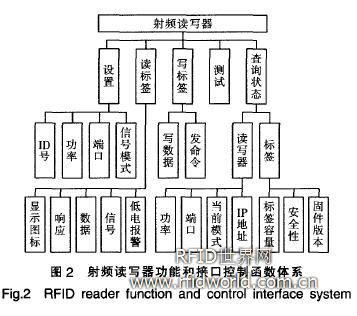

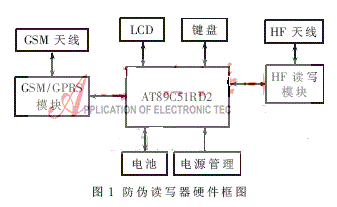

一個完整的RFID系統包括:讀寫器、天線、標簽和PC機。讀寫器完成對標簽(Tag)的讀寫操作。通過RS232或RS485總線完成PC機的命令接收和EPC卡號的上傳。圖l是讀寫器的系統組成框圖。讀寫器組成包括與PC機的串口通信部分、單片機和FPGA組成的數字部分、射頻部分。RF單元實現和標簽的通信,數字部分完成對射頻部分的控制、回波命令解析PC機接收卡號實現上位機的控制。下面對各模塊做簡單介紹。

2.1 PC端

RFID系統一般要將標簽信息讀取到計算機上,然后等待處理用戶通過PC機可以實現讀寫器控制,完成對標簽的讀寫操作。讀寫器與PC機通信是基于RS232總線,糾錯算法是CRC—CCITT算法。

2.2射頻模塊

讀寫器對標簽的讀寫是通過發送射頻能量和對回波實現的。射頻模一方面將數字模塊送來的信息完成調制并發送。標簽應答,射頻模塊接收回波信號將他解調成基帶信號,送到數字模塊。

2.3數字模塊

數字模塊由單片機(cygnalC8O51F126)、存儲器(24Cz56),FPGA(xlSlOO)組成單片機的功能有:

(1)實現與PC機通信,接收PC機命令,完成解析下傳到FPGA

(2)將FPGA送來的EPC卡號加算CRC—CCITT校驗上傳PC機。擇Xilinx公司ISE6.2,仿真軟件為Modelsim5.7。設計實現采取原理圖和VHDL語言相結合的原則。頂層模塊采用原理圖設計,功能模塊采用VHDL語言實現。

(3)解決多卡碰撞,實現多卡讀取。由于FPGA實現多卡讀取算法非常消耗FPGA資源,而且需要FPGA有大量的存儲器資源存放讀到的卡號,成本較高。而如果由PC機實現多卡讀取算法,則讀取速度很難提高。

(4)實現對射頻模塊的鎖相環頻率控制以及功率控制讀寫器發射功率常需要調整,而且讀寫器有時需要在不同射頻頻率,甚至跳頻下工作。單片機通過對射頻模塊的鎖相環控制實現對射頻頻率和功率的控制。

單片機采用CYGNAL公司的C8051F126。內部有128k的FLASH存儲器和8k的RAM,可以在5OMHz主頻下工作。

FPGA實現EPCClassl通信協議,接收單片機控制命令,將命令按照協議標準編碼送到射頻模塊調制并發送,然后解調并接收射頻模塊送來的回波基帶信號,將得到的標簽信息發送給單片機。FPGA實現的EPCClassl命令的基本命令包括scrollid,scrollallid,pinged,quiet,talk,kill;編程命令programid,verifyid,lockid,eraseid這些命令包括命令的發送和回波的解析。根據發送命令不同,對應的發送命令格式也不相同,分為2類。回波信號格式也根據命令的不同分為2類。下面介紹FPGA實現的EPCClass1協議。

3FPGA實現的信號調制解調

3.1FPGA器件及開發平臺

FPGA選擇Xilinx公司的SPARTIIXC2S100規模為1O萬門,系統時鐘選擇40MHz,滿足要求。開發軟件選擇Xilinx公司ISE6.2,仿真軟件為Modelsim5.7。設計實現采取原理圖和VHDL語言相結合的原則。頂層模塊采用原理圖設計,功能模塊采用VHDL語言實現

3.2結構框圖

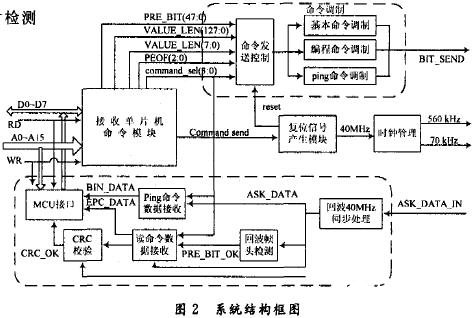

從系統的結構圖可以看出FPGA實現的調制解調部分包括:單片機接口(單片機的命令接收模塊、向單片機發送數據模塊)、復位信號產生模塊、命令調制模塊、命令接收模塊。

單片機向FPGA發送數據采用對地址操作方式,單片機對FPGA讀取數據采用查詢方式。FPGA整個工作過程:FPGA接收單片機控制命令,接收單片機命令模塊將所收到的命令賦值給相應寄存器,同時復位信號產生模塊根據單片機發送的命令產生復位信號(單片機寫FPGA過程即為復位)。命令調制模塊根據單片機送來的命令以及相應控制字,輸出相應的調制信號(bit—sent)輸出到射頻模塊。接收模塊始終在檢測回波數據,當檢測到回波數據的幀頭有效時通知讀命令數據接收模塊接收數據。同時將接收到的數據送CRC校驗模塊校驗,數據接收完成,CRC校驗也即完成,CRC校驗模塊校驗成功即產生CRCOK=l表示讀卡號成功,單片機查詢到此位為高時通過MCU接口模塊讀卡號和CRC。在Ping命令時,Ping命令接收模塊判斷命令發送模塊此時發送的命令類型。如果為Ping命令時,則接收數據,將接收的各槽數據及狀態信息放在BINDATA寄存器中。

3.3關鍵功能模塊

(1)命令調制模塊

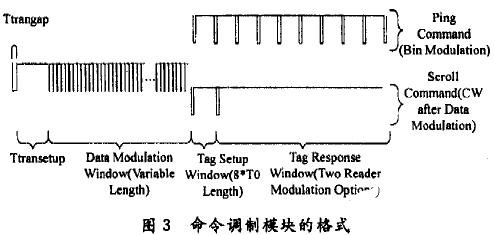

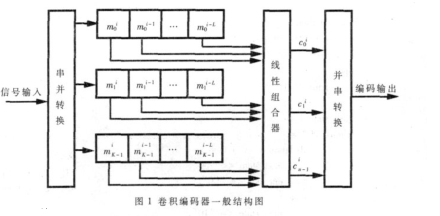

命令調制模塊發送的命令必須符合EPC規范對信息編碼要求以及命令格式要求。信息編碼占空比為1/8時鐘表示“0”,占空比為3/8時鐘表示“l”。命令格式要求如圖3所示,根據EPC規范,可以將命令格式分為3種,分別為ping命令格式、寫卡(program)命令格式、讀卡(scrolled)命令格式,具體命令格式參照文獻。命令調制模塊實現3種命令格式的調制。命令調制模塊設計采

(2)Ping命令接收模塊

回波編碼和發送編碼方式不同,Ping命令和scrollid命令回波編碼用“1010”表示l,用“l100”表示0。接收數據模塊必須將回波調制信號解調成~0,1信號。Ping命令是基本多卡操作命令。如圖3所示,Ping命令的標簽應答是在8個槽(bin)中應答,對應著不同的8組標簽。這樣一次Ping命令可以判斷8組標簽。提高了多卡效率.每一個槽(bin)信息用2個寄存器表示,BIN0(1:O)表示卡的狀態信息:有卡、無卡、多卡。BIN(7:O)表示槽的數據。單片機根據槽狀態信息決定是否讀取槽數據.

(3)scollid命令數據接收模塊

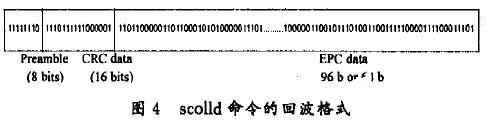

scrollid以及scrollallid,verifyid命令的回波格式相同,接收方式相同.回波格式如圖4所示

一幀完整回波包括幀頭(F7H),16位CRC,96位或64位EPCDATA。接收模塊采用檢測幀頭的方式,通過一個32位移位寄存器(1b數據由4個狀態信息表示)檢測幀頭,幀頭有效則讀數據模塊解調回波數據,解調數據存儲在EPCDATA寄存器中。同時將檢測到的bits送到CRC校驗。

(4)CRC校驗模塊

CRC模塊對數據接收模塊檢測到的數據按照CRC—CCITT算法校驗,校驗通過則產生CRCOK=”1”。單片機根據此狀態讀取EPCDATA。CRC—CCITT算法實現采用串行方式。程序非常簡單,而且節省FPGA資源。

節選代碼如下:

xOr_flag_en: process(elk)begin

if elk== ‘0’ and elk event then

if en ==’l’ then

if crc_bur(15)== ‘1’ then

crc bur《 = (crc bur(14 downto O)&data_in)

xor”OOO1OOOOOO1OOOO1”:

xor_flag《= ‘l’

else erc_buf 《=crc_buf(14 downto O)&data_in :

xor_flag《 = ‘0’;

end if;

else crc_buf《 =”111ll111111llll1”;

endif;

endif;

end prOcess

4 結語

FPGA實現了對EPC Classl 96位和64位卡的讀寫操作命令,讀寫成功率非常高,能實現8 m距離的正常讀,多卡讀取速度快。讀寫器和標簽的讀寫速率為上行70 kb/s,下行140 kb/s。此讀寫器也已經在批量生產,投放市場。

在讀寫器設計過程中仍有幾方面問題需要進一步改善。一是Ping命令回波沒有CRC校驗,所以Ping命令的回波檢測成功率不夠高,影響多卡速度;另一方面,當回波信號信噪比不高時,接收成功率下降速度很快。同時,在讀寫器設計過程中發現EPC標簽的一些問題。其中突出的是,調試發現96位標簽在應答時存在累積周期差,不能和讀寫器的時鐘同步。標簽鎖相環不夠準確,給讀寫器的設計帶來不小難度.

責任編輯:gt

電子發燒友App

電子發燒友App

評論