Freedom E310是第一款基于RISC-V指令集架構的開源商業片上系統,可以依據具體應用場景對其進行深度定制,在簡單介紹Freedom E310的基礎上,給出了將其移植到Altera的DE2開發平臺的詳細步驟。

2017-06-08 15:06:25 5429

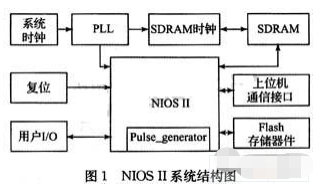

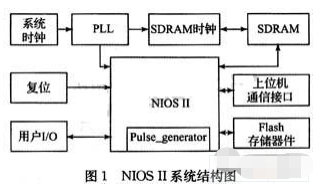

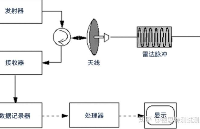

5429 只有設計出了高頻率的、參數化的脈沖發生器,脈沖加工電源的精度、參數化才可以實現。該電源系統中采用的是性價比較好的Altera公司的Cyclone II序列的FPGA芯片EP2C8Q208C7。其邏輯資源足夠實現系統的功能。

2021-02-23 10:01:45 3091

3091

Altera De2——115板卡的配套光盤資料,最近需要用就分享了,在百度盤大概130M鏈接:http://pan.baidu.com/s/1geNk0O7 密碼:dn1t

2017-04-19 13:14:19

AlAltera DE3高階開發平臺簡簡介:Altera DE3開發教學板擁有世界上容量最大、效能最好的FPGA ─ Stratix III,提供工程師以及研究開發者進行開發研究。從其最基本

2010-06-03 16:02:13

`老東西。。。Altera DE2`

2015-11-16 10:59:07

`DE2 FPGA開發板出手 Altera官方正品 EP2C35F672C8N 九成新,配件齊全 698元,可以小刀。南京地區可以當面交易。功能齊全,無任何問題,有興趣的請聯系QQ:865021481`

2016-04-29 21:43:29

DE2開發板TV那塊是怎么回事,怎么實現視頻的播放,是將寫好的視頻代碼下載到板子里,還是將視頻連接到板子上,在連接VGD顯示器就可以播放了。誰能具體講講這塊的內容

2015-11-02 12:49:25

本帖最后由 1477572187 于 2015-9-22 17:13 編輯

DE2開發板資料EP2C35F672C6官方資料,例程,用戶手冊,原理圖

2015-03-14 10:27:47

`工程文件是友晶的DE2_NIOS_DEVICE_LEDHW按照手冊 DE2的USB Device口接到電腦,(我就是把DE2的USB Blaster 和 USB Device 口分別連到了筆記本

2013-08-14 14:38:33

在FPGA上移植最新版本的uClinux,本實驗主要是在DE2上進行。 歷經一個多月的時間,終于在FPGA上移植了uClinux,從開學到現在,,由于版本的問題,加上uClinux更新的比較

2012-02-21 15:47:07

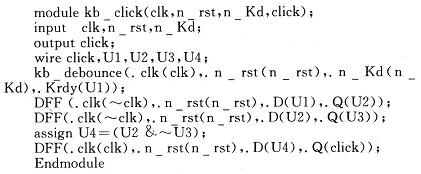

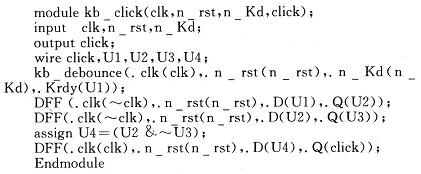

按鍵消抖電路原理是什么鍵控單脈沖發生器電路原理是什么基于FPGA下的按鍵消抖計數器和單脈沖發生器的Verilog HDL語言描述

2021-04-29 06:40:11

新人發帖,求助各位大神!我現在要做一個雙通道的信號發生器,輸出0.5Mhz的正弦波,通過電路設計,來實現信號的脈沖重復頻率調節0.1kHz-2khz。而且信號要求輸出功率在100W以上。信號的輸出幅

2017-08-31 17:09:36

哪個大神能提供一下E題的第五問的信號發生器的FPGA的程序,用的是STM32F1。提供一個標準矩形脈沖信號發生器,要求:a) 頻率為1MHz,誤差的絕對值不大于0.1%;b) 脈寬為100ns,誤差

2016-07-27 21:04:06

求教大神幫忙寫一個脈沖信號發生器的制作程序,萬分感謝。提供一個標準矩形脈沖信號發生器,要求:a) 頻率為1MHz,誤差的絕對值不大于0.1%;b) 脈寬為100ns,誤差的絕對值不大于1%;c

2016-07-27 21:01:32

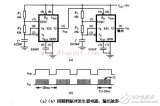

特點是電路簡單,頻率連續可調,可工作在外觸發狀態。當“內觸發”時,主振級是一個多諧振蕩器;當“外觸發”時,主振級就相當于一個單穩態電路了。2、延遲級脈沖信號發生器除了具有主脈沖輸出外,一般還要求有“同步

2017-10-16 10:25:44

特點是電路簡單,頻率連續可調,可工作在外觸發狀態。當“內觸發”時,主振級是一個多諧振蕩器;當“外觸發”時,主振級就相當于一個單穩態電路了。2、延遲級脈沖信號發生器除了具有主脈沖輸出外,一般還要求有“同步

2018-02-27 09:23:52

最近在學習Arduino,用Arduino+LCD1602+AD9954做了一個信號發生器,想增加脈沖調制功能,于是準備用TimerOne實現脈沖信號發生器。但出來的信號不正常,不知道什么原因,請

2017-03-04 20:26:45

、TTL、 TRIG、 GATE及或LCD液晶顯示頻率,其與頻率計電路是重疊的。③脈沖信號發生器。能產生寬度、幅度和重復頻率可調的矩形脈沖的發生器,可用以測試線性系統的瞬態響應,或用作模擬信號來測試雷達

2017-06-12 10:46:01

利用FPGA實現信號發生器

2016-08-24 16:24:24

DE2是Altera公司針對大學教學及研究機構推出的FPGA多媒體開發平臺。DE2開發平臺選用的FPGA是CycloneII系列FPGA中的EP2C35F672C6,通過對DE2的學習,我們能夠迅速

2021-07-30 07:28:21

基于ALTERA實現的DDS信號發生器設計

2017-05-12 15:08:10

要求:1.以Altera公司的最新4代FPGA Cyclone Ⅳ系列芯片為核心,以NIOS Ⅱ軟核處理器進行軟件設計。2#無需DAC 與多路模擬開關,由FPGA 產生調制輸出波形信號所需的PWM

2018-12-08 18:07:11

求一個基于FPGA的DDS信號發生器設計,最好有DA模塊和相位累加器模塊的代碼。

2019-03-18 22:09:03

基于FPGA的雙路低頻信號發生器設計摘要 本設計是基于Altera公司的Cyclone II系列EP2C8Q208C8N芯片的雙路低頻信號發生器。系統應用FPGA內部特有的可配置IP核和鎖相環等

2018-08-23 15:32:05

DDS的工作原理和基本結構基于FPGA的DDS信號發生器的設計如何建立頂層模塊?

2021-04-09 06:46:42

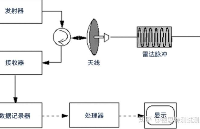

本文利用單片機和自主設計的TH-UWB02超寬帶發射芯片實現了一個超寬帶窄脈沖發射機電路,能夠發送高速率的窄脈沖超寬帶脈沖序列,由接收機解調后可以實現高速數據的無線傳輸,可用于無線數據傳輸、射頻標簽等領域。

2021-03-18 07:22:52

虛擬儀器和LabWindows/CVI簡介基于LabWindows/CVI平臺開發虛擬函數信號發生器

2021-04-25 06:17:45

DE2是什么?如何去實現一種基于DE2的LCD圖形顯示設計呢?

2021-11-09 06:18:39

怎么實現信號發生器系統的FPGA設計?

2021-09-30 06:35:31

m序列信號發生器由那幾部分組成?怎么實現m序列信號發生器的設計?

2021-05-10 06:09:23

怎么實現一種UWB脈沖發生器的設計?

2021-06-07 07:08:40

介紹了DDS的發展歷史及其兩種實現方法的特點,論述了DDS的基本原理,并提出一種基于FPGA的DDS信號發生器的設計方法,使DDS信號發生器具有調頻、調相的功能,最后對其性能進行了分析。實驗表明該系統具有設計合理、可靠性高、結構簡單等特點,具有很好的實用價值。

2021-05-11 06:58:58

為了比較DSP和SOPC技術在電子設計領域的應用,采用泰勒展開法和DDFS技術,分別給出設計方案的硬件電路結構和軟件流程圖,并通過集成開發環境CCS和DE2開發板實現正弦信號發生器。結果表明,采用

2021-05-12 06:15:43

本文在討論DDS的基礎上,介紹利用FPGA設計的基于DDS的信號發生器。

2021-05-06 09:54:10

)。DDS是開環系統,無反饋環節,輸出響應速度快,頻率穩定度高。因此直接數字頻率合成技術是目前頻率合成的主要技術之一。文中的主要內容是采用FPGA結合虛擬儀器技術,進行DDS信號發生器的開發。

2019-09-29 08:08:12

各位大神,怎么設計多通道脈沖信號發生器(方波)?跪求了,非常感謝!

2013-12-30 16:56:39

想用FPGA加DE2板子做一個簡易測距儀,買好超聲波測距儀了,那么問題來了,程序怎么辦,測距核心算法怎么寫,求大牛推薦資料和相關實例。

2015-01-13 16:59:15

` 本帖最后由 kexinqiji 于 2016-6-3 18:22 編輯

各位同志,本人手里有塊閑置Altera DE2 2C35開發板,板子完好,配件齊全, 95新。由于工作變動,打算

2013-11-18 20:08:53

DE2開發板使用手冊,有興趣的人可以下載看一下

2013-06-03 17:58:35

超寬帶UWB是一種利用納秒級窄脈沖發送信息的技術。重點討論了一種采用級聯雪崩晶體管結構UWB極窄脈沖發生器,并對其電路及雪崩晶體管的工作原理進行了具體分析。實驗獲得的UW

2009-07-04 15:09:49 14

14 on the Altera DE2/DE1 and Terasic TREX C1 boards (TR1). Thekit contains hardware design (in Verilog) and software to load the picture takeni

2009-07-20 09:12:09 0

0 1 安裝 Quartus II 5.1 Web Edition Full;2 將 DE2 System 光盤中的全部內容復制到PC 機上,其中DE2_control_panel文件夾內容最為重要;3 將開發板的電源和 USB 線(方形口端接開發板的BLASTER

2009-07-21 16:35:08 0

0 本文介紹基于FPGA 和DDFS 技術,應用Altera 公司的FPGA 開發工具DSP Builder 設計數字移相信號發生器,該數字移相信號發生器的頻率、相位、幅度均可預置,分辨率高,精確可調。且可分

2009-12-18 11:59:54 44

44 根據直接數字合成器的基本原理,給出了基于FPGA的直接數字合成器的設計與實現,利用FPGA有效地擴展了輸出波形的頻率范圍,實現了數字移相信號發生器。該信號發生器主要采用了直接

2010-07-21 17:30:47 69

69 在直接數字頻率合成器(DDS)的基礎上,利用現場可編程門陣列(FPGA)設計一款數字移相正弦信號發生器,并通過Altera公司的DE2開發板來驗證.在輸入環節加入一個數據鎖存器,用“

2010-10-20 16:37:02 129

129 基于FPGA高速、可編程的優點,設計了一款可以靈活改變脈沖輸出周期和輸出個數的周期脈沖發生器。利用VHDL語言編寫了全部模塊,并在Altera公司提供的QuartusⅡ4.1開發軟件上實現了

2010-12-08 15:58:00 52

52 提出了基于復雜可編程邏輯器件(Complex Programmable Logic Device, CPLD)16位的全數字脈沖信號發生器的設計,可產生周期、占空比均可調的高穩定性脈沖。此設計方法可用于DDS函數信號發生

2010-12-09 16:48:29 86

86 基于ECL門電路的UWB信號發生器的設計

0 引 言

超寬帶(Ultra Wide Band,UWB)技術在通信時,不使用載波電路,而是通過發送納秒級脈沖傳輸數據的,因此具有發

2009-11-20 11:04:47 1459

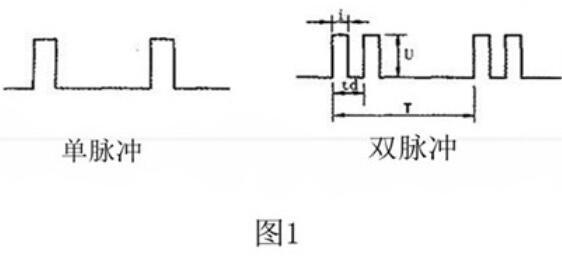

1459 FPGA開發中按鍵消抖與單脈沖發生器電路

FPGA開發中常用到單脈沖發生器。一些文章介紹過產生單脈沖的電路,產生的單脈沖脈寬和相位都不能與時鐘同步,只能用在

2009-12-31 10:36:52 2715

2715

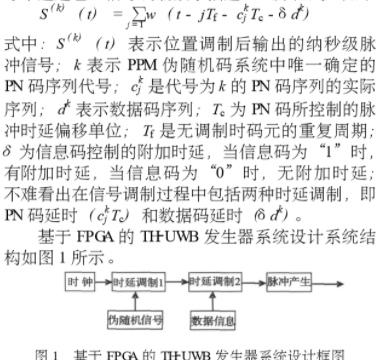

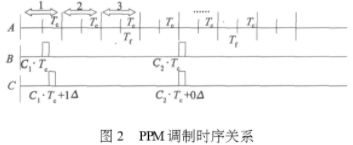

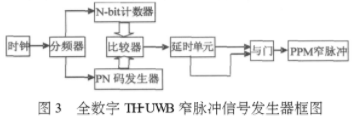

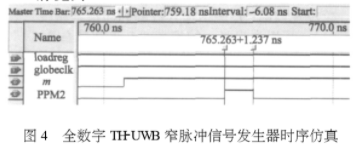

傳統數字通信是通過在信道中發送包含信息的模擬波形來實現通信的,而超寬帶(UWB)通信是通過發送和檢測極窄脈沖序列來實現通信。這種脈沖的脈寬只有1個多ns,有的甚至小

2010-10-26 10:50:42 997

997

DE2 板是以CycloneII 2C35FPGA為特點的672 針引腳的包裝。板上所有重要的部件都與板上的芯片相連,使用戶能夠控制板上各種的操作

2011-02-15 15:41:38 64

64 針對跳時超寬帶(TH-UWB)系統,提出了一種基于特殊訓練序列的同步捕獲算法,該算法使用寬度為一個信息符號的滑動時間窗對接收信號依次截取,通過設計一種特殊的訓練序列使得相鄰兩段

2011-04-19 19:00:10 18

18 FPGA實現智能函數發生器設計介紹了一種基于 FPGA 的智能函數發生器的設計.采用EDA技術對此設計進行功能仿真和時序仿真,在EDA/SOPC系統開發平臺上實現程序下載,同時在示波器上觀察波形

2011-07-25 11:00:53 55

55 為配合地震計電磁信息采集系統對地震計進行標定,設計一款基于FPGA的地震計標定 信號發生器 。以Altera EP2C8T144C8型 FPGA和16位串行DAC芯片DAC8560為核心,利用直接數字頻率合成技術、m序

2011-08-05 14:33:47 49

49 本文在介紹差分跳頻G函數算法原理基礎之上,對短波差分跳頻信號發生器進行了基于FPGA的整體系統優化設計,并分別在軟件和硬件環境下進行了仿真與實現。

2011-08-13 15:04:11 1535

1535

用大多數FPGA都可以實現一個數字UWB(超寬帶)脈沖發生器。本設計可以創建一個兩倍于FPGA時鐘頻率的脈沖信號(

2011-09-06 11:59:48 5280

5280

在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 178

178 詳細分析了雪崩三極管原理,利用雪崩三極管的雪崩特性實現了超寬帶雷達窄脈沖的產生。通過研究分析典型的脈沖產生電路,給出了產生人體生命探測系統的脈沖信號發生器的電路,最后

2011-11-30 16:50:13 54

54 電子發燒友網核心提示:本設計采用DE2、THDB-ADA平臺進行開發。DE2平臺選用FPGA EP2C35F672。THDB-ADA是針對DE2開發板設計的一款子開發板,由FPGA實現對A/D的控制。在系統中只用到了模塊的

2012-11-27 10:36:19 3674

3674 設計采用Altera公司CycloneII系列EP2C5Q208作為核心器件,采用直接數字頻率合成技術實現了一個頻率、相位可控的基本信號發生器。該信號發生器可以產生正弦波、方波、三角波和鋸齒波四種波形。仿真及硬件驗證的結果表明,該信號發生器精度高,抗干擾性好,此設計方案具有一定的實用性。

2013-01-22 14:45:33 472

472 基于FPGA的正弦信號發生器的 技術論文

2015-10-30 10:39:05 20

20 UWB通信系統的TH-PPM信號產生與接收研究,UWB通信系統的TH-PPM信號產生與接收研究

2016-03-01 10:08:19 35

35 DE2 板是以CycloneII 2C35FPGA為特點的672 針引腳的包裝。板上所有重要的部件都與板上的芯片相連,使用戶能夠控制板上各種的操作。DE2 板包括了很多開關(兼有撥動開關和按鍵),發光二極管和七段數碼管。

2017-09-01 16:32:12 25

25 DE2中文說明書

2017-10-16 09:15:12 6

6 DE2中文說明書

2017-10-16 09:12:36 4

4 脈沖信號發生器是 信號發生器的一種。信號發生器按信號源有很多種分類方法,其中一種方法可分為混和信號源和邏輯信號源兩種。其中混和信號源主要輸出模擬波形;邏輯信號源輸出數字碼形。混和信號源又可分為函數

2017-10-26 17:09:54 20777

20777

FPGA和51單片機信號發生器設計

2017-10-31 09:15:37 22

22 源的原始脈沖,原始通過光電耦合器、功率管驅動芯片等硬件調理電路調理后,驅動功率MOSFET的柵極,讓其迅速打開,形成所需的快沿脈沖信號。測試結果證明,該快沿脈沖發生器具有體積小、成本低、可靠性高等特點,并且可實現對脈沖信號的幅

2017-11-14 17:37:08 17

17 基于運放的信號發生器精度低且穩定性和可調節性差,而基于DDS的信號發生器則成本高、電路復雜。為此提出了基于FPGA+PWM的多路信號發生器設計方法。該方法硬件上無需DAC與多路模擬開關,由FPGA產生調制輸出波形信號所需的PWM脈沖波,經二階低通濾波和放大電路后即可得到所需波形信號。

2017-11-18 09:42:01 6332

6332

本文檔內容介紹了基于fpga實現信號發生器,供參考

2018-04-20 15:23:35 65

65 本文首先介紹了脈沖信號發生器的工作原理,其次詳細的闡述了脈沖信號發生器的設計案例。

2018-08-21 17:29:39 18636

18636 脈沖發生器是用來發生信號的系統,產生所需參數的電測試信號儀器。按其信號波形分為四大類。

2019-02-25 14:23:15 13954

13954 的主題。該板具有多種特點,非常適合各大學課程在實驗室環境下的一系列設計項目和非常復雜尖端的數字系統的開發和應用。Altera 公司為DE2 板提供了一套支持文件,例如學習指導,現成的教學實驗練習和豐富的插圖說明。

2019-07-08 08:00:00 7

7 脈沖信號發生器是信號發生器的一種。信號發生器按信號源有很多種分類方法,其中一種方法可分為混和信號源和邏輯信號源兩種。其中混和信號源主要輸出模擬波形;邏輯信號源輸出數字碼形。

2019-12-19 14:59:52 13470

13470

研制了基于現場可編程門陣列 (FPGA)實現的、用于± 50 0 kvar靜止補償器 (STATCOM)的 PWM脈沖發生器。該脈沖發生器通過接口單元接收 DSP寫入的 PWM脈沖寬度數據 ,然后

2020-01-07 11:15:43 24

24 本教程介紹如何將Altera的DE2開發和教育板上的SDRAM芯片與使用Altera SOPC Builder實現的Nios II系統一起使用。本文的討論是基于這樣一個假設:讀者可以訪問DE2板,并且熟悉教程介紹中使用VHDL設計的Altera SOPC Builder的內容。

2021-01-22 15:34:11 9

9 本文檔的主要內容詳細介紹的是如何使用Verilog設計Altera的DE2板上SDRAM存儲器。

2021-01-22 15:34:09 10

10 脈沖發生器是用來發生信號的系統,產生所需參數的電測試信號儀器。按其信號波形分為四大類。

2021-02-02 13:57:32 22708

22708 脈沖發生器是用來發生信號的系統,產生所需參數的電測試信號儀器。按其信號波形分為四大類。 正弦信號發生器。主要用于測量電路和系統的頻率特性、非線性失真、增益及靈敏度等。 隨機信號發生器。通常又分為噪聲信號

2021-10-02 17:59:00 3433

3433 脈沖發生器: 顧名思義,脈沖發生器是一種產生脈沖的信號發生器。這些信號發生器通常采用邏輯脈沖發生器的形式,可以產生具有可變延遲的脈沖,有些甚至提供可變上升和下降時間。

2022-08-02 15:48:42 3762

3762 超聲波脈沖信號發生器采用它激式脈沖清洗方式,先進的軟件控制理念,可完成對超聲波信號發生器的軟啟動,頻率掃描,頻率跟蹤,遠程控制,限流保護,過流保護,超溫保護,負載開路保護等。超聲波脈沖信號發生器優點

2022-12-14 15:50:49 362

362

本設計以FPGA為控制核心,采用直接數字頻率合成(DDS)設計了一款信號可調的信號發生器,采用的FPGA是Altera公司研發的的Cyclnoe II系列,所選用的型號是EP4C6F17C8,外圍

2022-12-22 11:08:05 5

5 脈沖發生器輸出是1嗎?信號發生器怎么只發一個脈沖? 脈沖發生器和信號發生器是常用的電子測量儀器,用于產生脈沖和不同類型的信號。在實際應用中,人們通常會誤解它們的作用和輸出特性,因此需要進行詳細的解釋

2023-08-24 15:18:06 882

882 脈沖發生器是什么意思?脈沖發生器怎么使用? 脈沖發生器是一種電子設備,可以生成不同類型的脈沖信號。這些信號可以被用于各種測試、測量和控制應用,包括電子、通信、無線電、雷達、醫療等領域。它通常由多個

2023-08-24 15:18:09 2128

2128 脈沖信號發生器德思特PG1000系列在雷達系統開發過程中的應用。一次脈沖雷達主雷達產生一個照射目標物的信號,并接受其回波。根據不同的調制方式(模擬調制/數字調制)

2023-10-07 14:32:51 322

322

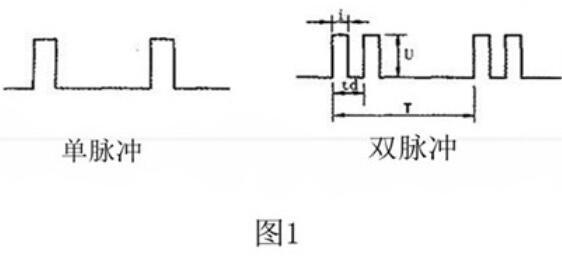

信號發生器如何發出雙脈沖? 信號發生器是一種用于產生各種信號波形的儀器。雙脈沖信號是一種特殊的信號波形,由兩個脈沖組成,通常用于測試和測量系統的響應和性能。在本文中,將詳細介紹信號發生器如何發出

2023-12-21 15:03:35 446

446

電子發燒友App

電子發燒友App

評論