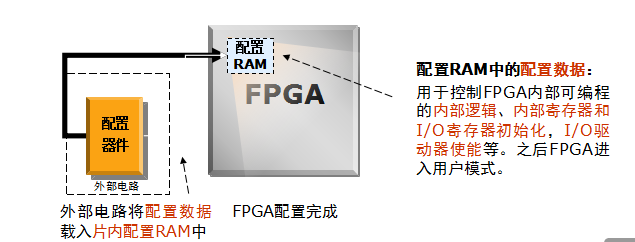

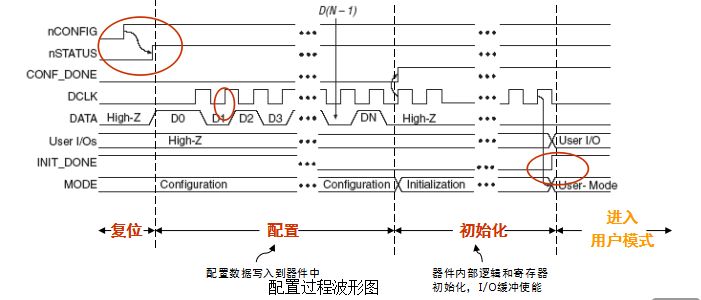

等。 配置( configuration )是對(duì)FPGA的內(nèi)容進(jìn)行編程的過程。每次上電后都需要進(jìn)行配置是基于SRAM工藝FPGA的一個(gè)特點(diǎn),也可以說是一個(gè)缺點(diǎn)。FPGA配置過程如下:

2022-12-26 18:10:00 1780

1780 目前我公司開發(fā)的產(chǎn)品以28335為主控芯片,但在實(shí)際使用過程中,發(fā)現(xiàn)經(jīng)常有一些板卡上電后不工作,人為按復(fù)位按鈕后,工作又正常,檢查3.3V電源與1.9V電源電壓也都正常,電源芯片使用的是TPS767D301,兩路電源是同時(shí)上電,無延時(shí),上電順序滿足28335上電要求,請(qǐng)問是什么方面的問題?

2020-05-20 08:24:33

FPGA在上電完成整個(gè)配置流程之后進(jìn)入到用戶模式。用戶模式是在完成了用戶合計(jì)的數(shù)字邏輯在FPGA片上的搭建之后,開始運(yùn)行該邏輯電路從而相應(yīng)的功能。轉(zhuǎn)自《電子技術(shù)應(yīng)用》

2016-10-02 20:20:32

`FPGA 上電配置時(shí)候IO口會(huì)有一個(gè)短暫的3.3V 10ms 的電平,導(dǎo)致我控制端出現(xiàn)問題,我想問下如何可以避免這個(gè)電平`

2020-11-23 10:31:40

的過程優(yōu)勢:簡單的說,它就相當(dāng)于一張白紙,把需要做的東西全部自己做出來,自由度最高。理論上FPGA可以配置成任何需要的處理器。一般用于通信類的行業(yè)。難點(diǎn): 開發(fā)難度高,門檻也比較高。對(duì)數(shù)電模電的...

2022-02-09 06:14:56

FPGA上電瞬間IO管腳輸出的高電平怎么消除呢?

2023-04-23 14:48:08

下面給大家介紹FPGA LUT的結(jié)構(gòu)

2018-07-09 04:57:10

FPGA與6678調(diào)試SRIO通信過程中,如DSP修改后重新編譯LOAD后,FPGA方無反應(yīng),需要斷電再上電才能通信正常,請(qǐng)問可能是什么原因,根據(jù)論壇例程改編的DSP程序。。。

2018-08-07 07:28:46

FPGA入門知識(shí)介紹近幾年來,由于現(xiàn)場可編程門陣列(FPGA)的使用非常靈活,又可以無限次的編程,已受到越來越多的電子編程者的喜愛,很多朋友都想學(xué)習(xí)一些FPGA入門知識(shí)準(zhǔn)備進(jìn)行這個(gè)行業(yè),現(xiàn)在關(guān)于

2014-08-16 10:32:45

FPGA在軟件無線電中的應(yīng)用本文結(jié)合各種實(shí)際測試介紹了羅德與施瓦茨公司的手持式頻譜儀R&S FSH在發(fā)射機(jī)與天饋線測試、無線電干擾查處以及電磁兼容診斷測試中的應(yīng)用。

2012-08-12 11:55:19

Flash進(jìn)行上電加載,在系統(tǒng)上電穩(wěn)定后,FPGA器件首先需要足夠的時(shí)間用于配置加載操作,只有在這個(gè)過程結(jié)束之后,FPGA器件才能夠進(jìn)入正常的用戶運(yùn)行模式。而上電復(fù)位延時(shí)過短,等同于FPGA器件根本

2019-04-12 06:35:31

的。除此之外,FPGA與傳統(tǒng)的開發(fā)是有很大區(qū)別的,FPGA開發(fā)的是硬件,需要對(duì)底層有深刻的了解,學(xué)習(xí)的過程也是很困難的,在這里分享幾點(diǎn)我的學(xué)習(xí)經(jīng)驗(yàn)。1、對(duì)于任何一門學(xué)問,并不是您有了所有知識(shí)儲(chǔ)備才開始,而是

2019-10-14 10:08:35

本文以Altera公司的FPGA為目標(biāo)器件,通過開發(fā)實(shí)例介紹FPGA開發(fā)的完整的流程及開發(fā)過程中使用到的開發(fā)工具,包括QuartusII、FPGA CompilerII、Modelsim,并重點(diǎn)解說如何使用這三個(gè)工具進(jìn)行協(xié)同設(shè)計(jì)。

2021-04-29 06:04:13

FPGA為了簡化BOM成本(如安路半導(dǎo)體)不需要用戶特別關(guān)注上電時(shí)序,用單電源供電,芯片內(nèi)部控制上電時(shí)序。雖然不合理的上電時(shí)序有時(shí)候也能讓FPGA正常工作,但不正常的上電或掉電過程有可能會(huì)造成瞬時(shí)電流

2019-07-18 14:26:01

FPGA程序?qū)懲昃幾g已用94%的資源。下載沒有問題,上電后,有時(shí)正常運(yùn)行,有時(shí)一上電沒有現(xiàn)象,示波器看管腿的波形也沒有,懷疑FPGA沒有工作,有時(shí)epcs4的程序沒有正確下載。量了FPGA的供電也都正常。到底是什么問題呢?

2015-01-08 15:18:37

cyclone fpga jtag突然不能下載程序,測量了一下電壓,發(fā)現(xiàn)上電后 ,nstatus管教一直是低電平,其他供電正常 ,這是為什么呢?求幫忙解答,謝謝了

2016-09-27 20:40:03

如上,fpga開發(fā)版上電后有個(gè)紅色的燈常亮了(正常情況下是閃爍的),現(xiàn)在也連接不上電腦,是板子壞了嗎?有沒有大神有過經(jīng)驗(yàn)?求告知。

2023-06-01 14:55:08

我第一次做FGPA,PCB完全完成,現(xiàn)在是上電FGPA就燒了,但是不知道從什么地方下手,求大神指教,從哪開始調(diào)試。

2014-11-11 10:39:18

- 2.5VVCCO_35 - 2.5V連接到I / O bank的一些外部電路在2.5V FPGA電源軌之前上電(這超出了我的控制范圍)。這會(huì)以奇怪的方式導(dǎo)致2.5V FPGA電源軌斜坡,請(qǐng)參考附圖。基本上2.5VFPGA

2020-07-30 09:51:29

介紹了STC下載的過程,并設(shè)計(jì)全自動(dòng)STC下載電路,使得整個(gè)下載過程不需要人工干預(yù),這就大大提高的程序的開發(fā)效率,使得通過下載-運(yùn)行-測試 模式完成程序的開發(fā)。STC下載模式介紹STC單片機(jī)IS...

2021-12-01 06:33:37

介紹一種無線電測向技術(shù)

2021-05-26 06:40:24

類故障的概念以及維修加電類故障的基本思路。◎加電類故障基本概念和現(xiàn)象首先筆者先給大家介紹加電類故障的基本概念。所謂加電類故障就是從上電或者復(fù)位到自檢完成這一段過程中電腦所發(fā)生的故障的總稱,通俗點(diǎn)來說就是...

2021-09-08 06:35:10

輸出。而另一個(gè)常用的組合邏輯電路有譯碼的功能,即譯碼器,其邏輯功能是編碼的逆過程,通常是將少比特的輸入編碼翻譯為多比特的數(shù)據(jù)信息輸出。由于兩者的實(shí)現(xiàn)方式非常類似,這里僅以編碼器中的優(yōu)先編碼器為例介紹一下其在FPGA開發(fā)板上的實(shí)現(xiàn)過程。原作者:語雀

2022-07-21 15:38:45

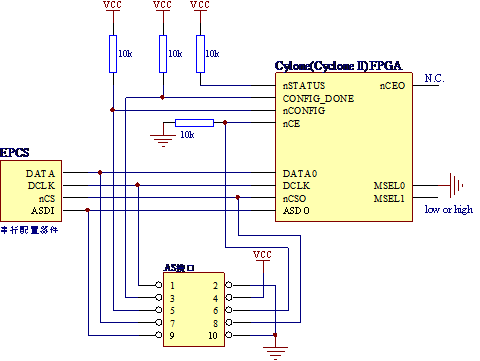

必要的。 本節(jié)介紹設(shè)計(jì)一款FPGA最小系統(tǒng)的過程,通過設(shè)計(jì)來學(xué)習(xí)PCB電路板(四層)和FPGA編程入門知識(shí),具體要求如下: 方案:調(diào)試芯片+FPGA芯片+閃存要求: 01. 了解FPGA芯片最小

2023-03-27 11:57:14

你好,ADI工程師,我現(xiàn)在想用AD9516-4時(shí)鐘芯片產(chǎn)生一個(gè)200M的時(shí)鐘,給FPGA用。當(dāng)我單獨(dú)測試AD9516-4時(shí),能夠產(chǎn)生200M時(shí)鐘,并且多次上電依然可以,但是當(dāng)我把fpga及其外圍電路

2018-12-20 14:15:47

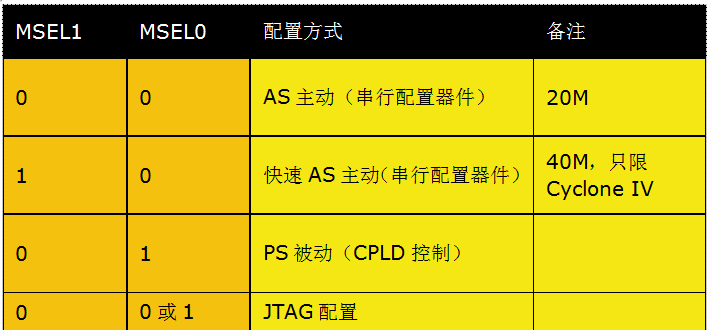

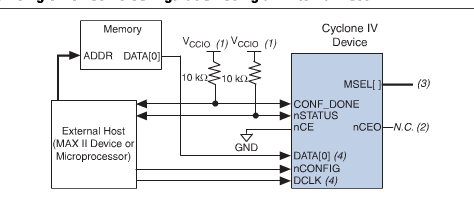

學(xué)習(xí)的時(shí)候了解到FPGA的多路供電要求一定的上電斷電順序,目前在搞Altera的Cyclone IV系列的FPGA,主要有內(nèi)部邏輯供電VCCINT,PLL供電VCCD_PLL,IO口供電VCCIO等

2017-05-18 22:36:29

CPLD和FPGA介紹及應(yīng)用原理[/hide]

2009-10-22 15:19:14

M032芯片的所有GPIO在MCU上電過程直到完成reset的這段過程中,是什么狀態(tài)?項(xiàng)目需要用GPIO控制多個(gè)外部IO,需要在設(shè)備上電過程中有明確的IO狀態(tài)。

I/O Initial State

2023-08-21 07:38:50

1,(正泰抵押研究院與翼輝信息):MCU上電后 到 用戶main函數(shù)運(yùn)行 之間的過程?MCU上電也就想到與重啟復(fù)位,引起復(fù)位的原因有很多:1,上電復(fù)位2,外部產(chǎn)生的手動(dòng)復(fù)位信號(hào)3,執(zhí)行復(fù)位指令4

2021-12-13 08:05:05

和boot1電平對(duì)應(yīng)的意義可能不同,下表是STM32F4xx系列的啟動(dòng)方式選擇 當(dāng)STM32上電時(shí),無論哪種啟動(dòng)模式,程序都將會(huì)從地址0x0000 0000開始執(zhí)行,三種啟動(dòng)模式只是將各自存儲(chǔ)空間映射到地址

2023-04-07 15:10:20

STM32加電啟動(dòng)的具體過程是怎樣的?

2021-11-29 06:57:08

1.同樣的板子,用過好多塊,都沒有問題,就這塊無法加載,應(yīng)該不是PCB設(shè)計(jì)問題。2.我設(shè)計(jì)的是主串加載模式(Master Serial)。硬件上將FPGA的M2~M0直接接到GND上。3.上電以后

2015-08-15 09:20:26

的內(nèi)部的一些特性來試圖解決這個(gè)問題。 要解決這個(gè)問題首先要了解FPGA上電初始化過程,這里我們是以ALTERA的ArriaGX的AS模式來進(jìn)行研究。第一步控制POR時(shí)間 FPGA的AS配置主要分為

2015-01-22 14:41:34

和支撐,十分小巧有特色。下面咱們上電測試一下,確認(rèn)一下整體通電情況,能夠正常上電,而且喇叭還播放音頻。(ps:一定要連接JTAG口,如果在辦公室測試,不想影響他人,可以提前將喇叭插頭拔掉)。 下面咱們

2022-03-08 06:35:09

、第三節(jié)介紹了電荷放大器及和混疊濾波電路的實(shí)現(xiàn)方法,第四節(jié)著重介紹了FPGA的實(shí)現(xiàn)方法,最后介紹了方案的實(shí)際應(yīng)用情況。

2019-07-01 06:11:15

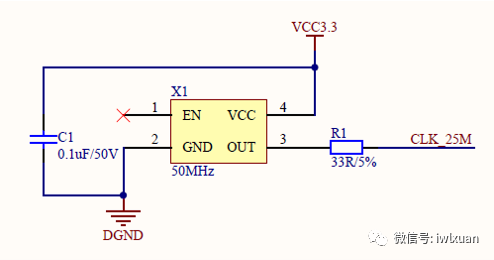

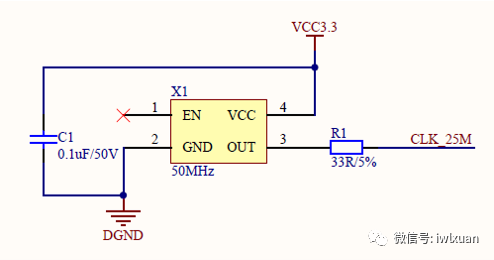

一、本文內(nèi)容本文主要包含以下三個(gè)基本外圍電路的調(diào)試過程與調(diào)試結(jié)果:電源模塊時(shí)鐘模塊復(fù)位模塊二、電源模塊調(diào)試無論對(duì)FPGA還是DSP而言,對(duì)電源的上電順序都有一定的要求,且不同型號(hào)的器件對(duì)電源軌的順序

2021-11-11 06:51:24

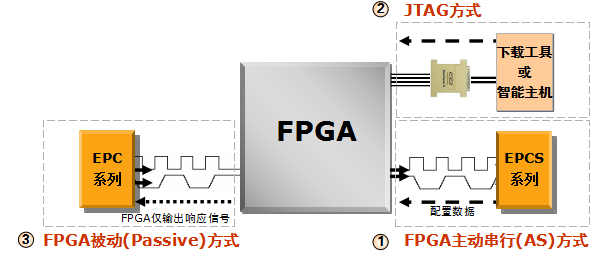

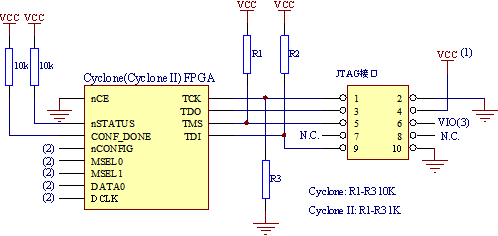

bit文件下載到FPGA或存儲(chǔ)器的任務(wù),另一方面則要完成FPGA上電啟動(dòng)時(shí)加載配置數(shù)據(jù)的任務(wù)。在開始設(shè)計(jì)FPGA的配置電路之前,我們不妨花一些篇幅簡單的了解一下FPGA的配置過程和配置方式。大都數(shù)

2016-08-10 17:03:57

之后最高只能到400M,在全國電設(shè)里能用上么?從今年的題目來看,一屆的頻率比一屆要高,以后的題目估計(jì)不會(huì)再出現(xiàn)低頻題目了。我知道FPGA是并行操作,看過那個(gè)很多人說,ALTERA的芯片最高時(shí)鐘頻率也只能到200M,在高的話處理效果就不會(huì)很好。我就是 想問如果用FPGA的這款 芯片最高可以處理多高頻率的信號(hào)?

2015-09-13 11:25:37

關(guān)于FPGA芯片資源介紹不看肯定后悔

2021-09-18 08:53:05

本文介紹了基于2600系列的IDDQ測試過程與功能實(shí)現(xiàn)。

2021-05-07 06:25:08

使得設(shè)計(jì)調(diào)試和檢驗(yàn)變成設(shè)計(jì)周期中最困難的流程。本文重點(diǎn)介紹在調(diào)試FPGA系統(tǒng)時(shí)遇到的問題及有助于提高調(diào)試效率的技術(shù),通過邏輯分析儀配合FPGA View軟件快速有效的觀測FPGA內(nèi)部節(jié)點(diǎn)信號(hào)。最后提供了FPGA具體的調(diào)試過程和方法。

2019-06-25 07:51:47

產(chǎn)生的問題是在FPGA上電啟動(dòng)時(shí)這部分引腳總是會(huì)快速的閃過一次高電平才恢復(fù)低電平,請(qǐng)問應(yīng)該怎么做才能使避免高電平會(huì)閃一次的這種情況?程序中因?yàn)樾枰獜?fù)位時(shí)保持輸出結(jié)果,所以不能使用復(fù)位信號(hào),關(guān)鍵代碼

2023-04-23 14:53:05

輸出。而另一個(gè)常用的組合邏輯電路有譯碼的功能,即譯碼器,其邏輯功能是編碼的逆過程,通常是將少比特的輸入編碼翻譯為多比特的數(shù)據(jù)信息輸出。由于兩者的實(shí)現(xiàn)方式非常類似,這里僅以編碼器中的優(yōu)先編碼器為例介紹一下其在FPGA開發(fā)板上的實(shí)現(xiàn)過程。原作者:硬木課堂語雀

2022-08-04 17:39:32

大家好,我們正在設(shè)計(jì)一個(gè)基于kintex-7 FPGA的電路板。該板具有DDR,QDR,BPI,以太網(wǎng),UART等外設(shè)。我們有一個(gè)關(guān)于加電排序的查詢。有沒有要求外圍IC在FPGA上電之前應(yīng)該上電,反之亦然。感謝致敬Tarang JIndal

2020-07-31 11:32:50

1、CPU上電后加載程序的流程芯片上電解復(fù)位之后執(zhí)行的第一段程序,在芯片中稱之為Bootrom loader。這部分程序在芯片制造過程中固化到其內(nèi)部的ROM空間,具備只讀屬性,在實(shí)際使用過程中無法

2022-06-21 15:28:35

如何控制FPGA各電源的上電順序呢?請(qǐng)教一下大神

2023-03-27 13:48:32

你好,在我們的研究中,我們正在探索FPGA器件上SRAM的上電狀態(tài)的固有隨機(jī)性。因此,我們現(xiàn)在正試圖在啟動(dòng)后從aVirtex-5器件讀出分配的RAM值。但是,根據(jù)“Virtex-5 FPGA配置指南

2020-06-18 09:26:09

最近在用AD7768在做數(shù)據(jù)采集,采用FPGA控制和處理轉(zhuǎn)換后的數(shù)據(jù),但是將FPGA和AD7768端口鏈接后,每次上電AD都會(huì)發(fā)燙 ,斷開連線后正常,這是怎么回事

2018-08-06 09:17:15

的內(nèi)部的一些特性來試圖解決這個(gè)問題。 要解決這個(gè)問題首先要了解FPGA上電初始化過程,這里我們是以ALTERA的ArriaGX的AS模式來進(jìn)行研究。第一步控制POR時(shí)間 FPGA的AS配置主要分為三個(gè)過程

2015-01-20 17:37:04

嗨,大家好,我遇到了Xilinx ISE映射過程的棘手問題。當(dāng)我綜合我的設(shè)計(jì)時(shí),我得到了一些FPGA資源的利用。雖然在映射過程中映射到FPGA上的LUT時(shí),所有利用率都會(huì)達(dá)到0%。他很可能是由于

2020-06-13 09:57:50

本人做課設(shè),想用FPGA輸出一個(gè)方波作為時(shí)鐘信號(hào),使用FPGA的是Altera公司的EP1C12Q240I7,配置芯片是EPCS4I8,我用QuartusII下載了程序之后,發(fā)現(xiàn)只有上電和手動(dòng)復(fù)位后

2016-12-08 16:20:03

求助:基于SRAM結(jié)構(gòu)的FPGA上電瞬間電流大小如何去評(píng)估,上電瞬間的電流很大,比正常工作電流大很多,如何去評(píng)估?資料上沒找到描述,感謝討論

2019-04-18 16:50:00

求大神詳細(xì)介紹一下FPGA嵌入式系統(tǒng)開發(fā)過程中的XBD文件設(shè)計(jì)

2021-05-06 08:19:58

現(xiàn)在的FPGA還嚴(yán)格要求上電時(shí)序嗎?想請(qǐng)教一下大家

2017-09-26 15:39:07

引言 電源時(shí)序控制是微控制器、FPGA、DSP、 ADC和其他需要多個(gè)電壓軌供電的器件所必需的一項(xiàng)功能。這些應(yīng)用通常需要在數(shù)字I/O軌上電前對(duì)內(nèi)核和模擬模塊上電,但有些設(shè)計(jì)可能需要采用其他序列

2019-07-03 08:15:19

上電過程 上電過程電源不是線性增加,而會(huì)出現(xiàn)電壓降低的現(xiàn)象,如圖所示,稱為上電回溝。 這個(gè)問題覺得應(yīng)該分兩種情況分析: 1. 高速電路上信號(hào)線的回鉤:反射,串?dāng)_,負(fù)載瞬變... 2. 電源電路上的回

2021-12-31 06:59:38

FPGA的仿真與調(diào)試在FPGA開發(fā)過程中起著至關(guān)重要的作用,也占用了FPGA開發(fā)的大部分時(shí)間。所以適當(dāng)減少或簡化FPGA的仿真與調(diào)試過程無疑是對(duì)FPGA開發(fā)的加速,所對(duì)產(chǎn)品成型的時(shí)間。這里我們將利用

2020-04-25 08:00:00

目前,大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運(yùn)行

2019-07-18 08:10:11

Hi all,

請(qǐng)教下Zstack中Coordinator上電過程PANID的選取問題.

跟蹤Zstack代碼最終將調(diào)用NLME接口函數(shù)NLME_NetworkFormationRequest()來

2018-06-01 12:36:31

大家好, 誰能告訴我Spartan-3AN的FPGA上電和閃存配置之間的時(shí)間間隔?謝謝RGDS以上來自于谷歌翻譯以下為原文Hi All, Could anyone tell me the Time

2019-06-27 08:15:46

請(qǐng)問CPLD/FPGA上電初始時(shí)IO口的狀態(tài)是怎么樣的呢?

2023-04-23 14:26:44

本帖最后由 一只耳朵怪 于 2018-6-14 10:48 編輯

請(qǐng)問TMS320F28035上電過程中是否將IO口設(shè)置為輸入狀態(tài)?上拉電阻多大?

2018-06-14 06:26:13

軟件無線電技術(shù)因?yàn)槠潇`活性被廣泛用于無線通信產(chǎn)品和射頻檢測儀器。本文介紹了軟件無線電在射頻檢測儀器和射頻檢測方法上的應(yīng)用。按照軟件無線電原理,將無線產(chǎn)品看作射頻前端+基帶電路+輔助電路的模塊構(gòu)架,就可以用射頻參數(shù)檢測替代昂貴的通信功能檢測,從而提高生產(chǎn)者的市場競爭力。

2019-07-22 07:32:59

FPGA怎么選擇?針對(duì)功耗和I/O而優(yōu)化的FPGA介紹

2021-05-06 09:20:34

概述EasyGo FPGA Solver是EasyGo開發(fā)的專門部署在FPGA 硬件上的解算器軟件。根據(jù)不同的應(yīng)用需求,會(huì)有不同的FPGA Solver 選擇

2022-05-19 09:21:43

簡化Xilinx和Altera FPGA調(diào)試過程:通過FPGAViewTM 解決方案,如混合信號(hào)示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內(nèi)部迅速移動(dòng)探點(diǎn),而無需重新編譯設(shè)計(jì)方案。能夠把內(nèi)部FPGA

2009-11-20 17:46:26 26

26 FPGA整體視頻介紹

視頻教程

2010-11-18 16:22:39 265

265 本文著重介紹了 Xilinx Platform Flash PROM 如何幫助系統(tǒng)和電路板設(shè)計(jì)人員簡化 FPGA 配置設(shè)計(jì)。用于配置 FPGA 的可選解決方案有很多,但它們通常都需要大量的前期設(shè)計(jì)工作和時(shí)間。Platform

2013-03-14 15:18:22 64

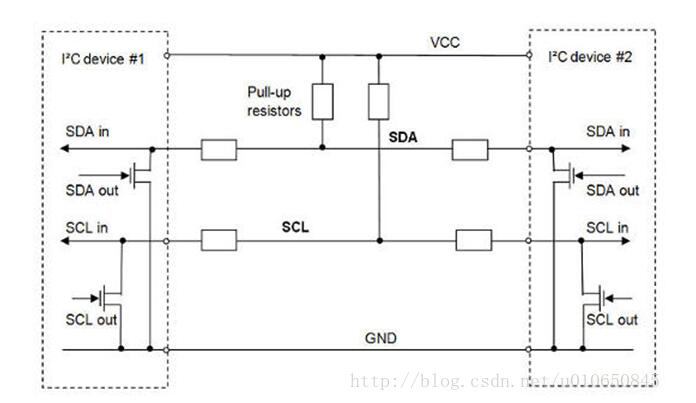

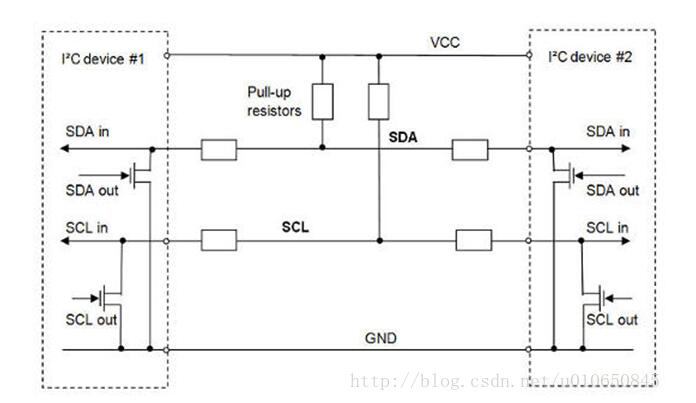

64 本文首先介紹了IIC總線概念和IIC總線硬件結(jié)構(gòu),其次介紹了IIC總線典型應(yīng)用,最后詳細(xì)介紹了IIC總線的FPGA實(shí)現(xiàn)原理及實(shí)現(xiàn)過程。

2018-05-31 10:56:50 6325

6325

本文主要介紹Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 如果你在采用FPGA的電路板設(shè)計(jì)方面的經(jīng)驗(yàn)很有限或根本沒有,那么在新的項(xiàng)目中使用FPGA的前景就十分堪憂——特別是如果FPGA是一個(gè)有1000個(gè)引腳的大塊頭。繼續(xù)閱讀本文將有助于你的FPGA選型和設(shè)計(jì)過程,并且有助于你規(guī)避許多難題。

2020-11-01 09:44:54 1826

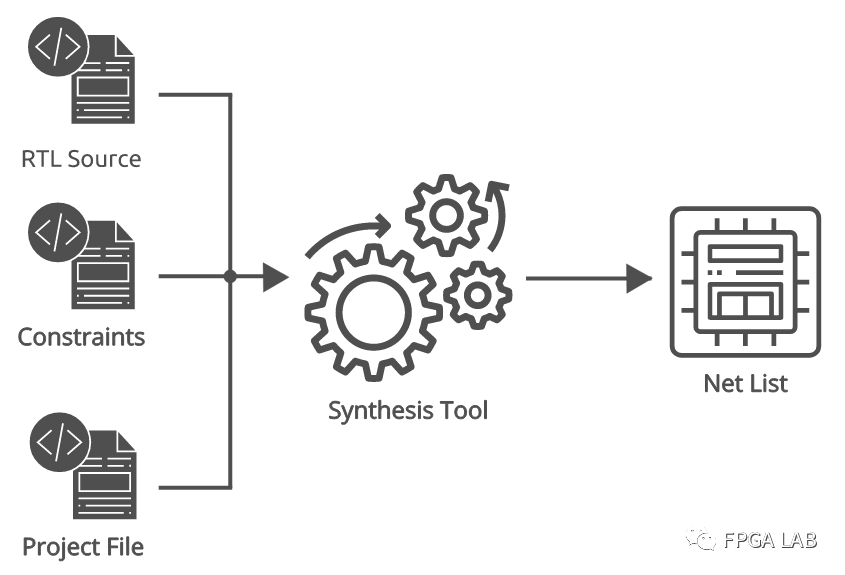

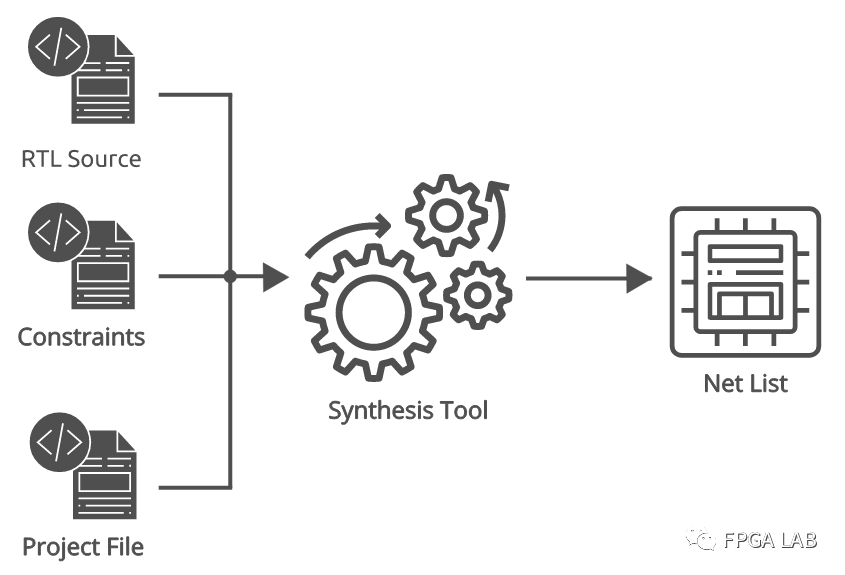

1826 構(gòu)建FPGA的第一階段稱為綜合。此過程將功能性RTL設(shè)計(jì)轉(zhuǎn)換為門級(jí)宏的陣列。這具有創(chuàng)建實(shí)現(xiàn)RTL設(shè)計(jì)的平面分層電路圖的效果。

2023-06-21 14:26:16 511

511

其實(shí)用FPGA做的示波器有很多,開源的相對(duì)較少,我們今天就簡單介紹一個(gè)使用FPGA做的開源示波器:

2023-08-14 09:03:18 881

881 小編在本節(jié)介紹FPGA芯片外圍電路設(shè)計(jì)規(guī)范和配置過程,篇幅比較大,時(shí)鐘的設(shè)計(jì)原則就有17條,伙伴們耐心讀一讀。

2023-08-15 16:18:11 3374

3374

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論