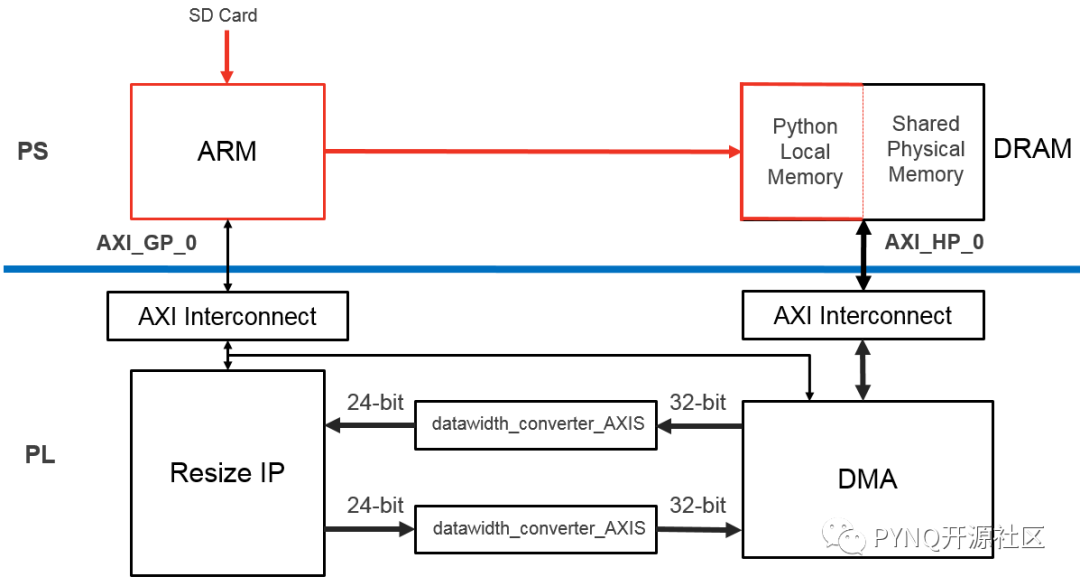

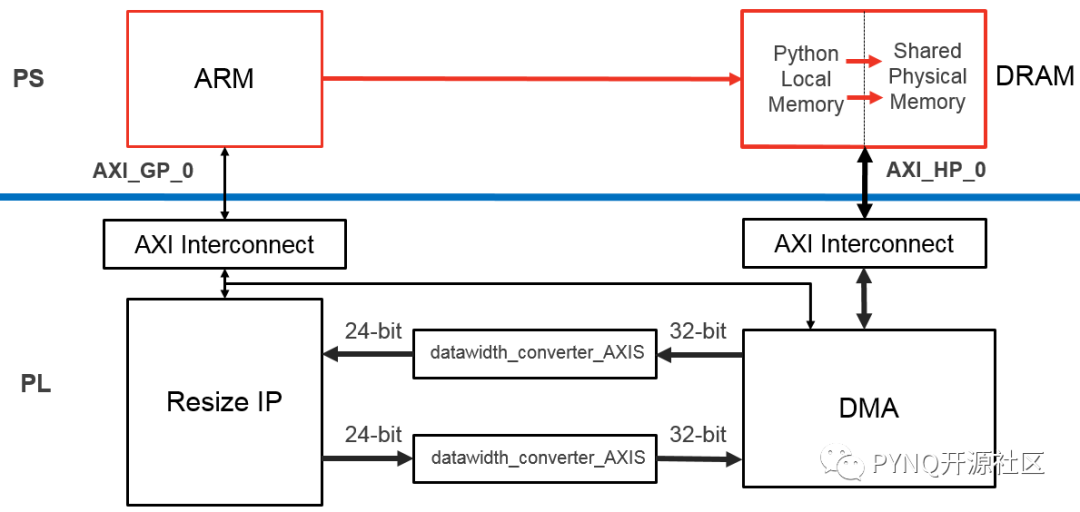

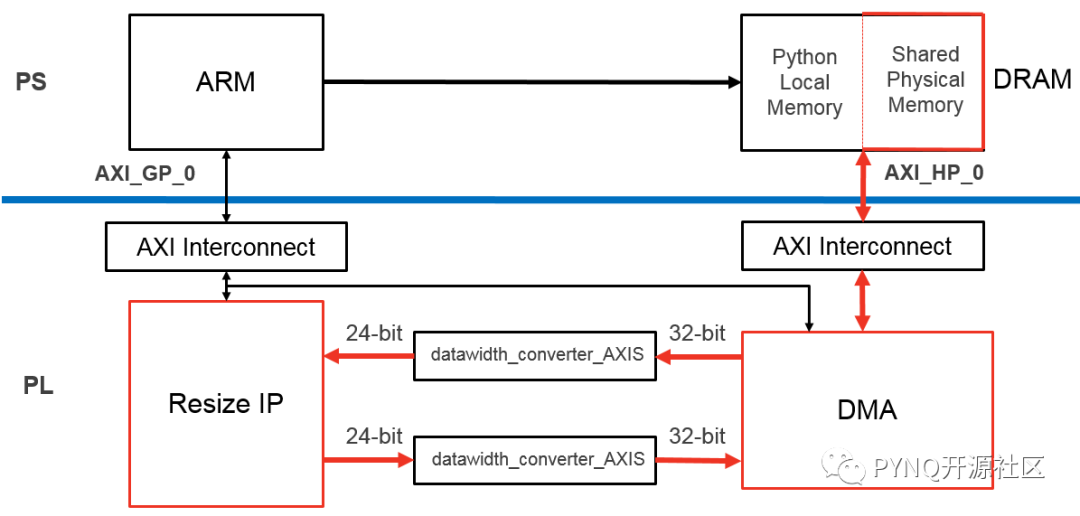

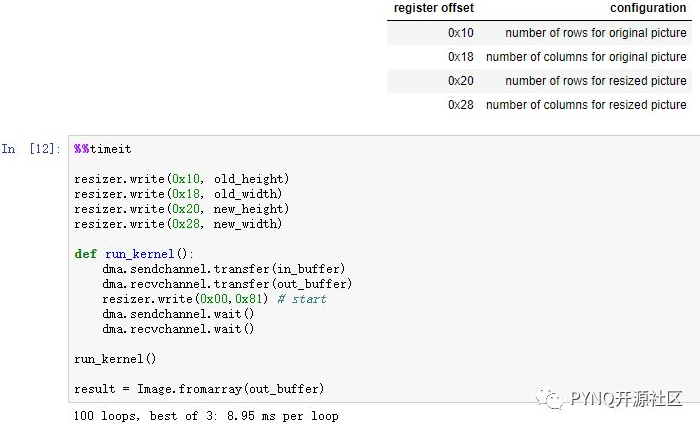

概述 此項(xiàng)目解釋了如何在FPGA上使用resizer IP來(lái)調(diào)整圖像的大小。其中對(duì)比了兩種圖像大小調(diào)整的解決方案的運(yùn)算速度,其中之一為使用Python Image Library通過(guò)軟件算法實(shí)現(xiàn)圖像

2020-11-19 15:29:43 3044

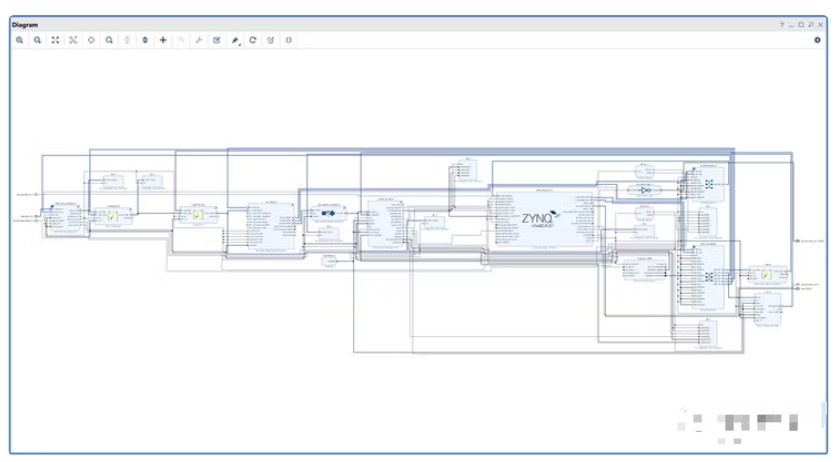

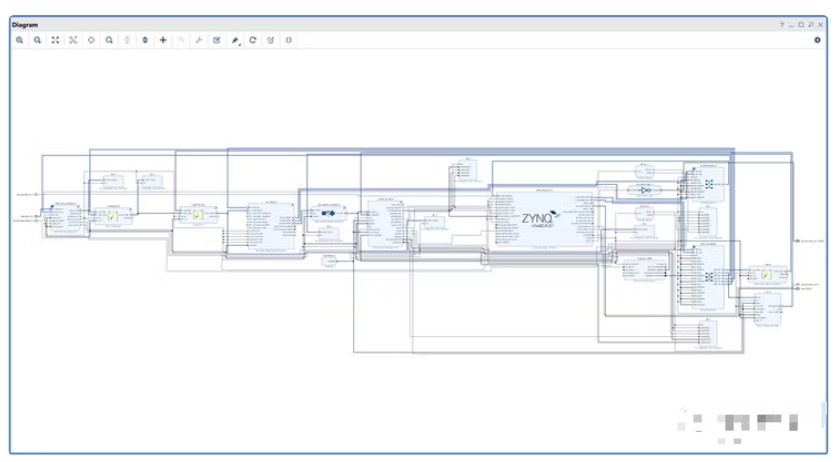

3044 在這個(gè)項(xiàng)目中,我們將探索使用 PCAM(FMC擴(kuò)展板) 和 Display Port 建立和運(yùn)行圖像處理。然后,我們可以添加圖像處理 IP 內(nèi)核以進(jìn)一步展示FPGA的處理圖像的能力。

2022-07-19 09:02:10 1963

1963

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨(dú)立的,只是集成在了一起呢,還是占用了FPGA的資源來(lái)形成一個(gè)RAM?如果我以ROM的形式調(diào)用該IP核,在

2013-01-10 17:19:11

容易就可以在某一個(gè)平臺(tái)上升級(jí)IP特性,甚至根據(jù)需求,隨時(shí)更換成其他協(xié)議的編解碼功能。FPGA的可擴(kuò)展性也是GPU不可比擬的,能非常容易的在同一塊FPGA上pipeline部署編解碼相關(guān)的上下游應(yīng)用;同時(shí)

2019-03-08 10:47:22

TCP/IP協(xié)議:TCP/IP協(xié)議是Internet上使用的主要協(xié)議之一,它定義了數(shù)據(jù)在網(wǎng)絡(luò)中的傳輸方式和處理方式。FPGA可以通過(guò)實(shí)現(xiàn)TCP/IP協(xié)議棧來(lái)支持TCP/IP通信。PCIe協(xié)議:PCI

2023-03-27 09:01:46

FPGA上對(duì)OC8051IP核的修改與測(cè)試FPGA上對(duì)OC8051IP核的修改與測(cè)試單片機(jī)與嵌入式系統(tǒng) 解放軍信息工程大學(xué) 楊先文 李崢引 言20世紀(jì)80年代初,Intel公司推出了MCS-51

2012-08-11 11:41:47

FPGA如何在高清圖像處理領(lǐng)域大展雄圖?

2021-04-29 06:43:01

VerilogHDL來(lái)描述并直接用硬件實(shí)現(xiàn)。即使一些模塊是預(yù)制的IP模塊,這個(gè)任務(wù)仍然是集成這些模塊到一個(gè)完整的設(shè)計(jì)之中。Helion是一家致力于利用FPGA和DSP從事圖像信號(hào)處理領(lǐng)域開(kāi)發(fā)的公司。他們

2012-08-11 11:27:45

有誰(shuí)知道現(xiàn)在國(guó)內(nèi)外有哪些公司賣FPGA的圖像處理相關(guān)的IP核?

2015-04-28 21:34:24

到的一幀圖像數(shù)據(jù)保存到 SRAM 中,此時(shí) DSP 在等待;第一次采樣結(jié)束后,DSP 與 FPGA 進(jìn)行總線切換,分別連接到與上次不同的 SRAM 上,DSP開(kāi)始讀取數(shù)據(jù),FPGA 開(kāi)始采集數(shù)據(jù)。每當(dāng) DSP 和 FPGA 都完成各自的任務(wù)時(shí),就進(jìn)行總線切換,交換連接的 SRAM。

2018-12-10 09:54:23

額外負(fù)擔(dān)。與DSP相比,FPGA結(jié)構(gòu)上的優(yōu)勢(shì)使得其更適合完成并行處理、及結(jié)構(gòu)性強(qiáng)和高速的運(yùn)算。本文基于這種算法理論基礎(chǔ),使用xilinx公司規(guī)模較大的XC4VLXl5系列FPGA,實(shí)現(xiàn)了紅外圖像的實(shí)時(shí)處理

2012-04-27 14:37:03

AD14.1,不知道如何調(diào)整彈出來(lái)的框圖大小,改了很多次就是不對(duì),求助大哥們??還有那個(gè)如何在AD的PCB中顯示引腳的名字,方便以后使用方便

2016-11-29 21:05:45

,整個(gè)處理時(shí)間(包括傳輸時(shí)間)也比單獨(dú)使用CPU要短得多。圖3.由于FPGA在本質(zhì)上是大規(guī)模并行的,因此相比CPU,可顯著性能提升。現(xiàn)在考慮一個(gè)真實(shí)的例子,比如粒子計(jì)數(shù)所需的圖像。首先需要應(yīng)用卷積濾鏡來(lái)

2018-08-03 11:13:19

對(duì)于圖像處理的知識(shí),個(gè)人僅限于研究生時(shí)上過(guò)的數(shù)字圖像處理課程,而對(duì)于FPGA的數(shù)字圖像處理,一直僅限于略(yan)有(gao)耳(shou)聞(di)。國(guó)慶躺尸看了點(diǎn)兒簡(jiǎn)單的FPGA圖像處理,發(fā)現(xiàn)

2022-07-15 14:51:07

通過(guò)resizer把YUV422格式轉(zhuǎn)換為YUV420SP時(shí),寬和高都要32位對(duì)齊,否則生成的YUV420SP數(shù)據(jù)不正確。請(qǐng)問(wèn),對(duì)于D1 720x480的數(shù)據(jù),由于720不能被32整除,應(yīng)該怎么配置呢?

謝謝

2018-06-21 01:52:38

很多初學(xué)labview的朋友們經(jīng)常遇到精確調(diào)整一個(gè)或者多個(gè)控件大小的問(wèn)題,特別是當(dāng)界面已經(jīng)基本完成,需要重新布局的時(shí)候,其實(shí)LV提供了按照像素點(diǎn)調(diào)整大小的工具。下面通過(guò)調(diào)整工具,把上面的布爾控件修改為相同大小的圓形對(duì)話框中的單位為像素點(diǎn),因此可以按照像素點(diǎn)精確調(diào)整控件的大小

2012-12-13 15:42:23

DevelopmentModule)來(lái)實(shí)現(xiàn)。有關(guān)LabVIEW視覺(jué)開(kāi)發(fā)模塊(LabVIEWVision Development Module)的更多信息,請(qǐng)參考下一章節(jié)的鏈接。手動(dòng)調(diào)整圖像大小或?qū)?b class="flag-6" style="color: red">圖像重新采樣

2022-05-16 21:15:57

1、Rockchip SoC上的圖像信號(hào)處理模塊介紹ISP 詳細(xì)信息ISP 包括:MIPI 串行攝像頭接口圖像信號(hào)處理許多圖像增強(qiáng)塊莊稼調(diào)整大小框圖完成的框圖不能從數(shù)據(jù)表粘貼到這里,下圖是一個(gè)抽象

2022-07-14 16:57:54

近年來(lái),隨著信息技術(shù)的發(fā)展,網(wǎng)絡(luò)化日加普遍,以太網(wǎng)被廣泛應(yīng)用到各個(gè)領(lǐng)域。例如在數(shù)據(jù)采集領(lǐng)域,一些小型監(jiān)測(cè)設(shè)備需要增加網(wǎng)絡(luò)實(shí)現(xiàn)遠(yuǎn)程數(shù)據(jù)傳輸?shù)墓δ埽灰切┰O(shè)備上增加一個(gè)網(wǎng)絡(luò)接口并實(shí)現(xiàn)了TCP/IP協(xié)議

2020-03-09 06:50:07

色分離(8位/像素)由rsz_cnt.inptyp參數(shù)設(shè)置。在色分離模式只有一個(gè)顏色分量的大小可以改變一次。例如為了調(diào)整所有的色彩(Y, Cb, and Cr) 在內(nèi)存中的一個(gè)顏色分開(kāi)的圖像,三個(gè)單獨(dú)

2015-09-25 21:26:16

protel 不能調(diào)整room的大小,拖動(dòng)的時(shí)候和原件一起移動(dòng)是怎么回事

2012-06-12 20:31:00

` 本項(xiàng)目利用MP801開(kāi)發(fā)板,通過(guò)攝像頭采集圖像數(shù)據(jù),然后在屏幕上顯示兩種圖像:屏幕有一個(gè)圓,圓內(nèi)顯示經(jīng)過(guò)了邊緣處理的圖像,而圓外則顯示原始圖像(效果如下圖)通過(guò)該工程的學(xué)習(xí),可以學(xué)到如下知識(shí):1

2019-11-29 09:52:21

就不在贅述。2 FPGA實(shí)現(xiàn)如圖1所示,我們要設(shè)計(jì)n行同時(shí)輸出,就串聯(lián)n行。Line_buffer的大小設(shè)置由圖像顯示行的大小(圖像寬度)決定。例如480*272 (480)。下面我們將采用更加靈活

2020-02-17 19:32:54

的EOPB0來(lái)調(diào)整SRAM的大小。一般此擴(kuò)展模式的設(shè)置都建議使用雅特力的ICP或ISP工具來(lái)完成,但在使用者無(wú)法使用ICP/ISP工具的情境下,就只能通過(guò)執(zhí)行程序來(lái)完成。本篇指南將說(shuō)明如何在程序中正確的設(shè)置

2020-08-16 11:59:03

你好,先生或女士我是中國(guó)學(xué)生。我已經(jīng)研究FPGA一段時(shí)間了,我正在嘗試使用FPGA來(lái)實(shí)現(xiàn)FC協(xié)議。經(jīng)過(guò)一番研究,我發(fā)現(xiàn)GTH可以達(dá)到FC1。但是我發(fā)現(xiàn)使用7系列FPGA收發(fā)器向?qū)?b class="flag-6" style="color: red">IP存在一些問(wèn)題。我

2020-08-17 10:28:07

主要是兩個(gè)小程序,1. 依據(jù)所需顯示簇的數(shù)量,自動(dòng)進(jìn)行調(diào)整并顯示,實(shí)現(xiàn)比較繁瑣,但是給大家分享參考下。我也沒(méi)有找到更好的實(shí)現(xiàn)方法。2. 圖像采集過(guò)程中,依據(jù)NI的范例,進(jìn)行了精簡(jiǎn)修改,只保留的圖像采集的部分,驗(yàn)證的過(guò)程是直接調(diào)用筆記本自身的攝像頭,實(shí)現(xiàn)功能正常。給大家參考下。

2019-05-13 14:42:46

,因此將教材拆開(kāi)成兩份20多M大小的教材,但是我后面有時(shí)間我再傳另外一本我提到的那本基于FPGA的圖像處理教材(2019-5-23)上傳中文版part2

2018-09-13 08:44:21

基于FPGA的IP核8051上實(shí)現(xiàn)TCPIP的設(shè)計(jì)

2012-08-06 12:18:28

變換,擴(kuò)展的點(diǎn)以0填充,模擬FPGA的FFT IP核實(shí)際工作狀況),對(duì)測(cè)試圖像test進(jìn)行FFT變換,進(jìn)行必要的濾波,然后IFFT逆變換。測(cè)試圖像為彩色圖像,原始圖像如下。 首先進(jìn)行彩色轉(zhuǎn)灰度的變換

2019-08-08 11:33:01

數(shù)據(jù)流,FPGA通過(guò)對(duì)其同步信號(hào),如時(shí)鐘、行頻和場(chǎng)頻進(jìn)行檢測(cè),從而從數(shù)據(jù)總線上實(shí)時(shí)的采集圖像數(shù)據(jù)。MT9V034攝像頭默認(rèn)初始化數(shù)據(jù)就能輸出正常的視頻流,因此FPGA中實(shí)際上未作任何IIC初始化配置。在FPGA

2019-07-05 13:51:50

亮度分布特性有力的工具,根據(jù)它的結(jié)果可以進(jìn)行諸如灰度拉伸、自動(dòng)對(duì)比度、動(dòng)態(tài)伽馬調(diào)整等操作。圖1 Lena 圖像的灰度直方圖統(tǒng)計(jì)FPGA算法統(tǒng)計(jì)在計(jì)算機(jī)或者DSP 上實(shí)現(xiàn)直方圖統(tǒng)計(jì)時(shí),我們通常會(huì)使用數(shù)組

2012-05-14 12:37:37

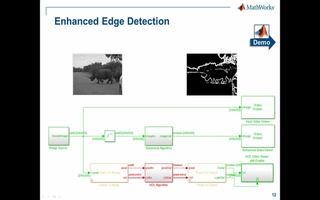

。邊緣增強(qiáng)和噪聲抑制實(shí)際上是兩個(gè)完全相反的圖像處理方式,為了保證兩個(gè)模塊能夠更好的實(shí)現(xiàn)增強(qiáng)圖像的效果,在這個(gè)IP中,第一步做的是圖像的形態(tài)檢測(cè)(Edge Map Morphology),然后再根據(jù)這個(gè)

2019-08-12 18:50:45

的需求很好地調(diào)整壓縮率和吞吐率,可以在低成本的FPGA上實(shí)現(xiàn)超過(guò)16Gbps的吞吐率。LZOAccel-C可以提供與當(dāng)前流行的基于LZO 2.10軟件應(yīng)用相當(dāng)?shù)膲嚎s率,并且可以通過(guò)軟件模型分析處理速度

2018-12-21 23:10:43

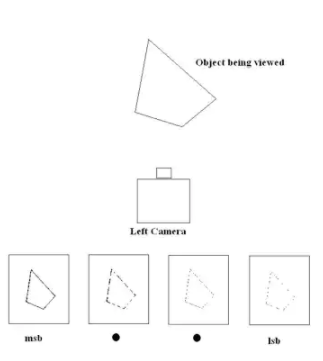

目前,全景技術(shù)的研究主要將注意力集中在集合變換算法和鏡頭矯正算法的改進(jìn),對(duì)實(shí)時(shí)性問(wèn)題研究較少。本系統(tǒng)利用FPGA對(duì)圓形極坐標(biāo)圖像進(jìn)行實(shí)時(shí)展開(kāi)。

2019-08-29 08:20:27

嗨,我是Xilinx FPGA的新手。我該如何在FPGA中實(shí)現(xiàn)實(shí)時(shí)時(shí)鐘或時(shí)間和日期計(jì)數(shù)器?Xilinx是否為Artix 7提供任何RTC核心或IP?非常感謝您的建議。

2020-05-22 12:41:35

大家好我正在嘗試在斯巴達(dá)6上開(kāi)發(fā)UDP / IP堆棧。該FPGA將與外部PHY(DP83640)通信。我已經(jīng)添加了TEMAC v4.4核心。所以我的問(wèn)題是: - 如何在FPGA和PHY之間執(zhí)行自動(dòng)

2019-11-05 09:46:20

使用的是Virtex:5 Minimoudle,我有一個(gè)自定義IP連接到powerpc作為主設(shè)備。我在我的PC上生成數(shù)據(jù)并通過(guò)原始以太網(wǎng)傳輸,最后寫在Minimodule SDRAM上,此通信由此

2020-07-20 07:07:12

我正在嘗試在ML403 FPGA開(kāi)發(fā)板上實(shí)現(xiàn)圖像處理。我知道如何進(jìn)行圖像處理但是,我很困惑如何將我想要處理的圖像處理到我板上的DDR中。是否有可用于將圖像輸入電路板的示例代碼或解決方案。由于尺寸有限,我對(duì)在BRAM中存儲(chǔ)圖像不感興趣。Aravind E Vijayan

2019-11-07 09:20:27

在FPGA中,動(dòng)態(tài)相位調(diào)整(DPA)主要是實(shí)現(xiàn)LVDS接口接收時(shí)對(duì)時(shí)鐘和數(shù)據(jù)通道的相位補(bǔ)償,以達(dá)到正確接收的目的。那么該如何在低端FPGA中實(shí)現(xiàn)DPA的功能呢?

2021-04-08 06:47:08

請(qǐng)將圖片視為附件。針腳及其文字的大小太大了,我無(wú)法找到任何地方調(diào)整尺寸......我嘗試過(guò)選項(xiàng)→偏好→針腳/ T恤→尺寸,但似乎沒(méi)用......請(qǐng)告訴我怎么樣去做?謝謝~~ 以上來(lái)自于谷歌翻譯

2018-10-19 11:29:24

作為我項(xiàng)目的一部分,我需要將ADC與7系列FPGA接口,我有一個(gè)SelectIO?接口向?qū)У?b class="flag-6" style="color: red">IP核。但是,我的整個(gè)項(xiàng)目都在VHDL中,IPi得到的是Verilog。請(qǐng)指出我如何在我的VHDL頂級(jí)模塊中使用該IP核的一些示例。最好的祝福

2020-05-21 12:31:59

總線的FPGA接口? FPGA必須插在服務(wù)器主板上嗎?它可以與普通的服務(wù)器主板連接嗎?我的問(wèn)題是我只能在電路板底部表面的過(guò)孔處點(diǎn)擊QPI信號(hào),并需要某種連接器來(lái)連接FPGA。謝謝!

2020-03-13 10:05:34

如何調(diào)整Arduino STM32的串口緩存大小?

2021-12-08 07:34:18

怎么調(diào)整鋪銅大小,為什么我調(diào)整鋪銅大小會(huì)是這樣

2019-09-05 01:07:58

基于專用單片機(jī)來(lái)實(shí)現(xiàn)(一般稱為可編程DSP單片機(jī))以及在VLSI上實(shí)現(xiàn)某種算法的專用集成電路芯片(ASIC)等。近年來(lái),隨著EDA技術(shù)的迅速發(fā)展,國(guó)內(nèi)外逐漸比較流行的是在FPGA中實(shí)現(xiàn)復(fù)雜算法的運(yùn)算處理。在

2019-07-31 06:38:07

時(shí),我不會(huì)知道如何啟動(dòng)FPGA。我想將RGB圖像轉(zhuǎn)換為灰度圖像,我應(yīng)該如何在PC上顯示圖像的結(jié)果?謝謝!以上來(lái)自于谷歌翻譯以下為原文Hi:I am a beginner for the FPGA

2019-01-25 10:55:14

嗨,團(tuán)隊(duì)我想從PC調(diào)整圖像大小,我希望使用VEE分辨率高于800X600。我能怎么做? BR;希博伊 以上來(lái)自于谷歌翻譯 以下為原文Hi, Team I would like to resize

2019-01-14 14:08:49

本文在分析OpenCores網(wǎng)站提供的一款OC8051IP核的基礎(chǔ)上,給出了一種仿真調(diào)試方案;利用該方案指出了其中若干邏輯錯(cuò)誤并對(duì)其進(jìn)行修改,最終完成了修改后IP核的FPGA下載測(cè)試。

2021-05-08 06:22:32

有沒(méi)有一種簡(jiǎn)單的方法來(lái)強(qiáng)制圖像的大小是4的倍數(shù)?我的CRC算法在計(jì)算中使用32位字。我的解決方法是使用鏈接器選項(xiàng)來(lái)填充未使用的內(nèi)存,但這會(huì)導(dǎo)致不必要的大圖像。我只需要少量的填充,使圖像的大小為4字節(jié)

2018-10-22 14:54:55

怎么才能在嵌入FPGA的IP核8051上實(shí)現(xiàn)TCP/IP的設(shè)計(jì)?

2021-04-29 06:51:27

方法卻都是類似的,都是通過(guò)模板卷積的方法來(lái)實(shí)現(xiàn)的。 VLSI技術(shù)的迅猛發(fā)展為數(shù)字圖像實(shí)時(shí)處理技術(shù)提供了硬件基礎(chǔ),其中FPGA(現(xiàn)場(chǎng)可編程門陣列)的特點(diǎn)使其非常適用于數(shù)字圖像處理。本文研究的就是在

2011-02-24 14:20:18

我想知道像 IAR 這樣構(gòu)建后的最終二進(jìn)制文件大小。目前os CubeIDE最終輸出的是elf文件,所以我不知道它的大小。(當(dāng)我使用 IAR 時(shí),它會(huì)在終端上顯示最終的二進(jìn)制文件大小,并且還可以生成二進(jìn)制文件。)有沒(méi)有人知道如何在 CubeIDE 上檢查最終二進(jìn)制大小?

2022-12-16 07:50:32

樹(shù)莓派如何調(diào)整SD卡的分區(qū)大小

2023-10-24 06:23:28

基本就只能用FPGA。例如在一些分選設(shè)備中圖像處理基本上用的都是FPGA,因?yàn)樵谄渲邢鄼C(jī)從看到物料圖像到給出執(zhí)行指令之間的延時(shí)大概只有幾毫秒,這就要求圖像處理必須很快且延時(shí)固定,只有FPGA進(jìn)行的實(shí)時(shí)

2023-06-08 15:55:34

RDK_V3.8版本,接入分辨率700w,的3392*2008的數(shù)據(jù),運(yùn)行沒(méi)有問(wèn)題,。修改分辨率為800w的3320*2350數(shù)據(jù),出現(xiàn)resizer overflow的問(wèn)題,相關(guān)日志信息如下

2018-07-25 09:07:28

的camera輸出YUV格式時(shí)我發(fā)現(xiàn)我無(wú)法調(diào)整分辨率了,我只能在1024*768分辨率下預(yù)覽并拍照。我覺(jué)得這是ISP的resizer沒(méi)有處理的緣故。請(qǐng)問(wèn)ISP在接受RAW數(shù)據(jù)時(shí)是不是默認(rèn)就開(kāi)啟resizer功能的?而當(dāng)接受YUV數(shù)據(jù)時(shí)需要額外的設(shè)置?

2018-06-21 05:22:51

vision assistant中可以生成直方圖統(tǒng)計(jì),但是這個(gè)直方圖的區(qū)域是固定的;代碼中有圖像區(qū)域的數(shù)組,但是這個(gè)數(shù)組不直觀,如何在運(yùn)行過(guò)程中框選圖像一部分來(lái)得到圖像處理的區(qū)域?

2019-06-23 14:35:46

是否可以使用FMC指令來(lái)調(diào)整程序中的數(shù)據(jù)Flash大小?

2020-12-18 07:43:29

本篇論文就針對(duì)共軛變換圖像處理方法在微光圖像處理領(lǐng)域的應(yīng)用,就如何在FPGA上實(shí)現(xiàn)共軛變換圖像處理方法展開(kāi)研究。首先在Matlab環(huán)境下,對(duì)常用的圖像增強(qiáng)算法和共軛變換圖像處理

2011-11-24 11:35:56 55

55 基于FPGA的SD卡控制器IP,以驗(yàn)證可用。

2015-11-06 09:50:50 10

10 FPGA中IP核的生成,簡(jiǎn)單介紹Quartus II生成IP核的基本操作,簡(jiǎn)單實(shí)用挺不錯(cuò)的資料

2015-11-30 17:36:15 11

11 在樹(shù)莓派上調(diào)整SD卡大小,官方提供的SD卡鏡像只有2G,但是我們通常使用的SD卡都很大,這樣就會(huì)有很多空間沒(méi)法利用,比如我的32G卡有28G都空著呢。所以,我們需要調(diào)整一下可以使用的SD卡的空間的大小

2015-11-30 11:02:55 8

8 基于FPGA的經(jīng)濟(jì)型MPEG2運(yùn)動(dòng)圖像編碼器IP核設(shè)計(jì)

2016-08-30 15:10:14 9

9 FPGA圖像處理

2016-12-14 22:29:34 17

17 如何在EDK中使用自己的 IP核呢? 這是很多人夢(mèng)寐以求的事情。然而在EDK以及ISE的各種文檔中對(duì)此卻遮遮掩掩,欲語(yǔ)還休。

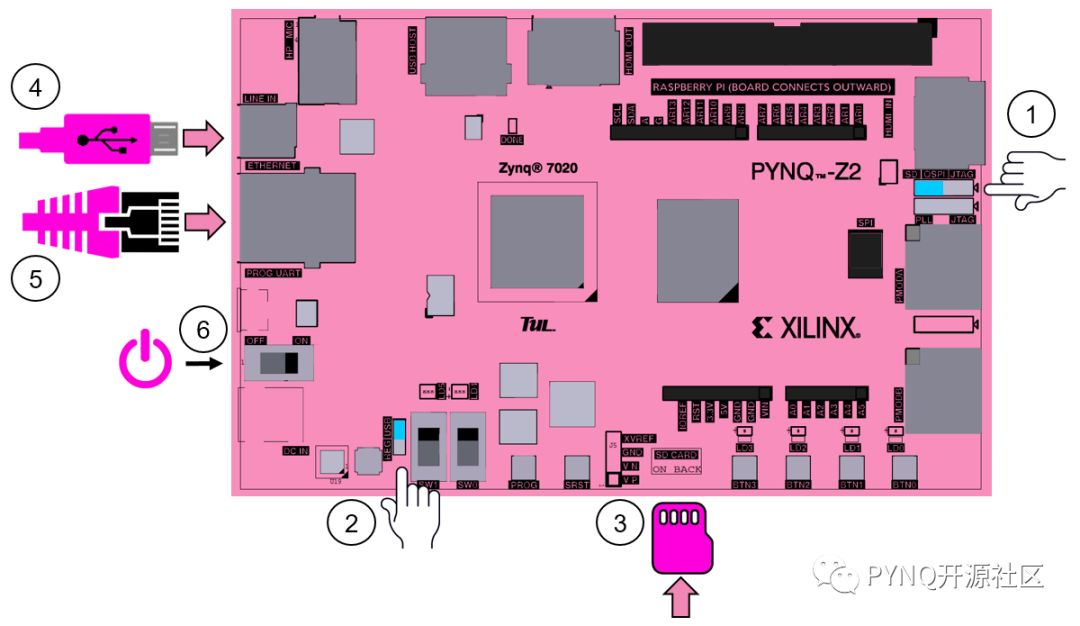

2017-02-11 13:35:11 1995

1995 借助FPGA技術(shù)和NI視覺(jué)開(kāi)發(fā)模塊,您可以對(duì)從相機(jī)采集的圖像進(jìn)行高速現(xiàn)場(chǎng)可編程門陣列(FPGA)處理。 FPGA處理尤其適用于要求圖像采集和處理之間具有低延遲的應(yīng)用。 本文概述了如何在FPGA上進(jìn)行圖像處理。

2017-11-17 06:00:17 18274

18274 的使用,同時(shí)以整數(shù)數(shù)據(jù)處理方式實(shí)現(xiàn)了向?qū)V波器中方差和變換系數(shù)的計(jì)算,并且通過(guò)參數(shù)調(diào)整,可以方便地實(shí)現(xiàn)不同大小圖像的不同尺寸窗口的向?qū)V波。在Altera公司Cyclone系列FPGA芯片上進(jìn)行了綜合,實(shí)驗(yàn)結(jié)果表明,向?qū)V波整數(shù)FPGA結(jié)構(gòu)的處理結(jié)果與

2017-11-22 15:43:12 12

12 在FPGA中,動(dòng)態(tài)相位調(diào)整(DPA)主要是實(shí)現(xiàn)LVDS接口接收時(shí)對(duì)時(shí)鐘和數(shù)據(jù)通道的相位補(bǔ)償,以達(dá)到正確接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自帶有DPA電路,但低端的FPGA,如CYCLONE(r)系列中是沒(méi)有的。下面介紹如何在低端FPGA中實(shí)現(xiàn)這個(gè)DPA的功能。

2018-02-16 17:32:33 10345

10345

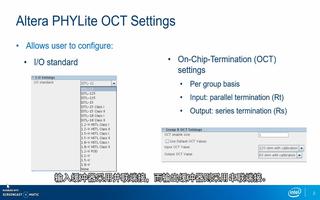

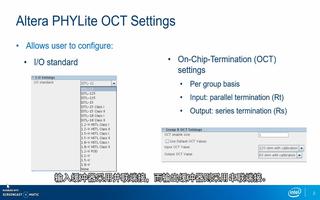

如何在 Altera PHYLite IP 中創(chuàng)建已校準(zhǔn)終端 I/O

2018-06-20 00:28:00 4063

4063

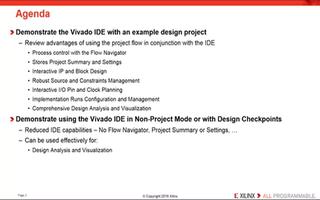

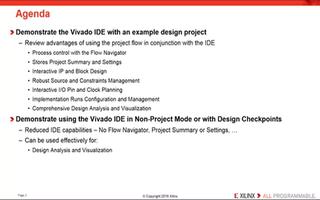

了解如何在IP Integrator中創(chuàng)建簡(jiǎn)單的MicroBlaze設(shè)計(jì),并創(chuàng)建一個(gè)在KC705目標(biāo)板上運(yùn)行的簡(jiǎn)單軟件應(yīng)用程序。

2018-11-20 06:13:00 2836

2836

CapTIvate Technology軟件設(shè)計(jì)快速指南(六) - 實(shí)驗(yàn)二 如何在CDC中調(diào)整觸摸參數(shù)

2019-04-16 06:36:00 2646

2646

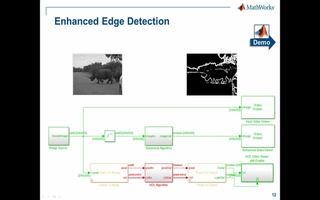

此講座將結(jié)合新產(chǎn)品的特性,重點(diǎn)介紹如何在MATLAB?中開(kāi)發(fā)基于像素流的視頻和圖像處理的算法,并通過(guò)HDL代碼產(chǎn)生的技術(shù)快速在FPGA上實(shí)現(xiàn)。你將了解到:如何在MATLAB中開(kāi)發(fā)基于像素的視頻和圖像處理算法,如何在幀處理的測(cè)試平

2019-08-29 06:08:00 2579

2579

? Xilinx公司的FPGA中有著很多的有用且對(duì)整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號(hào)處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM ?IP

2020-12-29 15:59:39 9496

9496 為了調(diào)整圖像數(shù)據(jù)灰度,介紹了一種圖像灰度級(jí)拉伸算法的FPGA實(shí)現(xiàn)方法,并針對(duì)FPGA的特點(diǎn)對(duì)算法的實(shí)現(xiàn)方法進(jìn)行了研究,從而解決了其在導(dǎo)引系統(tǒng)應(yīng)用中的實(shí)時(shí)性問(wèn)題。仿真驗(yàn)證結(jié)果表明:基于FPGA的圖像拉伸算法具有運(yùn)算速度快,可靠性高,功耗低等特點(diǎn),非常適合成像系統(tǒng)使用.

2021-04-01 14:14:49 10

10 為了調(diào)整圖像數(shù)據(jù)灰度,介紹了一種圖像灰度級(jí)拉伸算法的FPGA實(shí)現(xiàn)方法,并針對(duì)FPGA的特點(diǎn)對(duì)算法的實(shí)現(xiàn)方法進(jìn)行了研究,從而解決了其在導(dǎo)引系統(tǒng)應(yīng)用中的實(shí)時(shí)性問(wèn)題。仿真驗(yàn)證結(jié)果表明:基于FPGA的圖像拉伸算法具有運(yùn)算速度快,可靠性高,功耗低等特點(diǎn),非常適合成像系統(tǒng)使用.

2021-04-01 14:14:49 1

1 基于FPGA的TCP/IP協(xié)議的實(shí)現(xiàn)說(shuō)明。

2021-04-28 11:19:47 49

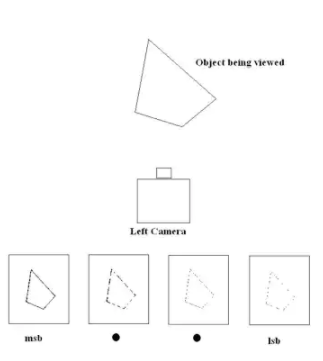

49 使用插值算法實(shí)現(xiàn)圖像縮放是數(shù)字圖像處理算法中經(jīng)常遇到的問(wèn)題。我們經(jīng)常會(huì)將某種尺寸的圖像轉(zhuǎn)換為其他尺寸的圖像,如放大或者縮小圖像。由于在縮放的過(guò)程中會(huì)遇到浮點(diǎn)數(shù),如何在FPGA中正確的處理浮點(diǎn)數(shù)運(yùn)算是在FPGA中實(shí)現(xiàn)圖像縮放的關(guān)鍵。

2022-03-18 11:03:41 4056

4056 如何在java代碼中使用HTTP代理IP。

2022-08-04 15:38:49 1866

1866 如何在python代碼中使用HTTP代理IP。

2022-08-04 15:46:27 1010

1010 如何在PHP代碼中使用HTTP代理IP。

2022-08-04 16:08:51 2056

2056 如何在易e語(yǔ)言代碼中使用HTTP代理IP,示例代碼demo直接可用(步驟注釋清晰)

2022-08-05 16:29:51 5972

5972 如何在c語(yǔ)言代碼中使用HTTP代理IP,示例代碼demo直接可用(步驟注釋清晰)

2022-08-05 16:31:38 1980

1980 硬件調(diào)整大小和去隔行簡(jiǎn)化了視頻數(shù)據(jù)的格式化和索引,以允許更多的編碼資源用于圖像數(shù)據(jù)處理和覆蓋到顯示數(shù)據(jù)上。這種疊加的示例包括調(diào)整大小的圖像,這些圖像可以查看數(shù)據(jù)幀的特定部分以減少處理時(shí)間。

2022-08-25 14:49:26 1118

1118

移動(dòng)c臂x光機(jī)常用于骨科手術(shù)當(dāng)中,該設(shè)備對(duì)于操作人員的技術(shù)要求較高,即便是專業(yè)醫(yī)師也需要經(jīng)過(guò)培訓(xùn)后才能熟練操作,它的操作步驟是什么樣的,又該如何調(diào)整它的窗口大小呢?

2022-09-20 14:34:46 671

671

電子發(fā)燒友網(wǎng)站提供《如何在模擬電視上打印圖像.zip》資料免費(fèi)下載

2022-11-17 11:11:00 0

0 核的不同模塊進(jìn)行實(shí)體/塊的仿真。前文回顧如何測(cè)試與驗(yàn)證復(fù)雜的FPGA設(shè)計(jì)(1)——面向?qū)嶓w或塊的仿真在本篇文章中,我們將介紹如何在虹科IP核中執(zhí)行面向全局的仿真,而這也是測(cè)

2022-06-15 17:31:20 389

389

Xilinx公司的FPGA中有著很多的有用且對(duì)整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號(hào)處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317 電子發(fā)燒友網(wǎng)站提供《磁棒線圈電感的封裝大小能調(diào)整嗎.docx》資料免費(fèi)下載

2023-12-18 10:23:53 0

0 ,磁棒線圈電感的封裝大小能調(diào)整嗎?我們遇到很多客戶咨詢關(guān)于調(diào)整當(dāng)前電感應(yīng)用封裝的案子,可以肯定的告訴大家,磁棒線圈電感的封裝大小是可以調(diào)整的。簡(jiǎn)單來(lái)說(shuō),磁棒線圈電感

2023-12-27 21:57:07 0

0 LED(Light Emitting Diode)是一種半導(dǎo)體器件,經(jīng)常被用作照明、顯示和指示燈。為了驅(qū)動(dòng)LED,需要使用LED驅(qū)動(dòng)電源來(lái)提供穩(wěn)定的電流。調(diào)整LED的電流大小對(duì)于控制LED的亮度

2024-02-27 17:50:17 743

743

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論