本文設(shè)計(jì)了一種以超低功耗單片機(jī)MSP430F149為控制器,以高速的FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)實(shí)現(xiàn)等精度測(cè)量正弦信號(hào)的頻率、周期和相位差的多功能計(jì)數(shù)器。在設(shè)計(jì)中依據(jù)等精度計(jì)數(shù)原理,應(yīng)

2012-07-16 16:02:09 4299

4299

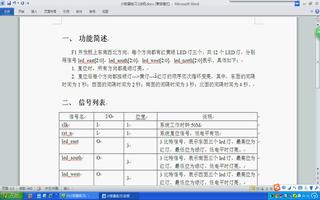

學(xué)習(xí)這門(mén)技術(shù)也越來(lái)越重要,很多人都開(kāi)啟了學(xué)習(xí)機(jī)器學(xué)習(xí),本文就介紹了機(jī)器學(xué)習(xí)的基礎(chǔ)內(nèi)容。提示:以下是本篇文章正文內(nèi)容,編程實(shí)現(xiàn)10進(jìn)制計(jì)數(shù)器,具有異步復(fù)位功能,十位和個(gè)位用8421BCD碼表示一、4選1多路選擇器是什么?示例:pandas 是基于NumPy 的一種工具,該工具是為了解決

2022-02-09 07:33:15

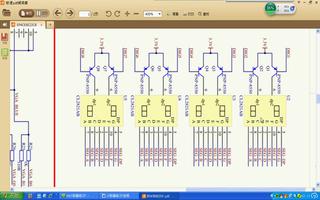

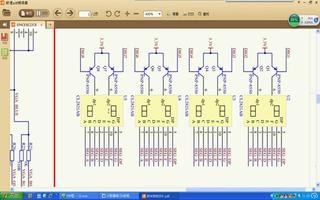

74161設(shè)計(jì)12進(jìn)制計(jì)數(shù)器,1.74161為十六進(jìn)制計(jì)數(shù)器,設(shè)計(jì)十二進(jìn)制計(jì)數(shù)器時(shí)1片就可以滿(mǎn)足要求。2.新建BDF文件及保存工程同前篇。3.將所需要的元器件和引腳拖入?yún)^(qū)域內(nèi)并完成連接,如圖1所示圖1十二進(jìn)制計(jì)數(shù)器連接圖4.建立VWF文件,仿真后得到結(jié)果如圖2

2021-07-22 06:33:31

我是剛開(kāi)始學(xué)FPGA,現(xiàn)在對(duì)其verilog語(yǔ)言還不是很懂。下面題目:設(shè)計(jì)一個(gè)十進(jìn)制的加法計(jì)數(shù)器,功能包含復(fù)位信號(hào),置位信號(hào),每個(gè)時(shí)鐘的正跳變沿計(jì)數(shù)器加一。計(jì)數(shù)0-99即可。請(qǐng)幫忙給個(gè)參考的程序。

2012-05-11 23:03:24

Verilog與VHDL(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s

2015-03-16 12:00:54

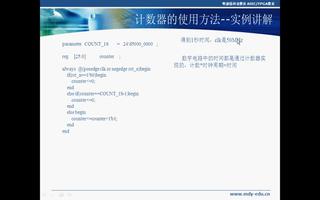

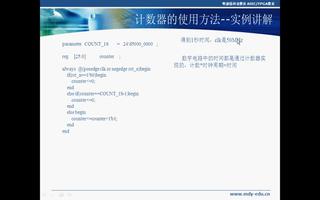

FPGA代碼最常使用的功能模塊是哪個(gè)呢?是狀態(tài)機(jī)、乘法器、加法器、計(jì)數(shù)器?答案就是計(jì)數(shù)器!幾乎我們的每個(gè)設(shè)計(jì)都要用到計(jì)數(shù)器,用來(lái)計(jì)算接受或發(fā)送了多少個(gè)數(shù)據(jù),用來(lái)衡量用了多少時(shí)間,用來(lái)做選擇信號(hào)等等

2015-05-14 22:01:11

使用計(jì)數(shù)器計(jì)數(shù)不成功,有個(gè)老師指導(dǎo)說(shuō)“每次是能計(jì)數(shù)器, 計(jì)數(shù)器值會(huì)清零 "就說(shuō)了這幾句,奈何我太菜了 無(wú)法理解怎么弄。有大神指導(dǎo)下如何實(shí)現(xiàn)計(jì)數(shù)操作

2020-05-31 22:35:28

計(jì)數(shù)器是什么?如何使用計(jì)數(shù)器?計(jì)數(shù)器有哪些應(yīng)用呢?

2022-02-28 11:08:08

AVR單片機(jī)軟硬件設(shè)計(jì)教程入門(mén)篇單片機(jī)就是一臺(tái)微型電腦。麻雀雖小,五臟俱全,單片機(jī)將微型電腦的所有基本部分都集成在一片硅片上。構(gòu)成單片機(jī)的基本要素:CPU核,ROM,RAM,片上外設(shè),總線(xiàn) [hide]AVR單片機(jī)軟硬件設(shè)計(jì)教程.rar[/hide]

2009-12-09 15:22:26

CSR8670開(kāi)發(fā)板--菜鳥(niǎo)入門(mén)篇

2017-09-30 08:45:57

`力天電子手把手教你學(xué)DSP之入門(mén)篇.由力天電子出品全網(wǎng)獨(dú)家資源下載地址:`

2013-05-05 19:09:23

PCB設(shè)計(jì)技巧之入門(mén)篇

2012-08-05 21:44:31

RK3399平臺(tái)開(kāi)發(fā)系列講解(內(nèi)核入門(mén)篇)1.1、通過(guò)sysfs清楚了解設(shè)備的系統(tǒng)狀況 sys目錄

2021-12-16 08:00:00

STM32入門(mén)篇之通用定時(shí)器徹底研究:STM32的定時(shí)器功能很強(qiáng)大,學(xué)習(xí)起來(lái)也很費(fèi)勁兒,本人在這卡了5天才算看明白。寫(xiě)下下面的文字送給后來(lái)者,希望能帶給你點(diǎn)啟發(fā)。在此聲明,本人也是剛入門(mén),接觸

2015-05-14 08:43:52

cpld\fpga\verilog hdl視頻教程入門(mén)篇:第1講、FPGA設(shè)計(jì)基礎(chǔ)(PDF、視頻)第2講、FPGA設(shè)計(jì)入門(mén)(視頻、課后習(xí)題)第3講、VerilogHDL

2009-03-26 16:37:40

教程目錄: 入門(mén)篇:第1講、FPGA設(shè)計(jì)基礎(chǔ)(PDF、視頻)第2講、FPGA設(shè)計(jì)入門(mén)(視頻、課后習(xí)題)第3講、VerilogHDL基礎(chǔ)(PDF、視頻、課后習(xí)題)第4講:Verilog HDL中的組合

2009-03-09 22:56:25

全部verilog源碼)5.基于verilog的分頻器設(shè)計(jì) (可實(shí)現(xiàn)任意整數(shù)分頻) (附全部源碼)6. 《ZedBoard高手之路》入門(mén)篇視頻教程7. 《FPGA設(shè)計(jì)中的黑盒設(shè)計(jì)與使用》視頻教程如果

2016-07-16 15:09:50

已知外部輸入時(shí)鐘信號(hào)clk為50MHz,請(qǐng)用verilog實(shí)現(xiàn)計(jì)數(shù)器的計(jì)時(shí)1秒鐘,每間隔1秒輸出一個(gè)clk時(shí)鐘周期的脈沖信號(hào)flag,參考波形如下:

2023-08-17 09:13:59

如下所示,表明成功。三 下階段安排這樣驅(qū)動(dòng)模塊的基本環(huán)境及驅(qū)動(dòng)開(kāi)發(fā)的基本流程介紹完畢,階段二的介紹,參考附錄部分。自此【OK210試用體驗(yàn)】入門(mén)篇的4篇博文已完成:【OK210試用體驗(yàn)入門(mén)篇(1):開(kāi)箱

2015-08-01 22:39:56

`推薦課程:張飛軟硬開(kāi)源:基于STM32的BLDC直流無(wú)刷電機(jī)驅(qū)動(dòng)器(視頻+硬件)http://url.elecfans.com/u/73ad899cfd簡(jiǎn)介:《機(jī)器人制作入門(mén)篇》從一個(gè)業(yè)余機(jī)器人

2017-06-07 17:04:18

哪位大蝦幫幫忙用verilog語(yǔ)言編寫(xiě)一個(gè)計(jì)數(shù)器,謝謝啊

2009-03-23 17:30:38

STM32學(xué)習(xí)之路入門(mén)篇之指令集

2018-12-26 22:45:43

講解數(shù)字系統(tǒng),尤其是時(shí)鐘系統(tǒng)中非常常見(jiàn)的一個(gè)模塊——BCD碼計(jì)數(shù)器的設(shè)計(jì)實(shí)現(xiàn)與驗(yàn)證,講解Verilog基礎(chǔ)語(yǔ)法,了解BCD碼技術(shù)器與普通二進(jìn)制計(jì)數(shù)器的區(qū)別。BCD碼計(jì)數(shù)器經(jīng)常用在需要十進(jìn)制計(jì)數(shù),十進(jìn)制

2015-09-23 12:39:23

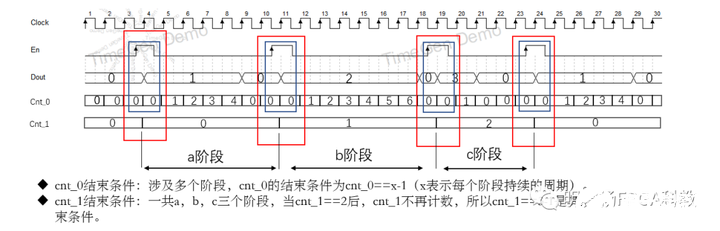

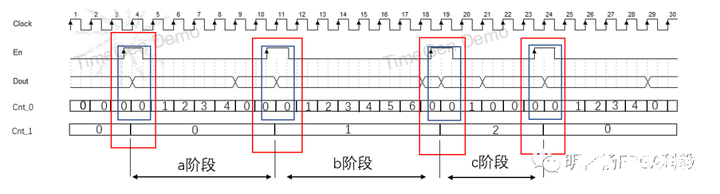

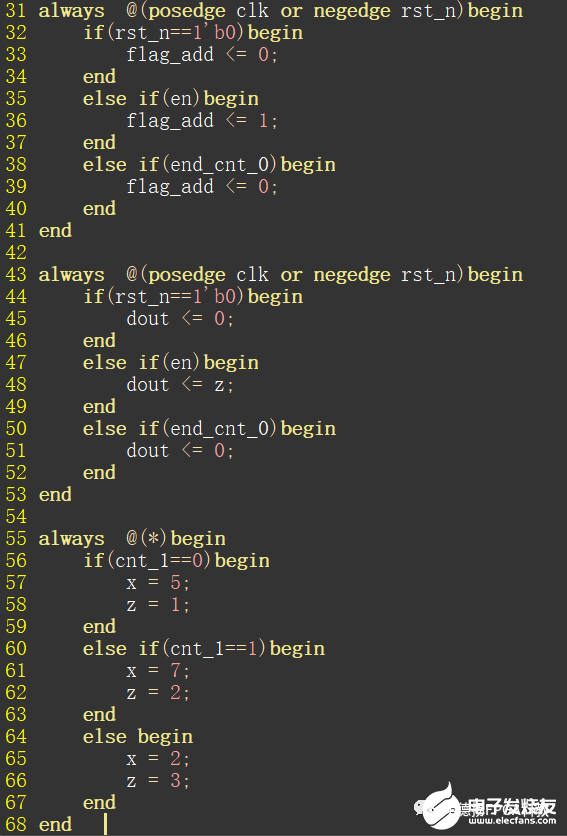

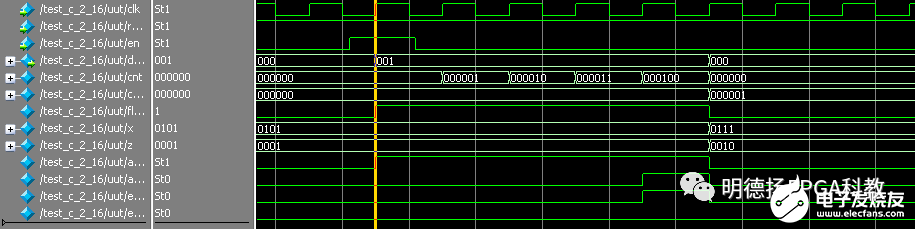

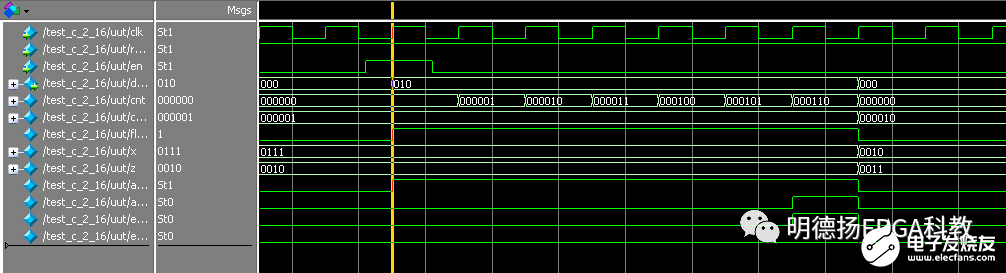

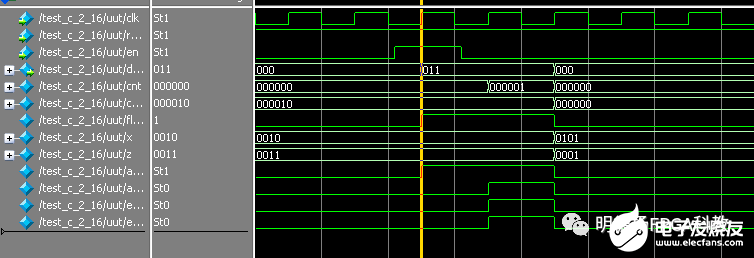

FPGA的人來(lái)說(shuō),非常之實(shí)用。但是,部分工程師在做仿真時(shí),有時(shí)候會(huì)出現(xiàn)違反這一原則的奇怪現(xiàn)象。例如下面這個(gè)案例。關(guān)于在仿真軟件中,為什么計(jì)數(shù)器的判定會(huì)在不滿(mǎn)足加一條件的時(shí)候進(jìn)行加一操作(如下圖所示

2020-04-24 14:54:53

最近在看《現(xiàn)代操作系統(tǒng)》,他提到了時(shí)鐘維持實(shí)際時(shí)間,在每個(gè)時(shí)鐘滴答將計(jì)數(shù)器加1即可實(shí)現(xiàn)。但要注意位溢出(32位計(jì)數(shù)器),可以通過(guò)以下方法解決:使用64位計(jì)數(shù)器:缺點(diǎn)是這種方法使得計(jì)數(shù)器加一操作的代價(jià)很高,1s內(nèi)維護(hù)很多次計(jì)數(shù)器。我不太懂紅色字體的意思

2018-05-04 11:36:41

單片機(jī) (入門(mén)篇)

2012-08-20 16:42:30

單片機(jī)學(xué)習(xí)(入門(mén)篇)

2009-10-10 10:26:50

單片機(jī)(入門(mén)篇)

2013-04-01 15:22:07

8253微機(jī)接口芯片作為定時(shí)器和計(jì)數(shù)器時(shí)實(shí)質(zhì)相同嗎?定時(shí)器/計(jì)數(shù)器8253內(nèi)部有多少個(gè)16位的計(jì)數(shù)器?

2021-10-20 06:16:30

單片機(jī)入門(mén)的敲門(mén)磚。在此,筆者就以此章節(jié)為重點(diǎn),對(duì)定時(shí)器/計(jì)數(shù)器學(xué)習(xí)做出基本介紹。-------------------------------------------------------------------------------------------------**提示:以下是本篇文章正文.

2021-11-24 07:18:06

之前寫(xiě)過(guò)一篇關(guān)于 “加法器” 的博文,研究了加法器的底層電路,本來(lái)想要研究一下“行波時(shí)鐘”,由于涉及到計(jì)數(shù)器,那么就先看看 “計(jì)數(shù)器” 在FPGA中綜合后是什么樣的 ?然后再看“行波時(shí)鐘”的情況

2014-03-24 17:27:51

你好,我是verilog /邏輯設(shè)計(jì)的新手。我不確定問(wèn)題屬于哪里,如果不是,請(qǐng)告訴我,謝謝我想用D觸發(fā)器構(gòu)建一個(gè)3位計(jì)數(shù)器我在閱讀了“邏輯設(shè)計(jì)的基本原理(Charles H. Roth)”一書(shū)后寫(xiě)了

2019-02-14 06:13:32

怎么實(shí)現(xiàn)基于單片機(jī)和FPGA的多功能計(jì)數(shù)器的設(shè)計(jì)?

2021-05-14 06:57:15

按鍵與數(shù)碼管的程序設(shè)計(jì)_手把手教你學(xué)單片機(jī)之AVR入門(mén)篇第06講 中斷與定時(shí)器_手把手教你學(xué)單片機(jī)之AVR入門(mén)篇第07講 異步串行口UART_手把手教你學(xué)單片機(jī)之AVR入門(mén)篇第08講 SPI串行口

2011-03-02 11:04:07

最近在做以前的每日一練,其中有一題是計(jì)算輸入一段字符所需時(shí)間,程序框圖如附件。這里1號(hào)計(jì)數(shù)器一直計(jì)數(shù)我可以理解,但是2號(hào)計(jì)數(shù)器不是順序框到第三個(gè)框的時(shí)候才開(kāi)始計(jì)數(shù)嗎?不是從0開(kāi)始計(jì)數(shù)嗎,這樣為什么2號(hào)減去1號(hào)能夠得出中間所需時(shí)間呢?新手剛入門(mén),希望各位指教。

2017-12-08 11:32:32

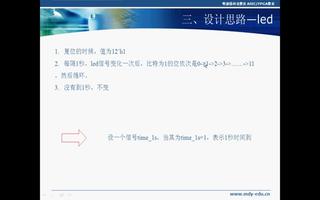

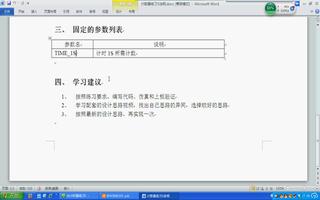

章Signaltapll的使用技巧1.signaltapll使用第十二章學(xué)習(xí)自檢方法1.波形對(duì)比方法第十三章計(jì)數(shù)器的使用1.計(jì)數(shù)器使用原則2.計(jì)數(shù)器練習(xí)13.計(jì)數(shù)器練習(xí)1答案4.計(jì)數(shù)器練習(xí)25.計(jì)數(shù)器練習(xí)

2015-05-20 14:47:32

機(jī)器學(xué)習(xí)項(xiàng)目入門(mén)篇:一個(gè)完整的機(jī)器學(xué)習(xí)項(xiàng)目

2020-05-11 14:47:49

小弟剛學(xué)FPGA用的是EP4CE6現(xiàn)在想寫(xiě)一個(gè)60進(jìn)制的計(jì)數(shù)器 然后在數(shù)碼管上顯示出來(lái)用verilog寫(xiě)但想了好幾天沒(méi)想出來(lái)去大俠指導(dǎo)下或給個(gè)程序看看小弟感激不盡。。。。。拜托了

2014-09-16 18:29:27

`“電子工程師自學(xué)速成”叢書(shū)分為“入門(mén)篇”、“提高篇”和“設(shè)計(jì)篇”共 3 本。《電子工程師自學(xué)速成入門(mén)篇》為“入門(mén)篇”,主要介紹了電子技術(shù)入門(mén)基礎(chǔ)、電子元器件電阻器、電容器、電感器、變壓器、二極管

2017-11-09 12:50:35

電子工程師自學(xué)速成 入門(mén)篇

2020-05-08 08:29:51

單片機(jī)入門(mén)、單片機(jī)硬件原理、單片機(jī)的開(kāi)發(fā)過(guò)程、單片機(jī)編程、中斷技術(shù)、定時(shí)器/計(jì)數(shù)器、串行通信技術(shù)和接口技術(shù),Protel電路繪圖設(shè)計(jì)部分的內(nèi)容有Protel軟件入門(mén)、設(shè)計(jì)電路原理圖、制作新元件、手工

2017-11-09 12:53:48

電子工程師自學(xué)速成”叢書(shū)分為“入門(mén)篇”、“提高篇”和“設(shè)計(jì)篇”共 3 本。《電子工程師自學(xué)速成——入門(mén)篇》為“入門(mén)篇”,主要介紹了電子技術(shù)入門(mén)基礎(chǔ)、電子元器件(電阻器、電容器、電感器、變壓器、二極管

2018-10-27 15:37:36

單片機(jī)(入門(mén)篇)

2006-03-21 20:51:01 330

330 格雷碼計(jì)數(shù)器的Verilog描述

2009-08-03 09:39:58 45

45 以89S52單片機(jī)和EP1C6Q240C8型FPGA為控制核心的多功能計(jì)數(shù)器,是由峰值檢波、A/D轉(zhuǎn)換、程控放大、比較整形、移相網(wǎng)絡(luò)部分組成,可實(shí)現(xiàn)測(cè)量正弦信號(hào)的頻率、周期和相位差的功能。多

2010-12-27 15:21:44 78

78 計(jì)數(shù)器的級(jí)連使用

一個(gè)十進(jìn)制計(jì)數(shù)器只能顯示0~9十個(gè)數(shù),為了擴(kuò)大計(jì)數(shù)器范圍,常用多個(gè)十進(jìn)制計(jì)數(shù)器級(jí)連使用。

2007-11-22 12:53:25 3379

3379

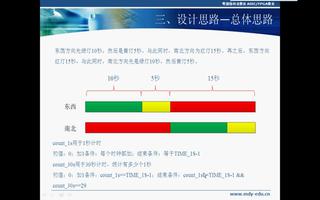

60進(jìn)制計(jì)數(shù)器,由于24進(jìn)制、60進(jìn)制計(jì)數(shù)器均由集成計(jì)數(shù)器級(jí)聯(lián)構(gòu)成,且都包含有基本的

2008-06-30 00:00:41 15785

15785

計(jì)數(shù)器的應(yīng)用

2008-12-17 14:23:53 658

658

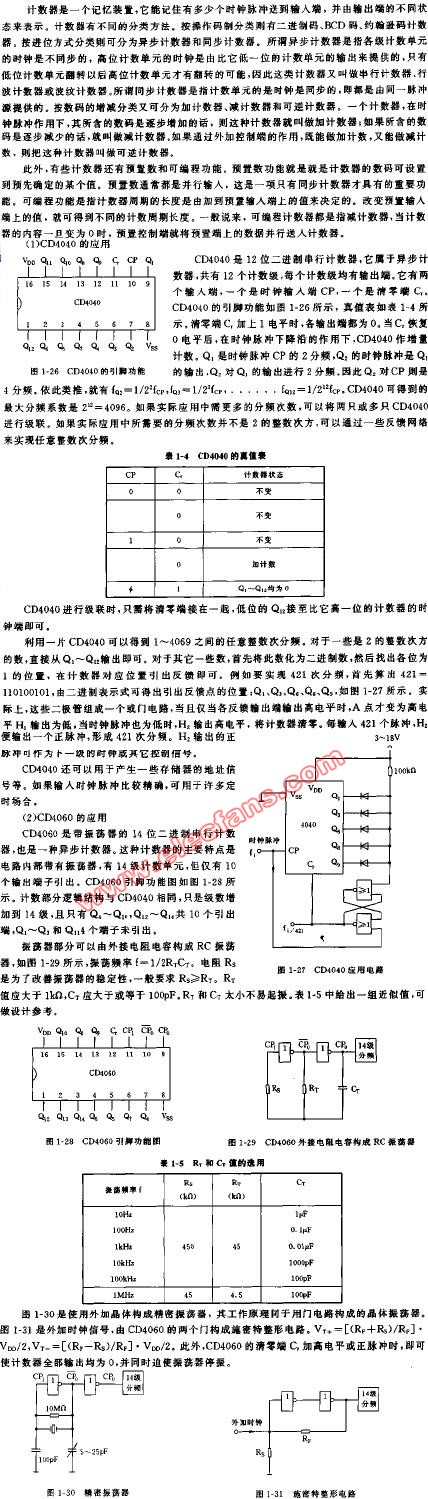

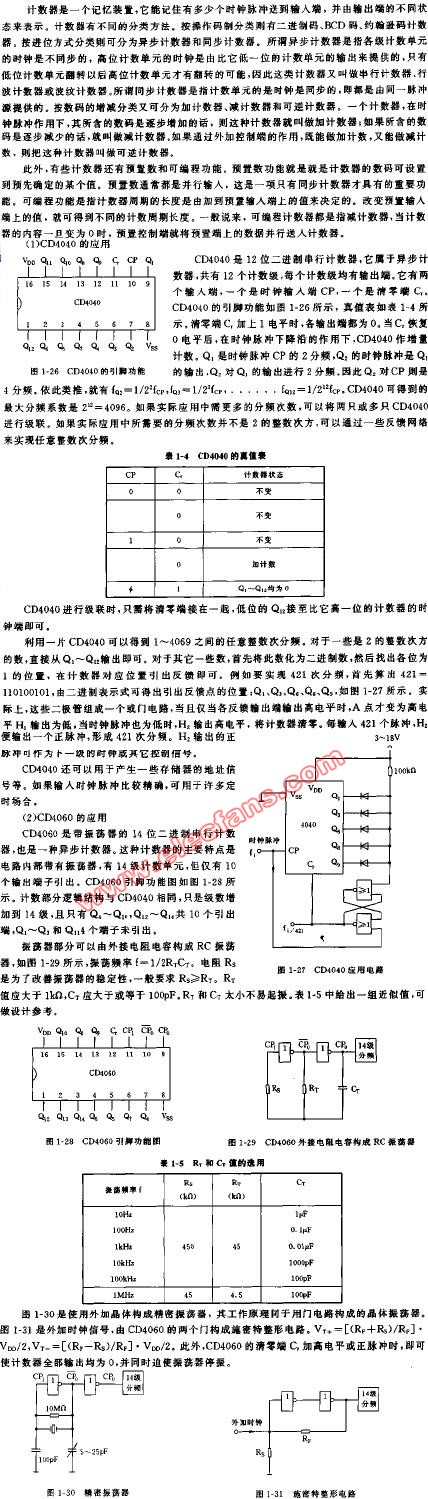

計(jì)數(shù)器

計(jì)數(shù)器的作用與分類(lèi)

計(jì)數(shù)器(Counter)用于計(jì)算輸入脈沖個(gè)數(shù),還常用于分頻、定時(shí)等。

2009-09-30 18:30:15 1414

1414

單片機(jī)入門(mén)教程第16課-計(jì)數(shù)器與定時(shí)器(二)

說(shuō)明:本課部份圖請(qǐng)打本單片機(jī)書(shū),都有,抱歉,不及畫(huà)。 定時(shí)/計(jì)數(shù)器的方式控制字

2010-01-07 15:54:54 1066

1066

單片機(jī)入門(mén)教程第16課-計(jì)數(shù)器與定時(shí)器(一)

一、計(jì)數(shù)概念的引入 從選票的統(tǒng)計(jì)談起:畫(huà)“正”。這就是計(jì)數(shù),生活中計(jì)數(shù)的例子處

2010-01-07 15:58:20 935

935

環(huán)形計(jì)數(shù)器和扭環(huán)形計(jì)數(shù)器

移位寄存器也可以構(gòu)成計(jì)數(shù)器,稱(chēng)為移位型計(jì)數(shù)器。它有兩種結(jié)構(gòu):環(huán)形計(jì)數(shù)器和扭環(huán)形計(jì)數(shù)器。

2010-01-12 14:07:46 9173

9173 計(jì)數(shù)器,計(jì)數(shù)器的工作原理是什么?

在數(shù)字系統(tǒng)中使用最多的時(shí)序電路是計(jì)數(shù)器。計(jì)數(shù)器不僅能用于對(duì)時(shí)鐘脈沖進(jìn)行計(jì)數(shù)還可以用于分頻、定時(shí),產(chǎn)生

2010-03-08 13:50:14 59934

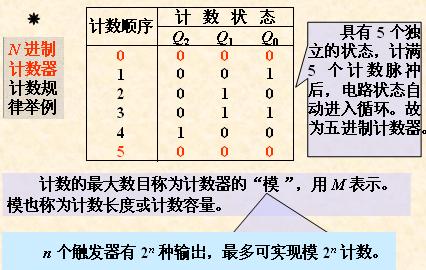

59934 計(jì)數(shù)器的定義和分類(lèi)

計(jì)數(shù)器定義在數(shù)字電路中,計(jì)數(shù)器屬于時(shí)序電路,它主要由具有記憶功能的觸發(fā)器構(gòu)成。計(jì)數(shù)器不僅僅

2010-03-08 17:37:35 12567

12567 簡(jiǎn)單改變FPGA計(jì)數(shù)器規(guī)格使作為DAC功能PWM計(jì)數(shù)器的紋波降低。

2012-04-06 11:11:57 1856

1856

計(jì)數(shù)器原理圖介紹。計(jì)數(shù)器原理圖介紹。計(jì)數(shù)器原理圖介紹

2015-12-25 09:37:05 14

14 電子工程師自學(xué)速成 - 入門(mén)篇電子工程師自學(xué)速成 - 入門(mén)篇電子工程師自學(xué)速成 - 入門(mén)篇電子工程師自學(xué)速成 - 入門(mén)篇電子工程師自學(xué)速成 - 入門(mén)篇。

2016-05-10 15:48:42 0

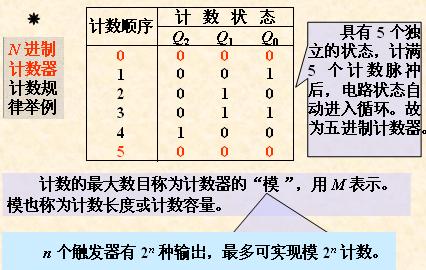

0 集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

2016-06-08 14:28:43 0

0 攝像機(jī)基礎(chǔ)培訓(xùn)——入門(mén)篇

2017-01-04 22:03:22 0

0 新手單片機(jī)入門(mén)篇

2017-10-13 09:23:35 13

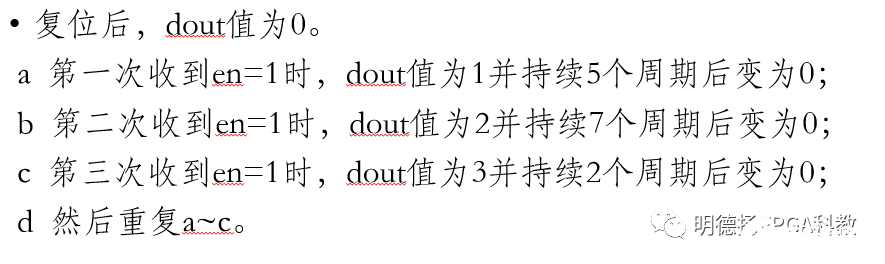

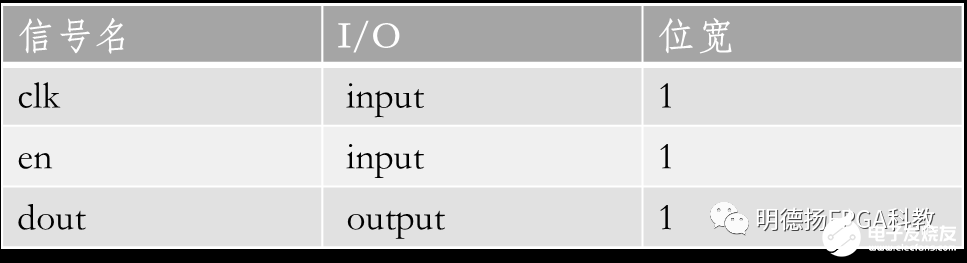

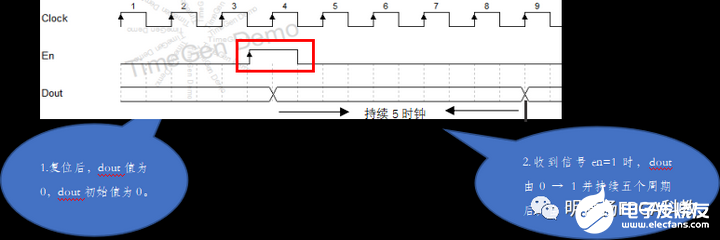

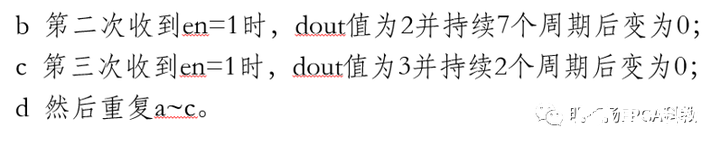

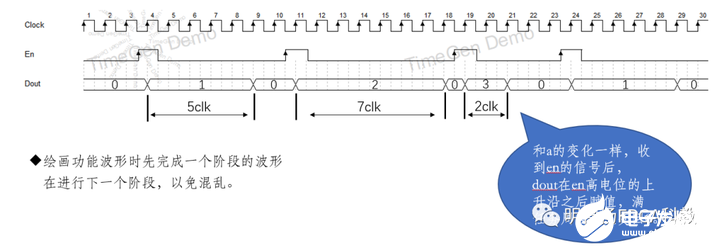

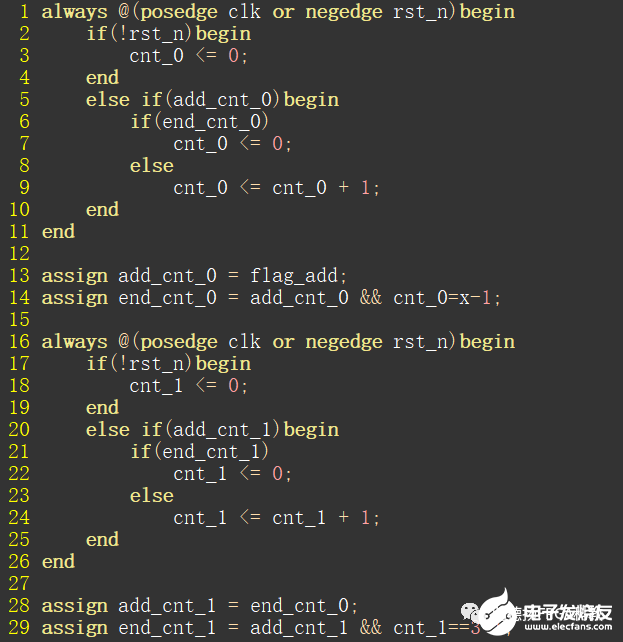

13 問(wèn)題1:如何用Verilog實(shí)現(xiàn)這個(gè)計(jì)數(shù)器?針對(duì)上述功能的計(jì)數(shù)器,應(yīng)該如何用Verilog實(shí)現(xiàn)?

2018-05-16 15:16:13 6102

6102

Verilog HDL作為現(xiàn)在最流行的FPGA開(kāi)發(fā)語(yǔ)言,當(dāng)然是入門(mén)基礎(chǔ)。

2019-02-18 14:47:00 10320

10320 計(jì)數(shù)器

2019-09-03 06:07:00 1711

1711

計(jì)數(shù)器

2019-09-03 06:15:00 1482

1482

計(jì)數(shù)器

2019-09-03 06:14:00 1422

1422

計(jì)數(shù)器

2019-09-03 06:11:00 3556

3556

計(jì)數(shù)器

2019-09-03 06:10:00 2856

2856

計(jì)數(shù)器

2019-08-29 06:10:00 2699

2699 計(jì)數(shù)器

2019-09-03 06:09:00 2484

2484

計(jì)數(shù)器

2019-09-03 06:08:00 1809

1809

計(jì)數(shù)器

2019-09-03 06:06:00 2556

2556

計(jì)數(shù)器

2019-09-03 06:05:00 2473

2473

計(jì)數(shù)器

2019-09-03 06:04:00 5364

5364

計(jì)數(shù)器

2019-09-03 06:03:00 2329

2329

計(jì)數(shù)器

2019-09-03 06:02:00 1921

1921

計(jì)數(shù)器

2019-09-03 06:01:00 2800

2800

計(jì)數(shù)器

2019-09-02 06:10:00 5240

5240

計(jì)數(shù)器的工作是通過(guò)每個(gè)時(shí)鐘脈沖將計(jì)數(shù)器的內(nèi)容提前一個(gè)計(jì)數(shù)來(lái)計(jì)數(shù)。當(dāng)被時(shí)鐘輸入激活時(shí)推進(jìn)其數(shù)字或狀態(tài)序列的計(jì)數(shù)器被稱(chēng)為以“遞增計(jì)數(shù)”模式操作。同樣,當(dāng)被時(shí)鐘輸入激活時(shí)減少其數(shù)字或狀態(tài)序列的計(jì)數(shù)器被稱(chēng)為以“倒計(jì)數(shù)”模式操作。在UP和DOWN模式下工作的計(jì)數(shù)器稱(chēng)為雙向計(jì)數(shù)器。

2019-06-23 07:47:00 12722

12722

本文檔的主要內(nèi)容詳細(xì)介紹的是在寫(xiě)Verilog時(shí)用到的簡(jiǎn)單的計(jì)數(shù)器模塊和功能模塊的程序免費(fèi)下載。

2019-08-30 08:00:00 11

11 該計(jì)數(shù)器從0 計(jì)數(shù)到4294967295,然后回滾到0 并重新開(kāi)始計(jì)數(shù)。它只需要FPGA 上一點(diǎn)點(diǎn)的資源就可以迅速完成計(jì)數(shù),這都多虧了FPGA 中隱藏的進(jìn)位鏈。讓我們來(lái)看這種計(jì)數(shù)器的幾種變體。

2020-12-11 17:26:55 12

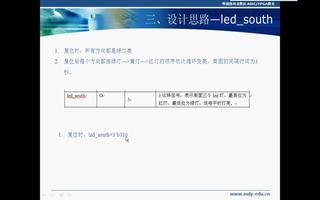

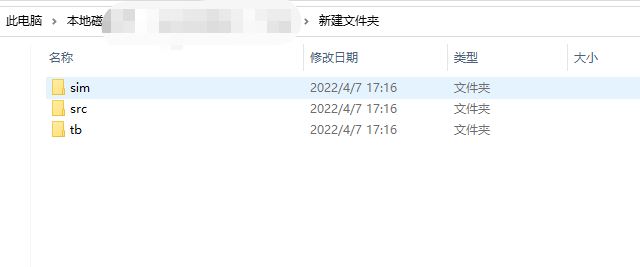

12 用Verilog語(yǔ)言,活用計(jì)數(shù)器功能。

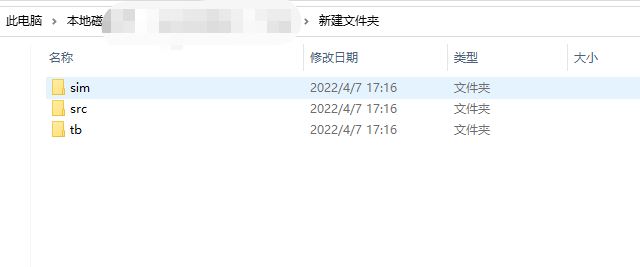

2022-04-07 17:33:24 4520

4520

扭環(huán)形計(jì)數(shù)器,約翰遜計(jì)數(shù)器,每次狀態(tài)變化時(shí)僅有一個(gè)觸發(fā)器發(fā)生翻轉(zhuǎn),譯碼不存在競(jìng)爭(zhēng)冒險(xiǎn),在n(n≥3)位計(jì)數(shù)器中,使用2n個(gè)狀態(tài),有2^n-2n個(gè)狀態(tài)未使用;

2022-06-15 09:27:57 1971

1971 MELSEC iQ-R高速計(jì)數(shù)器模塊用戶(hù)手冊(cè)(入門(mén)篇) 產(chǎn)品規(guī)格書(shū).本手冊(cè)中是用于讓用戶(hù)了解使用下述對(duì)象模塊時(shí)的必要性能規(guī)格、投運(yùn)步驟、配線(xiàn)、運(yùn)行示例等相關(guān)內(nèi)容。

2022-08-25 09:18:48 1

1 電子發(fā)燒友網(wǎng)站提供《FPGA上的十六進(jìn)制計(jì)數(shù)器.zip》資料免費(fèi)下載

2022-11-23 10:47:06 7

7 電子發(fā)燒友網(wǎng)站提供《Xilinx Spartan 6 FPGA上的0到999計(jì)數(shù)器.zip》資料免費(fèi)下載

2022-11-23 10:27:06 2

2 本方案是一個(gè)基于 FPGA ?的十進(jìn)制計(jì)數(shù)器。共陽(yáng)極 7 段顯示器上的 0 到 9 十進(jìn)制計(jì)數(shù)器,硬件在 Xilinx Spartan 6 FPGA 板上實(shí)現(xiàn)。

2022-12-20 14:52:25 2

2 S7-1200的計(jì)數(shù)器為IEC計(jì)數(shù)器,用戶(hù)程序中可以使用的計(jì)數(shù)器數(shù)量?jī)H受CPU的存儲(chǔ)器容量限制。

2023-01-29 09:31:56 6125

6125 在數(shù)字電子產(chǎn)品中,計(jì)數(shù)器是由一系列觸發(fā)器組成的時(shí)序邏輯電路。顧名思義,計(jì)數(shù)器用于計(jì)算輸入在負(fù)或正邊沿轉(zhuǎn)換中出現(xiàn)的次數(shù)。根據(jù)觸發(fā)觸發(fā)器的方式,計(jì)數(shù)器可以分為兩類(lèi):同步計(jì)數(shù)器和異步計(jì)數(shù)器。了解這兩種計(jì)數(shù)器的工作原理以及它們之間的區(qū)別。

2023-03-25 17:31:07 18649

18649

電子發(fā)燒友網(wǎng)站提供《在Verilog HDL中使用分頻器的8位計(jì)數(shù)器的設(shè)計(jì).zip》資料免費(fèi)下載

2023-06-15 10:14:44 0

0 同步計(jì)數(shù)器和異步計(jì)數(shù)器是兩種常見(jiàn)的數(shù)據(jù)結(jié)構(gòu),它們都用于控制對(duì)共享資源的訪(fǎng)問(wèn)。它們的主要作用是實(shí)現(xiàn)多個(gè)線(xiàn)程之間的同步和并發(fā)控制。盡管它們都被用于同步的目的,但它們有很多不同的特點(diǎn)和用例。 同步計(jì)數(shù)器

2023-12-15 10:49:43 514

514 計(jì)數(shù)器是一種被廣泛應(yīng)用于各個(gè)領(lǐng)域的實(shí)用工具,在我們的日常生活中隨處可見(jiàn)。無(wú)論是進(jìn)行時(shí)間統(tǒng)計(jì),協(xié)助工作任務(wù)的完成,還是用于科學(xué)研究和編程技術(shù),在各個(gè)領(lǐng)域都起到了重要的作用。本文將詳細(xì)介紹計(jì)數(shù)器

2024-02-03 10:04:14 589

589

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論