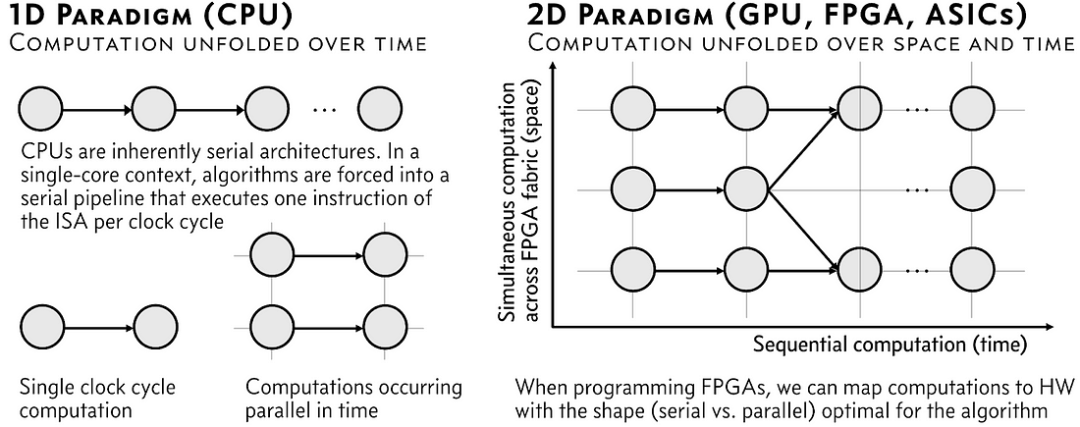

GPU。除了性能外,FPGA 的強(qiáng)大還源于它們具有適應(yīng)性,通過(guò)重用現(xiàn)有的芯片可以輕松實(shí)現(xiàn)更改,從而讓團(tuán)隊(duì)在六個(gè)月內(nèi)從想法進(jìn)展到原型(和用18個(gè)月構(gòu)建一個(gè) ASIC 相比)。”1.測(cè)試中使用的神經(jīng)網(wǎng)絡(luò)機(jī)器

2017-04-27 14:10:12

硬件公司供貨的不斷增加,GPU 在深度學(xué)習(xí)中的市場(chǎng)需求還催生了大量公共云服務(wù),這些服務(wù)為深度學(xué)習(xí)項(xiàng)目提供強(qiáng)大的 GPU 虛擬機(jī)。

但是顯卡也受硬件和環(huán)境的限制。Larzul 解釋說(shuō):“神經(jīng)網(wǎng)絡(luò)訓(xùn)練

2024-03-21 15:19:45

神經(jīng)網(wǎng)絡(luò)50例

2012-11-28 16:49:56

神經(jīng)網(wǎng)絡(luò)Matlab程序

2009-09-15 12:52:24

大家有知道labview中神經(jīng)網(wǎng)絡(luò)和SVM的工具包是哪個(gè)嗎?求分享一下,有做這方面的朋友也可以交流一下,大家共同進(jìn)步

2017-10-13 11:41:43

神經(jīng)網(wǎng)絡(luò)基本介紹

2018-01-04 13:41:23

第1章 概述 1.1 人工神經(jīng)網(wǎng)絡(luò)研究與發(fā)展 1.2 生物神經(jīng)元 1.3 人工神經(jīng)網(wǎng)絡(luò)的構(gòu)成 第2章人工神經(jīng)網(wǎng)絡(luò)基本模型 2.1 MP模型 2.2 感知器模型 2.3 自適應(yīng)線性

2012-03-20 11:32:43

將神經(jīng)網(wǎng)絡(luò)移植到STM32最近在做的一個(gè)項(xiàng)目需要用到網(wǎng)絡(luò)進(jìn)行擬合,并且將擬合得到的結(jié)果用作控制,就在想能不能直接在單片機(jī)上做神經(jīng)網(wǎng)絡(luò)計(jì)算,這樣就可以實(shí)時(shí)計(jì)算,不依賴于上位機(jī)。所以要解決的主要是兩個(gè)

2022-01-11 06:20:53

神經(jīng)網(wǎng)絡(luò)簡(jiǎn)介

2012-08-05 21:01:08

近年來(lái),深度學(xué)習(xí)的繁榮,尤其是神經(jīng)網(wǎng)絡(luò)的發(fā)展,顛覆了傳統(tǒng)機(jī)器學(xué)習(xí)特征工程的時(shí)代,將人工智能的浪潮推到了歷史最高點(diǎn)。然而,盡管各種神經(jīng)網(wǎng)絡(luò)模型層出不窮,但往往模型性能越高,對(duì)超參數(shù)的要求也越來(lái)越嚴(yán)格

2019-09-11 11:52:14

制造業(yè)而言,深度學(xué)習(xí)神經(jīng)網(wǎng)絡(luò)開(kāi)辟了令人興奮的研究途徑。為了實(shí)現(xiàn)從諸如高速公路全程自動(dòng)駕駛儀的短時(shí)輔助模式到專職無(wú)人駕駛旅行的自動(dòng)駕駛,汽車制造業(yè)一直在尋求讓響應(yīng)速度更快、識(shí)別準(zhǔn)確度更高的方法,而深度

2017-12-21 17:11:34

基于深度學(xué)習(xí)的神經(jīng)網(wǎng)絡(luò)算法

2019-05-16 17:25:05

FPGA加速的關(guān)鍵因素是什么?EdgeBoard中神經(jīng)網(wǎng)絡(luò)算子在FPGA中的實(shí)現(xiàn)方法是什么?

2021-09-28 06:37:44

MATLAB神經(jīng)網(wǎng)絡(luò)

2013-07-08 15:17:13

Matlab神經(jīng)網(wǎng)絡(luò)工具箱是什么?Matlab神經(jīng)網(wǎng)絡(luò)工具箱在同步中的應(yīng)用有哪些?

2021-04-26 06:42:29

TF之CNN:Tensorflow構(gòu)建卷積神經(jīng)網(wǎng)絡(luò)CNN的嘻嘻哈哈事之詳細(xì)攻略

2018-12-19 17:03:10

請(qǐng)問(wèn):我在用labview做BP神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)故障診斷,在NI官網(wǎng)找到了機(jī)器學(xué)習(xí)工具包(MLT),但是里面沒(méi)有關(guān)于這部分VI的幫助文檔,對(duì)于”BP神經(jīng)網(wǎng)絡(luò)分類“這個(gè)范例有很多不懂的地方,比如

2017-02-22 16:08:08

習(xí)神經(jīng)神經(jīng)網(wǎng)絡(luò),對(duì)于神經(jīng)網(wǎng)絡(luò)的實(shí)現(xiàn)是如何一直沒(méi)有具體實(shí)現(xiàn)一下:現(xiàn)看到一個(gè)簡(jiǎn)單的神經(jīng)網(wǎng)絡(luò)模型用于訓(xùn)練的輸入數(shù)據(jù):對(duì)應(yīng)的輸出數(shù)據(jù):我們這里設(shè)置:1:節(jié)點(diǎn)個(gè)數(shù)設(shè)置:輸入層、隱層、輸出層的節(jié)點(diǎn)

2021-08-18 07:25:21

項(xiàng)目名稱:基于PYNQ-Z2的神經(jīng)網(wǎng)絡(luò)圖形識(shí)別試用計(jì)劃:申請(qǐng)理由:本人為一名嵌入式軟件工程師,對(duì)FPGA有一段時(shí)間的接觸,基于FPGA設(shè)計(jì)過(guò)簡(jiǎn)單的ASCI數(shù)字芯片。目前正好在學(xué)習(xí)基于python

2019-01-09 14:48:59

項(xiàng)目名稱:基于PYNQ的神經(jīng)網(wǎng)絡(luò)自動(dòng)駕駛小車試用計(jì)劃:一、本人技術(shù)背景本人有四年以上的嵌入式開(kāi)發(fā)和三年以上的機(jī)器視覺(jué)領(lǐng)域項(xiàng)目實(shí)踐經(jīng)驗(yàn),在計(jì)算機(jī)視覺(jué)與FPGA數(shù)字圖像處理方面有較多的理論研究與項(xiàng)目實(shí)踐

2018-12-19 11:36:24

項(xiàng)目名稱:基于PYNQ的卷積神經(jīng)網(wǎng)絡(luò)加速試用計(jì)劃:申請(qǐng)理由:本人研究生在讀,想要利用PYNQ深入探索卷積神經(jīng)網(wǎng)絡(luò)的硬件加速,在PYNQ上實(shí)現(xiàn)圖像的快速處理項(xiàng)目計(jì)劃:1、在PC端實(shí)現(xiàn)Lnet網(wǎng)絡(luò)的訓(xùn)練

2018-12-19 11:37:22

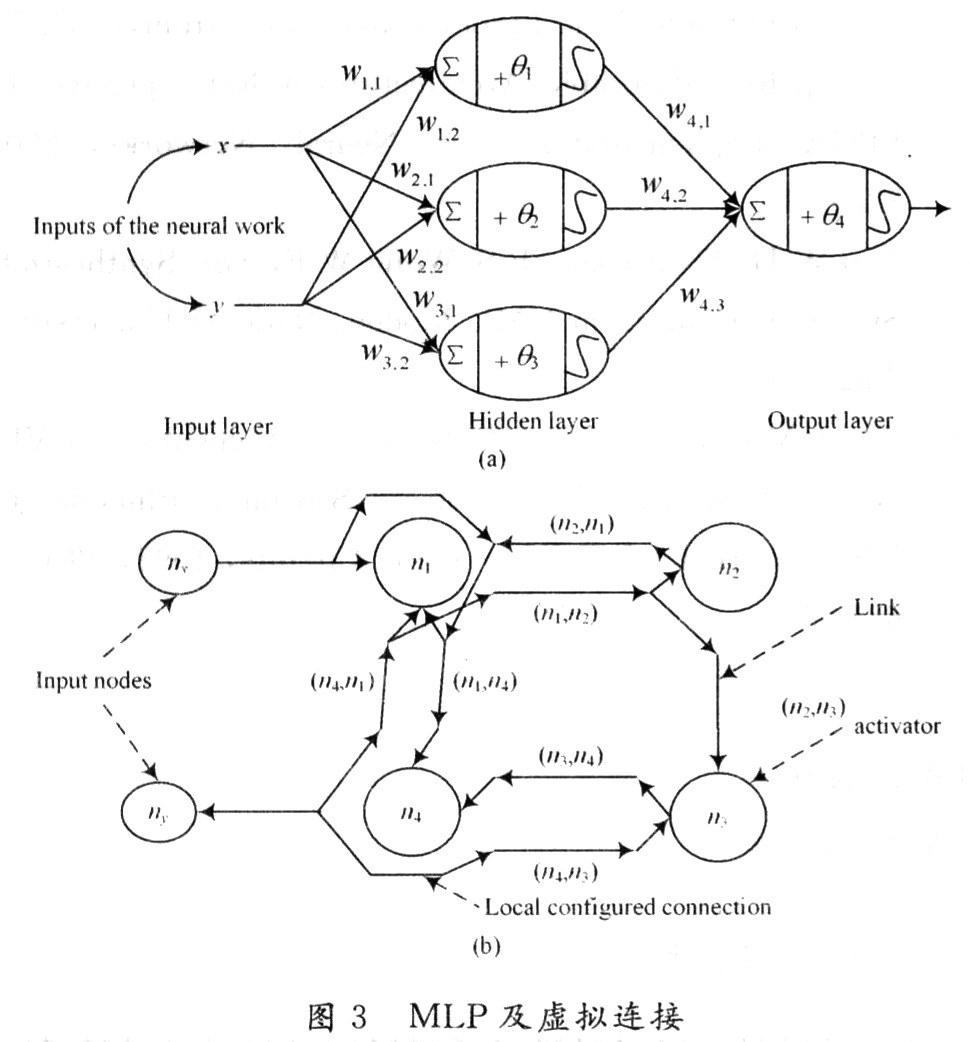

前言前面我們通過(guò)notebook,完成了在PYNQ-Z2開(kāi)發(fā)板上編寫并運(yùn)行python程序。我們的最終目的是基于神經(jīng)網(wǎng)絡(luò),完成手寫的數(shù)字識(shí)別。在這之前,有必要講一下神經(jīng)網(wǎng)絡(luò)的基本概念和工作原理。何為

2019-03-03 22:10:19

,神經(jīng)網(wǎng)絡(luò)技術(shù)的第三次發(fā)展浪潮仍在繼續(xù),在其背后,高性能CPU、GPU和FPGA、ASIC以強(qiáng)大的算力為技術(shù)的應(yīng)用落地提供了有力的支持。然而目前基于FPGA平臺(tái)搭建神經(jīng)網(wǎng)絡(luò)作為控制器,適合我們自己動(dòng)手實(shí)現(xiàn)

2019-03-02 23:10:52

是一種常用的無(wú)監(jiān)督學(xué)習(xí)策略,在使用改策略時(shí),網(wǎng)絡(luò)的輸出神經(jīng)元相互競(jìng)爭(zhēng),每一時(shí)刻只有一個(gè)競(jìng)爭(zhēng)獲勝的神經(jīng)元激活。ART神經(jīng)網(wǎng)絡(luò)由比較層、識(shí)別層、識(shí)別閾值、重置模塊構(gòu)成。其中比較層負(fù)責(zé)接收輸入樣本,并將其傳遞

2019-07-21 04:30:00

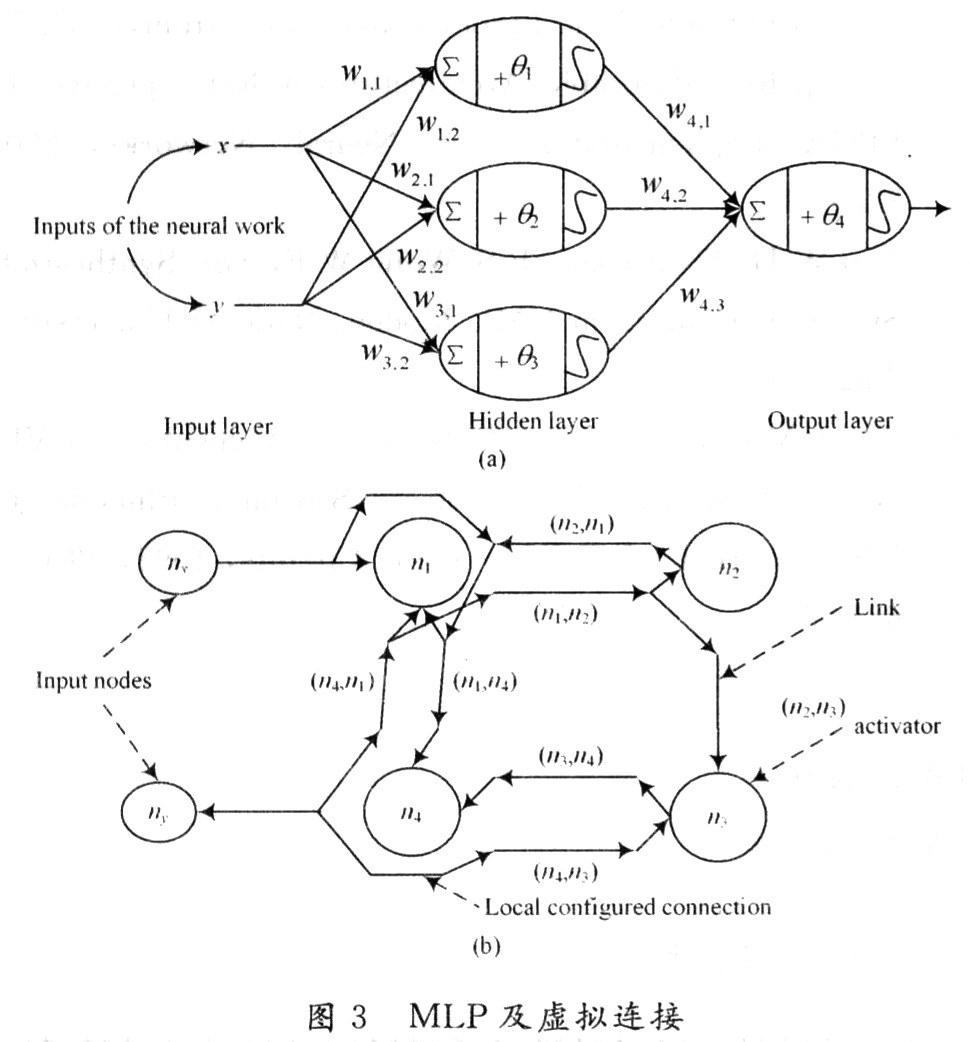

`BP神經(jīng)網(wǎng)絡(luò)首先給出只包含一個(gè)隱層的BP神經(jīng)網(wǎng)絡(luò)模型(兩層神經(jīng)網(wǎng)絡(luò)): BP神經(jīng)網(wǎng)絡(luò)其實(shí)由兩部分組成:前饋神經(jīng)網(wǎng)絡(luò):神經(jīng)網(wǎng)絡(luò)是前饋的,其權(quán)重都不回送到輸入單元,或前一層輸出單元(數(shù)據(jù)信息是單向

2019-07-21 04:00:00

人工神經(jīng)網(wǎng)絡(luò)是根據(jù)人的認(rèn)識(shí)過(guò)程而開(kāi)發(fā)出的一種算法。假如我們現(xiàn)在只有一些輸入和相應(yīng)的輸出,而對(duì)如何由輸入得到輸出的機(jī)理并不清楚,那么我們可以把輸入與輸出之間的未知過(guò)程看成是一個(gè)“網(wǎng)絡(luò)”,通過(guò)不斷地給

2008-06-19 14:40:42

人工神經(jīng)網(wǎng)絡(luò)(Artificial Neural Network,ANN)是一種類似生物神經(jīng)網(wǎng)絡(luò)的信息處理結(jié)構(gòu),它的提出是為了解決一些非線性,非平穩(wěn),復(fù)雜的實(shí)際問(wèn)題。那有哪些辦法能實(shí)現(xiàn)人工神經(jīng)網(wǎng)絡(luò)呢?

2019-08-01 08:06:21

人工神經(jīng)網(wǎng)絡(luò)課件

2016-06-19 10:15:48

`我思故我在 亮出你的觀點(diǎn)自從類神經(jīng)網(wǎng)絡(luò)算法可以用強(qiáng)大的運(yùn)算能力加以模擬之后,強(qiáng)人工智能才開(kāi)始出現(xiàn)。即便如此,以目前 CPU 的運(yùn)算能力來(lái)講,模擬類神經(jīng)網(wǎng)絡(luò)算法的代價(jià)非常之大,于是有人想到了用

2017-08-23 15:42:16

簡(jiǎn)單理解LSTM神經(jīng)網(wǎng)絡(luò)

2021-01-28 07:16:57

圖卷積神經(jīng)網(wǎng)絡(luò)

2019-08-20 12:05:29

FPGA實(shí)現(xiàn)。易于適應(yīng)新的神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)深度學(xué)習(xí)是一個(gè)非常活躍的研究領(lǐng)域,每天都在設(shè)計(jì)新的 DNN。其中許多結(jié)合了現(xiàn)有的標(biāo)準(zhǔn)計(jì)算,但有些需要全新的計(jì)算方法。特別是在具有特殊結(jié)構(gòu)的網(wǎng)絡(luò)難以在 GPU 上

2023-02-17 16:56:59

優(yōu)化神經(jīng)網(wǎng)絡(luò)訓(xùn)練方法有哪些?

2022-09-06 09:52:36

全連接神經(jīng)網(wǎng)絡(luò)和卷積神經(jīng)網(wǎng)絡(luò)的區(qū)別

2019-06-06 14:21:42

以前的神經(jīng)網(wǎng)絡(luò)幾乎都是部署在云端(服務(wù)器上),設(shè)備端采集到數(shù)據(jù)通過(guò)網(wǎng)絡(luò)發(fā)送給服務(wù)器做inference(推理),結(jié)果再通過(guò)網(wǎng)絡(luò)返回給設(shè)備端。如今越來(lái)越多的神經(jīng)網(wǎng)絡(luò)部署在嵌入式設(shè)備端上,即

2021-12-23 06:16:40

卷積神經(jīng)網(wǎng)絡(luò)為什么適合圖像處理?

2022-09-08 10:23:10

卷積神經(jīng)網(wǎng)絡(luò)(CNN)究竟是什么,鑒于神經(jīng)網(wǎng)絡(luò)在工程上經(jīng)歷了曲折的歷史,您為什么還會(huì)在意它呢? 對(duì)于這些非常中肯的問(wèn)題,我們似乎可以給出相對(duì)簡(jiǎn)明的答案。

2019-07-17 07:21:50

分析了目前的特殊模型結(jié)構(gòu),最后總結(jié)并討論了卷積神經(jīng)網(wǎng)絡(luò)在相關(guān)領(lǐng)域的應(yīng)用,并對(duì)未來(lái)的研究方向進(jìn)行展望。卷積神經(jīng)網(wǎng)絡(luò)(convolutional neural network,CNN) 在計(jì)算機(jī)視覺(jué)[1-

2022-08-02 10:39:39

卷積神經(jīng)網(wǎng)絡(luò)的優(yōu)點(diǎn)

2020-05-05 18:12:50

卷積神經(jīng)網(wǎng)絡(luò)的層級(jí)結(jié)構(gòu) 卷積神經(jīng)網(wǎng)絡(luò)的常用框架

2020-12-29 06:16:44

什么是卷積神經(jīng)網(wǎng)絡(luò)?ImageNet-2010網(wǎng)絡(luò)結(jié)構(gòu)是如何構(gòu)成的?有哪些基本參數(shù)?

2021-06-17 11:48:22

反饋神經(jīng)網(wǎng)絡(luò)算法

2020-04-28 08:36:58

FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)關(guān)鍵問(wèn)題分析基于FPGA的ANN實(shí)現(xiàn)方法基于FPGA的神經(jīng)網(wǎng)絡(luò)的性能評(píng)估及局限性

2021-04-30 06:58:13

法是可以硬件實(shí)現(xiàn)的,并且具有較高的數(shù)據(jù)加密速度,時(shí)鐘頻率可達(dá)50 MHz以上【關(guān)鍵詞】:神經(jīng)網(wǎng)絡(luò);;混沌吸引子;;公鑰密碼;;FPGA【DOI】:CNKI:SUN:XDZK.0.2010-02-008

2010-04-24 09:15:41

最近在學(xué)習(xí)電機(jī)的智能控制,上周學(xué)習(xí)了基于單神經(jīng)元的PID控制,這周研究基于BP神經(jīng)網(wǎng)絡(luò)的PID控制。神經(jīng)網(wǎng)絡(luò)具有任意非線性表達(dá)能力,可以通過(guò)對(duì)系統(tǒng)性能的學(xué)習(xí)來(lái)實(shí)現(xiàn)具有最佳組合的PID控制。利用BP

2021-09-07 07:43:47

基于BP神經(jīng)網(wǎng)絡(luò)的辨識(shí)

2018-01-04 13:37:27

基于RBF神經(jīng)網(wǎng)絡(luò)的辨識(shí)

2018-01-04 13:38:52

i.MX 8開(kāi)發(fā)工具從相機(jī)獲取數(shù)據(jù)并使用一個(gè)GPU并應(yīng)用圖像分割算法。然后將該信息饋送到專用于識(shí)別交通標(biāo)志的神經(jīng)網(wǎng)絡(luò)推理引擎的另一GPU。

2019-05-29 10:50:46

FPGA 上實(shí)現(xiàn)卷積神經(jīng)網(wǎng)絡(luò) (CNN)。CNN 是一類深度神經(jīng)網(wǎng)絡(luò),在處理大規(guī)模圖像識(shí)別任務(wù)以及與機(jī)器學(xué)習(xí)類似的其他問(wèn)題方面已大獲成功。在當(dāng)前案例中,針對(duì)在 FPGA 上實(shí)現(xiàn) CNN 做一個(gè)可行性研究

2019-06-19 07:24:41

原文鏈接:http://tecdat.cn/?p=5725 神經(jīng)網(wǎng)絡(luò)是一種基于現(xiàn)有數(shù)據(jù)創(chuàng)建預(yù)測(cè)的計(jì)算系統(tǒng)。如何構(gòu)建神經(jīng)網(wǎng)絡(luò)?神經(jīng)網(wǎng)絡(luò)包括:輸入層:根據(jù)現(xiàn)有數(shù)據(jù)獲取輸入的層隱藏層:使用反向傳播優(yōu)化輸入變量權(quán)重的層,以提高模型的預(yù)測(cè)能力輸出層:基于輸入和隱藏層的數(shù)據(jù)輸出預(yù)測(cè)

2021-07-12 08:02:11

如何用stm32cube.ai簡(jiǎn)化人工神經(jīng)網(wǎng)絡(luò)映射?如何使用stm32cube.ai部署神經(jīng)網(wǎng)絡(luò)?

2021-10-11 08:05:42

某人工神經(jīng)網(wǎng)絡(luò)的FPGA處理器能夠?qū)?shù)據(jù)進(jìn)行運(yùn)算處理,為了實(shí)現(xiàn)集數(shù)據(jù)通信、操作控制和數(shù)據(jù)處理于一體的便攜式神經(jīng)網(wǎng)絡(luò)處理器,需要設(shè)計(jì)一種基于嵌入式ARM內(nèi)核及現(xiàn)場(chǎng)可編程門陣列FPGA的主從結(jié)構(gòu)處理系統(tǒng)滿足要求。

2021-05-21 06:35:27

)第二步:使用Lattice sensAI 軟件編譯已訓(xùn)練好的神經(jīng)網(wǎng)絡(luò),定點(diǎn)化網(wǎng)絡(luò)參數(shù)。該軟件會(huì)根據(jù)神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)和預(yù)設(shè)的FPGA資源進(jìn)行分析并給出性能評(píng)估報(bào)告,此外用戶還可以在軟件中做

2020-11-26 07:46:03

神經(jīng)網(wǎng)絡(luò)(Neural Networks)是人工神經(jīng)網(wǎng)絡(luò)(Ar-tificial Neural Networks)的簡(jiǎn)稱,是當(dāng)前的研究熱點(diǎn)之一。人腦在接受視覺(jué)感官傳來(lái)的大量圖像信息后,能迅速做出反應(yīng)

2019-08-08 06:11:30

現(xiàn)有的圖數(shù)據(jù)規(guī)模極大,導(dǎo)致時(shí)序圖神經(jīng)網(wǎng)絡(luò)的訓(xùn)練需要格外長(zhǎng)的時(shí)間,因此使用多GPU進(jìn)行訓(xùn)練變得成為尤為重要,如何有效地將多GPU用于時(shí)序圖神經(jīng)網(wǎng)絡(luò)訓(xùn)練成為一個(gè)非常重要的研究議題。本文提供了兩種方式來(lái)

2022-09-28 10:37:20

本文提出了一個(gè)基于FPGA 的信息處理的實(shí)例:一個(gè)簡(jiǎn)單的人工神經(jīng)網(wǎng)絡(luò)應(yīng)用Verilog 語(yǔ)言描述,該數(shù)據(jù)流采用模塊化的程序設(shè)計(jì),并考慮了模塊間數(shù)據(jù)傳輸信號(hào)同 步的問(wèn)題,有效地解決了人工神經(jīng)網(wǎng)絡(luò)并行數(shù)據(jù)處理的問(wèn)題。

2021-05-06 07:22:07

人工神經(jīng)網(wǎng)絡(luò)在很多領(lǐng)域得到了很好的應(yīng)用,尤其是具有分布存儲(chǔ)、并行處理、自學(xué)習(xí)、自組織以及非線性映射等特點(diǎn)的網(wǎng)絡(luò)應(yīng)用更加廣泛。嵌入式便攜設(shè)備也越來(lái)越多地得到應(yīng)用,多數(shù)是基于ARM內(nèi)核及現(xiàn)場(chǎng)可編程門陣列

2019-09-20 06:15:20

例如BP神經(jīng)網(wǎng)絡(luò)

2018-03-07 19:44:24

有提供編寫神經(jīng)網(wǎng)絡(luò)預(yù)測(cè)程序服務(wù)的嗎?

2011-12-10 13:50:46

求助地震波神經(jīng)網(wǎng)絡(luò)程序,共同交流!!

2013-05-11 08:14:19

小女子做基于labview的蒸發(fā)過(guò)程中液位的控制,想使用神經(jīng)網(wǎng)絡(luò)pid控制,請(qǐng)問(wèn)這個(gè)控制方法可以嗎?有誰(shuí)會(huì)神經(jīng)網(wǎng)絡(luò)pid控制么。。。叩謝

2016-09-23 13:43:16

求助大神 小的現(xiàn)在有個(gè)難題: 一組車重實(shí)時(shí)數(shù)據(jù) 對(duì)應(yīng)一個(gè)車重的最終數(shù)值(一個(gè)一維數(shù)組輸入對(duì)應(yīng)輸出一個(gè)數(shù)值) 這其中可能經(jīng)過(guò)均值、方差、去掉N個(gè)最大值、、、等等的計(jì)算 我的目的就是弄清楚這個(gè)中間計(jì)算過(guò)程 最近實(shí)在想不出什么好辦法就打算試試神經(jīng)網(wǎng)絡(luò) 請(qǐng)教大神用什么神經(jīng)網(wǎng)絡(luò)好求神經(jīng)網(wǎng)絡(luò)程序

2016-07-14 13:35:44

1、加速神經(jīng)網(wǎng)絡(luò)的必備開(kāi)源項(xiàng)目 到底純FPGA適不適合這種大型神經(jīng)網(wǎng)絡(luò)的設(shè)計(jì)?這個(gè)問(wèn)題其實(shí)我們不適合回答,但是FPGA廠商是的實(shí)際操作是很有權(quán)威性的,現(xiàn)在不論是Intel還是Xilinx都沒(méi)有在

2022-10-24 16:10:50

最簡(jiǎn)單的神經(jīng)網(wǎng)絡(luò)

2019-09-11 11:57:36

的研究具有重要意義.模糊神經(jīng)網(wǎng)絡(luò)是人工神經(jīng)網(wǎng)絡(luò)和模糊系統(tǒng)相結(jié)合的新型網(wǎng)絡(luò)結(jié)構(gòu),把它應(yīng)用于語(yǔ)音識(shí)別系統(tǒng),使系統(tǒng)不僅具有非線性、自適應(yīng)性、魯棒性和自學(xué)習(xí)等神經(jīng)網(wǎng)絡(luò)本來(lái)的優(yōu)勢(shì),也具有模糊推理和模糊劃分等模糊邏輯全文下載

2010-05-06 09:05:35

脈沖耦合神經(jīng)網(wǎng)絡(luò)(PCNN)在FPGA上的實(shí)現(xiàn),實(shí)現(xiàn)數(shù)據(jù)分類功能,有報(bào)酬。QQ470345140.

2013-08-25 09:57:14

我在matlab中訓(xùn)練好了一個(gè)神經(jīng)網(wǎng)絡(luò)模型,想在labview中調(diào)用,請(qǐng)問(wèn)應(yīng)該怎么做呢?或者labview有自己的神經(jīng)網(wǎng)絡(luò)工具包嗎?

2018-07-05 17:32:32

請(qǐng)問(wèn)一下fpga加速神經(jīng)網(wǎng)絡(luò)為什么要用arm核呢?用其他的不行嗎

2022-07-25 14:37:58

時(shí)空記憶。增加了幾個(gè)非局部模塊后,我們的“非局部神經(jīng)網(wǎng)絡(luò)”結(jié)構(gòu)能比二維和三維卷積網(wǎng)絡(luò)在視頻分類中取得更準(zhǔn)確的結(jié)果。另外,非局部神經(jīng)網(wǎng)絡(luò)在計(jì)算上也比三維卷積神經(jīng)網(wǎng)絡(luò)更加經(jīng)濟(jì)。我們在 Kinetics

2018-11-12 14:52:50

模糊神經(jīng)網(wǎng)絡(luò)提供了從人工神經(jīng)網(wǎng)絡(luò)中模糊規(guī)則的抽取。本文研究模糊神經(jīng)網(wǎng)絡(luò)的自適應(yīng)學(xué)習(xí)、規(guī)則插入和抽取及神經(jīng)-模糊推理的FuNN 模型。把遺傳算法作為系統(tǒng)模糊規(guī)則選擇的自

2009-06-06 13:45:42 18

18 基于FPGA的人工神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)方法的研究

引 言 人工神經(jīng)網(wǎng)絡(luò)(Artificial Neural Network,ANN)是一種類似生物神經(jīng)網(wǎng)絡(luò)的信息處理結(jié)構(gòu),它的提出是為了

2009-11-17 17:17:20 1119

1119

基于FPGA的人工神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)方法的研究

引言

人工神經(jīng)網(wǎng)絡(luò)(ArtificialNeuralNetwork,ANN)是一種類似生物神經(jīng)網(wǎng)絡(luò)的信息處理結(jié)構(gòu),它的提出是為了解決一些非線

2009-11-21 16:25:24 4633

4633 人工神經(jīng)網(wǎng)絡(luò),人工神經(jīng)網(wǎng)絡(luò)是什么意思

神經(jīng)網(wǎng)絡(luò)是一門活躍的邊緣性交叉學(xué)科.研究它的發(fā)展過(guò)程和前沿問(wèn)題,具有重要的理論意義

2010-03-06 13:39:01 3296

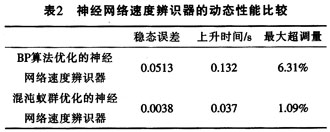

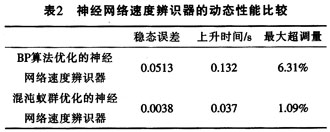

3296 近年來(lái),由于神經(jīng)網(wǎng)絡(luò)的研究取得了長(zhǎng)足的進(jìn)展,基于BP神經(jīng)網(wǎng)絡(luò)模型的速度辨識(shí)方法得到了廣泛研究,但其仍存在收斂速度慢、易陷入局部極小值等問(wèn)題,因此,對(duì)神經(jīng)網(wǎng)絡(luò)的優(yōu)化

2010-06-14 06:52:32 1105

1105

神經(jīng)網(wǎng)絡(luò)圖像壓縮算法的FPGA實(shí)現(xiàn)技術(shù)研究,下來(lái)看看

2016-09-17 07:29:23 19

19 基于BP神經(jīng)網(wǎng)絡(luò)的唇裂圖像研究_朱霞

2017-03-19 11:33:11 0

0 基于神經(jīng)網(wǎng)絡(luò)的聚類方法研究_胡偉

2017-03-16 09:37:53 0

0 針對(duì)深度神經(jīng)網(wǎng)絡(luò)在分布式多機(jī)多GPU上的加速訓(xùn)練問(wèn)題,提出一種基于虛擬化的遠(yuǎn)程多GPU調(diào)用的實(shí)現(xiàn)方法。利用遠(yuǎn)程GPU調(diào)用部署的分布式GPU集群改進(jìn)傳統(tǒng)一對(duì)一的虛擬化技術(shù),同時(shí)改變深度神經(jīng)網(wǎng)絡(luò)在分布式

2018-03-29 16:45:25 0

0 這篇文章為大家介紹了一下面向低功耗AI芯片上的神經(jīng)網(wǎng)絡(luò)設(shè)計(jì),隨著這幾年神經(jīng)網(wǎng)絡(luò)和硬件(CPU,GPU,FPGA,ASIC)的迅猛發(fā)展,深度學(xué)習(xí)在包...

2020-12-14 23:40:08 536

536 基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)說(shuō)明。

2021-04-28 11:24:23 25

25 海量文本分析是實(shí)現(xiàn)大數(shù)據(jù)理解和價(jià)值發(fā)現(xiàn)的重要手段,其中文本分類作為自然語(yǔ)言處理的經(jīng)典問(wèn)題受到研究者廣泛關(guān)注,而人工神經(jīng)網(wǎng)絡(luò)在文本分析方面的優(yōu)異表現(xiàn)使其成為目前的主要研究方向。在此背景下,介紹卷積

2021-05-13 16:34:34 48

48 基于FPGA的神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)方法說(shuō)明。

2021-06-01 09:35:16 37

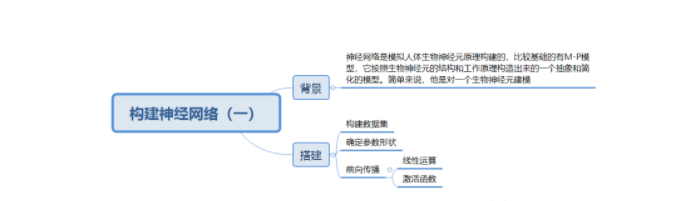

37 神經(jīng)網(wǎng)絡(luò)是模擬人體生物神經(jīng)元原理構(gòu)建的,比較基礎(chǔ)的有M-P模型,它按照生物

神經(jīng)元的結(jié)構(gòu)和工作原理構(gòu)造出來(lái)的一個(gè)抽象和簡(jiǎn)化的模型。

2023-02-24 16:06:52 1080

1080

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論