1 引言

FPGA 具有高速度、高集成度,可重復編程的特點,將其用于電路系統設計,可簡化電路設計,增強電路功能。而作為電路系統的“中樞控制神經”,FPGA 的故障會引起整個電路系統的癱瘓,而用一般的測試方法很難對其實施故障測試診斷。

目前,某修理單位的自動測試設備對不含上述復雜邏輯器件電路板的測試診斷已有解決措施。但這些自動測試設備尚不能對含復雜邏輯器件電路板進行有效地測試,現有的自動測試設備未包含DSP和FPGA、CPLD 等仿真系統,不能對復雜邏輯器件的工作狀態進行有效控制。

因此,含FPGA 電路板測試及故障診斷方法的研究,將顯著提高電子裝備的可維修性,使復雜邏輯器件給電子裝備水平帶來的提高能得到最大限度的發揮。

2 基于邊界掃描的含FPGA電路板測試

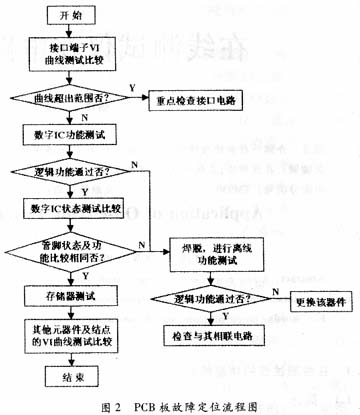

系統級測試一般采用BIT( 內嵌測試) ,即在系統運行過程中,由內嵌測試程序實時監控系統的運行狀態。一旦有故障發生,內嵌測試程序報告是哪個部件出錯,就可拔出該部件進行修理。對現場級維修而言,含FPGA 器件電路板的故障檢測要求快速準確,方法簡單實用,能在最短時間內自動將故障定位到現場可更換單元( LRU) ,多采用邊界掃描測試( BST,Boundary Scan Test) 方法。

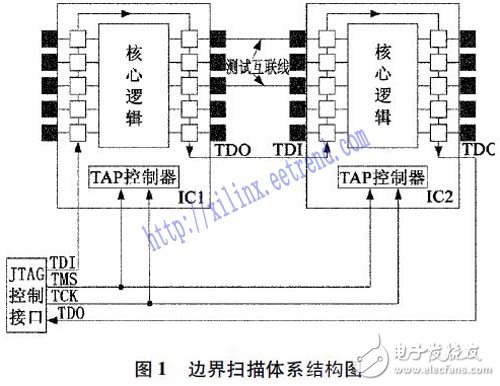

邊界掃描是一種可測試的結構技術,用來解決測試探針所不能實現的測試問題。它是在芯片的I /O 端上增加移位寄存器,把這些寄存器連接起來,加上時鐘復位、測試方式選擇以及掃描輸入和輸出端口,而形成邊界掃描通道。由于邊界掃描測試可直接獲得芯片管腳的信息,所以完全可以實現芯片級、板極、系統級的測試。每個IEEE1149. 1 兼容的器件,都包括一個4 線或5 線的測試端口( TAP) 、一個狀態機( TAP 控制器) 和由邊界掃描單元構成的邊界掃描移位寄存器。其接口和總線常被稱為JTAG 接口和JTAG 總線,其結構如圖1 所示。

3 非完全邊界掃描FPGA 電路板測試

由于測試性設計水平的限制,由邊界掃描器件和非邊界掃描器件組成的非完全邊界掃描電路板廣泛存在,如何對該類電路進行故障檢測與隔離是需要研究的關鍵問題。

3. 1 非完全邊界掃描電路板簇測試

利用“虛擬數據通道法”,通過電路板上的BS器件實現非BS 器件的測試。其基本原理為: 首先將常規器件芯片聚類合并構成相應的邏輯功能簇“cluster”,其輸入輸出端口與若干BS 器件相連,按照一定的算法生成簇測試矢量。邊界掃描測試開始時,簇測試矢量通過其輸入端BS 器件加載,測試響應由輸出端BS 器件捕獲并通過邊界掃描鏈移出,然后進行結果分析和處理。這種方法可以利用BS器件的虛擬通道對與其相連接的cluster 輸入輸出節點進行診斷,即通過虛擬輸入和虛擬輸出對邏輯功能簇進行診斷。對不與BS 器件相連的剩余輸入輸出端口,可以用其它方式加載測試矢量和捕獲測試響應,進行實體輸入與實體輸出,即串行測試與并行測試相結合。

3. 2 基于BS 與數字I /O 測試向量的測試方法

在含有FPGA 器件的電路板中有部分電路,屬于非邊界掃描器件,位于電路板邊緣連接器和FPGA器件形成的邊界掃描鏈之間。這部分器件的功能測試難以進行,可以采用邊界掃描測試技術與傳統的外部輸入矢量測試相結合的方法。

該方法能實現非邊界掃描器件的測試,但由于數字I /O 模塊輸入的矢量信號必須等到邊界掃描完成一個循環周期后,才能接著輸入下一個向量,受邊界掃描測試矩陣中并行測試向量數目的影響,測試耗時長,尤其是與外部I /O 之間的時序難于控制,是研究的重點和難點。

3. 3 擴展邊界掃描測試

針對基于邊界掃描技術的測試系統實現難度大、故障覆蓋率低等問題,提出了MERGE 法邊界掃描技術。將一個完整的數字電路分為非邊界掃描芯片簇、邊界掃描芯片簇和混合芯片簇。通過邊界掃描擴展卡,構造UUT 的邊界掃描結構,然后通過邊界掃描技術進行測試[3]。

該方法無法在現有ATE上實現自動測試,需要構建新的測試系統。

4 基于功能建模的含FPGA電路板測試

以上方法無法完成整板功能的測試,本文通過含FPGA 電路板功能建模,結合LASAR( Logic Automatic Simulate and Response) 仿真軟件,在某型ATE上實現含FPGA 電路板的自動測試。

4. 1 基于LASAR 的含FPGA 電路板測試方案

LASAR 作為數字電路測試開發和邏輯分析的仿真軟件系統,已被全球眾多國防電子與航空工程所采用,LASAR 的LSRTAP 數據格式已被IEEE制定為標準數字測試交換格式。LASAR 后處理軟件可直接加載在ATE 設備上對被仿真電路板進行測試。目前,許多ATE 設備都提供了LASAR 后處理軟件及其相關的技術文件。

對于以上平臺,完成電路板上各元件的建模是LASAR 仿真及生成后處理文件的關鍵。在LASAR V6.60 中,VITAL( VHDL Initiative Towards ASIC Libraries)支持建立FPGA 和ASIC 結構模型。

基于VITAL 語言的含FPGA 電路板測試步驟如下:

( 1) 在FPGA 開發環境中,對FPGA 器件進行功能描述;

( 2) 編譯FPGA 器件的功能描述文件,輸出FPGA的配置文件和VITAL 標準格式數據,建立FPGA器件的軟件模型;

( 3) 將VITAL 標準格式數據導入LASAR,建立FPGA 軟件模型,實現FPGA 功能建模;

( 4) 把電路板的網表文件導入LASAR 仿真軟件,將仿真的結果導出,經過后處理,應用到ATE上,對電路板進行測試診斷。

對于測試方而言,由于難以得到電路板設計資料,FPGA 功能建模是研究的難點。

4. 2 基于VITAL 語言的FPGA 功能建模

VITAL 是在IEEE std 1076 - 1993 基礎上開發的,提供面向ASIC 設計的VHDL 模型基準語言,其目的是促進ASIC 模型庫在工業VHDL 描述和模擬中的應用,它為ASIC 庫的建立、電路設計的描述提供格式相對固定的描述方法,并為提高VHDL 模擬性能提供依據和基礎。

VITAL 語言標準包括時序程序包VITAL_Timing、建立模型用的規范文檔和基本元件包VITAL_Primitives,并引進Verilog SDF ( Standard Delay Format)延時機制。VITAL_Primitives 包括基本邏輯元件和實用元件兩部分。基本邏輯元件模型執行基本邏輯操作,實現基本元件的功能,實用元件支持多驅動源決斷操作和查表操作。時序程序包中定義了VITAL 基本類型,延時計算函數和過程,時序約束檢查過程等。VITAL_Primitives 使用VITAL_Timing 程序包中定義的類型和函數。VITAL 中延時和時序約束都定義為VHDL 類屬參數,并規定SDF 標準格式與VITAL 間對應關系,允許仿真程序直接讀人SDF文件,覆蓋類屬參數的默認值[9]。

VITAL 模型方法能夠將FPGA 器件開發軟件的設計輸出,轉化為LASAR 仿真軟件識別的器件模型,大大簡化FPGA 器件的功能建模過程。

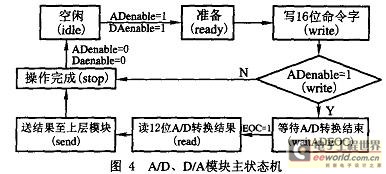

4. 3 基于LASAR 的含FPGA 電路板仿真

設計網表、SDF 文件和宏單元庫是生成LASAR模型所需的重要數據。LASAR 中的VITAL 和Verilog轉換器能分別將SDF 文件、VHDL 和Verilog 網表轉換為LASAR 模型。

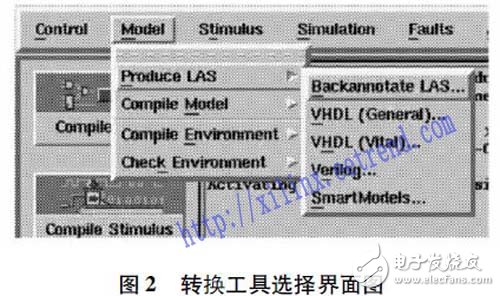

在LASAR 圖形界面中“Model”工具欄下的“Produce LAS”中選擇相應轉換工具,如圖2 所示。

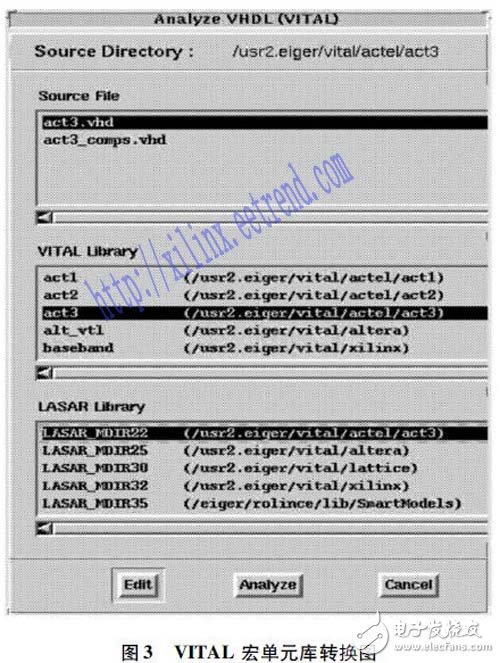

若為第一次使用該系列器件,需要將所有宏單元庫轉換并保存到所有LASAR 用戶的庫目錄中。如圖3 所示,選擇VHDL 源文件,確定VITAL 庫,然后確定結果保存路徑。

器件轉換過程分兩步執行,首先將VHDL 設計網表轉換為LASAR 結構模型,該過程和宏單元庫轉化過程類似,如圖4 所示。選擇VHDL 或Verilog 源文件、選擇VITAL 庫,然后確定目標路徑( 通常為library.lib) 。

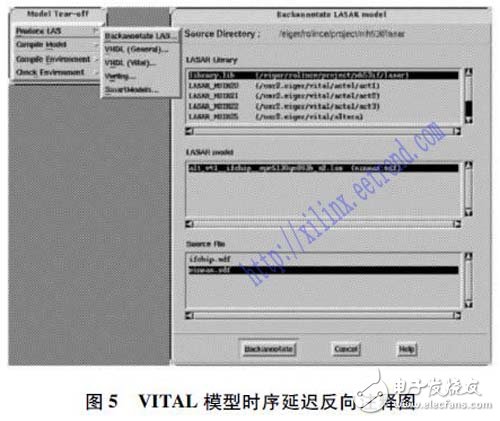

完成以上步驟后,需要將SDF 文件中包含的時序信息需要反向注釋成轉換設計文件。如圖5 所示,通過選擇“Produce LAS”下的“Backannotated”選項,確定設計文檔和該設計的SDF 文件。LASAR 通過編譯器件模型,并啟動TIMCHG( 時間轉換) 程序。TIMCHG 讀取SDF 文件,并為器件節點分配時序屬性。其結果是一個插入到本地library. lib 文件中的. BAV 文件( 反向注釋模型) 。成功反向注釋器件模型后,就可以進行整板模型編譯和仿真。

并不是所有的設計100% 兼容VITAL,有一些VITAL 和Verilog 結構不能徹底轉換。也可能有一些設計,違反基本的LASAR 限制。文獻[5]介紹了這些約束和限制。

4. 4 基于LASAR 后處理的含FPGA 電路板測試

LASAR 后處理LSRTAP 生成的TAP 文件數據包括電路板功能測試、故障字典檢測和探筆引導診斷三種可獨立或混合的測試數據,該數據格式已被IEEE 制定為國際標準數字測試交換格式( DTIF -Digital Test Interchange Format) ,為基于數字仿真的TPS 的開發和交付提供了一種標準的信息內容和數據格式。

某型電路板自動測試系統完全支持LASAR 生成的后處理文件。首先應用LASAR 數字仿真軟件按照上述提到的測試數據開發程序,生成電路板的測試數據,建立標準的“交換測試數據庫”結構,然后將39個LSRTAP文件自動轉換到對應的標準“交換測試數據庫”中。ATE 直接調用數據庫中的測試數據,進行測試和診斷。

5 結束語

由邊界掃描和非邊界掃描器件組成的非完全邊界掃描電路板普遍存在,其故障檢測與隔離是板級維修測試的難題。本文提出了一種基于功能建模的含FPGA 電路板測試方法。利用FPGA開發環境中生成VITAL 模型并導入LASAR,通過電路板的好板仿真和故障仿真,生成后處理文件,經ATE 調用完成含FPGA電路板的功能測試。該方法利用現有測試系統,實現了該類電路板的測試與故障診斷。

電子發燒友App

電子發燒友App

評論