PCI Express(PCIe)是一種高性能互連協(xié)議,可應(yīng)用于網(wǎng)絡(luò)適配、圖形加速、服務(wù)器、大數(shù)據(jù)傳輸、嵌入式系統(tǒng)等領(lǐng)域。PCIe協(xié)議在軟件層上可兼容于PCI和PCI—X,但同時(shí)也有明顯的不同。在兩個(gè)設(shè)備間,其是一種基于數(shù)據(jù)包、串行、點(diǎn)對點(diǎn)的互連,因此所連接設(shè)備獨(dú)享通道帶寬。根據(jù)使用的版本號和通道數(shù),其性能具有可擴(kuò)展性。對于PCIe 2.0,每條通道在每個(gè)方向上的數(shù)據(jù)傳輸速率是5.0 Gbit·s-1。從PCIe×1~PCIe×16,能滿足一定時(shí)間內(nèi)出現(xiàn)的低速設(shè)備和高速設(shè)備的需求。

Altera提供了兼容于PCIe 1.0和PCIe 2.0的解決方案,無論是作為根節(jié)點(diǎn)還是端點(diǎn),都可以通過嵌入在FPGA內(nèi)部的可配置硬核IP模塊實(shí)現(xiàn),而不占用可編程資源,這既節(jié)省了資源也提高了應(yīng)用的可靠性。Altera的IP編譯器可以提供×1,×2,×4,×8的通道接口。本文主要介紹采用Cyclone IV GX系列的FPGA來實(shí)現(xiàn)×4的PCIe接口所涉及的硬件電氣規(guī)范、協(xié)議規(guī)范等。

1 PCIe總線體系和Cyclone IV GX

1.1 PCIe總線體系概述

PCI Express是一種基于數(shù)據(jù)包、串行、點(diǎn)到點(diǎn)的高性能互連總線協(xié)議。其定義了一種分層的體系結(jié)構(gòu),包括軟件層、處理層、數(shù)據(jù)鏈路層和物理層。其中軟件層是保持與PCI總線兼容的關(guān)鍵,PCIe采用與PCI和PCI—X相同的使用模型和讀寫通信模型。支持各種常見事物,如存儲器讀寫事物,IO讀寫事物和配置讀寫事物。而且由于地址空間模型沒有變化,所以現(xiàn)有的操作系統(tǒng)和驅(qū)動軟件無需進(jìn)行修改即可在PCIe系統(tǒng)上運(yùn)行。此外PCIe還支持一種稱為消息事物的新事物類型。這是由于PCIe協(xié)議在取消了許多邊帶信號的情況下,需要有替代的方法來通知主機(jī)系統(tǒng)對設(shè)備中斷,電源管理,熱插拔支持等進(jìn)行服務(wù)。

1.2 Altera Cyclone IV GX系列FPGA

Cyclone IV GX FPGA采用Altera成熟的GX收發(fā)器技術(shù),具有出眾的抖動性能和優(yōu)異的信號完整性。利用靈活的收發(fā)器時(shí)鐘體系結(jié)構(gòu),可充分利用收發(fā)器所有可用資源,實(shí)現(xiàn)多種協(xié)議。Cyclone IV GX FPGA為根端口和端點(diǎn)配置的PCI Express×1、×2和×4提供唯一的硬核知識產(chǎn)權(quán)(IP)模塊。因此不用再接入其他專用的PCIe協(xié)議芯片,即可實(shí)現(xiàn)端到端的高速數(shù)據(jù)傳輸。

Cyclone IV系列的FPGA還支持一系列外部存儲器,包括DDR2 SDRAM,DDR SDRAM,QDR SDRAM。Altera可提供速度最快、效率最高、最低延遲的存儲器控制器,使得FPGA可以接入現(xiàn)有的更高速的存儲器件。專用的DQS和DQ引腳在芯片級的布線上進(jìn)行優(yōu)化以減少抖動和增大余量上,且固定在芯片四周的特定位置。高速外部存儲器在眾多應(yīng)用中是重要的系統(tǒng)組成部分,如視頻圖像處理,數(shù)據(jù)通信與存儲,以及DMA等。

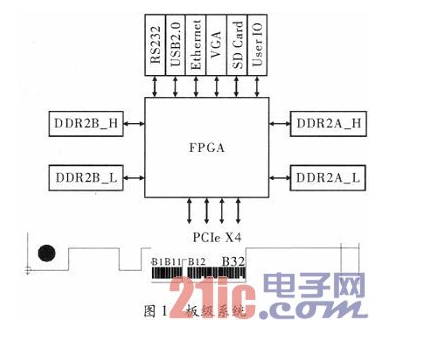

2 板級系統(tǒng)和部分走線阻抗

2.1 板級系統(tǒng)

充分利用FPGA左右兩側(cè)的存儲器接口,分別掛兩片Micron的DDR2 SDRAM顆粒,作為DMA緩存。FPGA的下側(cè)是高速收發(fā)器接口,共有4組GXB[3:0],分別經(jīng)差分鏈路接入PCIe ×4金手指。其中GXB[3:2]是復(fù)用接口,通過改變T節(jié)點(diǎn)的耦合電容,可接入兩路高速ADC。FPGA上側(cè)接口包括USB PHY、千兆以太網(wǎng)PHY、串口、SD卡以及VGA接口等。FPGA有3個(gè)時(shí)鐘輸入,分別是:(1)來自PCIe接口的參考時(shí)鐘PCIE_REFCLK。(2)來自專用時(shí)鐘模塊的GXB_REFCLK。(3)來自25 MHz有源晶振的SYM_CLK。

2.2 關(guān)鍵走線的阻抗控制

圖2是PCB疊層結(jié)構(gòu)示意圖,其中L1,L3,L6,L8是信號層;L2,L7是地層;L4,L5是電層。信號層分別參考臨近的地層或電源層。其中PCIe鏈路僅在L1和L8布線,基于以上疊層結(jié)構(gòu),確定PCIe接口的100 Ω差分阻抗走線的線寬和線間距分別為4 mil(1mil=0.0254 mm)和8.1 mil,差分線長容差在5 mil之內(nèi)。

DDR2 SDRAM的布線按照SSTL_18標(biāo)準(zhǔn),DQ/DQS信號在L3和L6層,確定50 Ω單端走線線寬5.3 mil,等長控制在10 mil之內(nèi)。時(shí)鐘走線是100 Ω差分阻抗,布線時(shí)放在頂層和L6層。在時(shí)鐘走線過孔附近打上接地過孔,作為信號回流路徑,以盡量減少阻抗不連續(xù)對信號完整性造成的影響。

3 PCIe應(yīng)用層設(shè)計(jì)方案及仿真

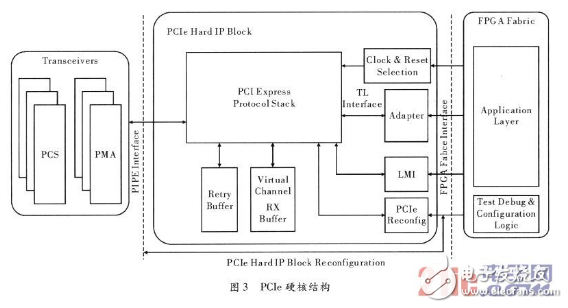

3.1 PCIe IP核結(jié)構(gòu)

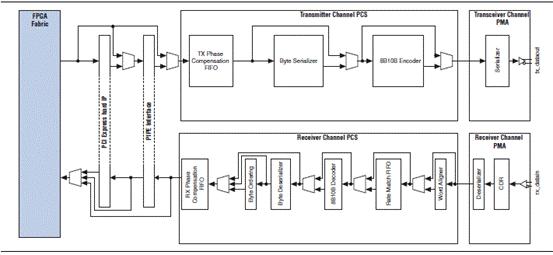

Altera的PCIe硬核IP包含處理層,鏈路層和物理層所要求的全部功能,以及大多數(shù)的可選功能。只需在IPCompiler中經(jīng)過簡單的參數(shù)設(shè)置即可生成全功能的IP模塊,如果是作為端點(diǎn)設(shè)備,可以使用Avalon-ST接口或Avalon—MM接口適配器,將應(yīng)用層映射為處理層的TLP。Avalon—ST適配層將應(yīng)用層的Avalon—ST接口映射到PCIe處理層的TLPs。

3.2 應(yīng)用層設(shè)計(jì)

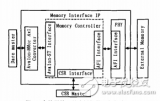

圖4左側(cè)是應(yīng)用層的方案圖,主要包含配置模塊、硬核IP模塊、時(shí)鐘管理模塊、DMA讀寫控制與仲裁模塊、任務(wù)驅(qū)動模塊等5部分。

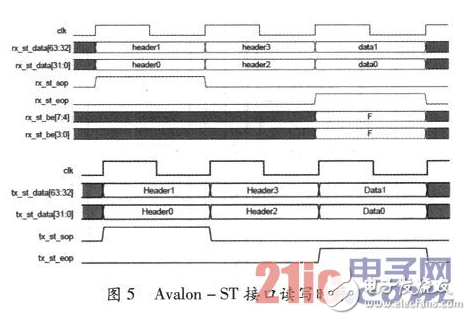

設(shè)計(jì)采用64位Agalon—ST接口,這樣供應(yīng)用的層使用的時(shí)鐘pld_clk與內(nèi)核時(shí)鐘同頻。TLPs分為Header、PayLoad和ECRC 3部分。其中TLP的數(shù)據(jù)包頭指出了數(shù)據(jù)包的類型,路由方式,有效載荷長度,目標(biāo)地址,設(shè)備ID,功能ID,總線ID等內(nèi)容,而數(shù)據(jù)包后還可生成與校驗(yàn)有關(guān)的ECRC信息,這些特征均有助于增強(qiáng)傳輸過程中數(shù)據(jù)的完整性與可靠性。圖5是一個(gè)以4雙字長度為例的數(shù)據(jù)接收的時(shí)序圖,其中rx_st_data和tx_st_data表示64位寬度的讀寫數(shù)據(jù)端口,rx_st_sop和tx_st_sop表示數(shù)據(jù)包起始標(biāo)志,rx_st_eop和tx_st_eop表示數(shù)據(jù)包結(jié)束標(biāo)志。應(yīng)用層可根據(jù)這些數(shù)據(jù)和標(biāo)志位實(shí)現(xiàn)TLP接收與發(fā)送同步。

設(shè)計(jì)中還包括鏈?zhǔn)紻MA,用于FPGA外部存儲與系統(tǒng)存儲器的數(shù)據(jù)傳輸。通過DMA訪問外部存儲器的最大優(yōu)勢在于,CPU配置完DMA狀態(tài)機(jī)后可繼續(xù)執(zhí)行其他指令操作,然后DMA狀態(tài)機(jī)會通過請求PCIe總線中斷的方式來完成數(shù)據(jù)傳輸。在用DMA時(shí)需要設(shè)置兩個(gè)基址BAR2和BAR3最小為256 Byte。DMA主要分為讀操作、寫操作以及仲裁3部分。初始條件下,DMA處于復(fù)位狀態(tài),通過讀取DMA信息標(biāo)示符來判斷當(dāng)前是否處于空閑狀態(tài),并從FPGA內(nèi)部讀取DMA控制信息,并相應(yīng)的進(jìn)入讀操作或?qū)懖僮鳌R訡PU寫FPGA外部存儲器為例,CPU通過PCIe總線寫B(tài)AR0地址數(shù)據(jù)來配置并開啟DMA Engine。FPGA將發(fā)出對CPU的DMA讀請求,然后等待CPU發(fā)送DMA數(shù)據(jù)。此時(shí)DMA Engine處于WAIT_FOR_DATA狀態(tài),等待來自PCIe接口的DMA數(shù)據(jù)包。同樣,CPU讀FPGA外部存儲器時(shí),F(xiàn)PGA將發(fā)出對CPU的DMA寫請求,并當(dāng)DMA完成讀操作后,等待PCIe接口發(fā)送DMA數(shù)據(jù)包,并由中斷標(biāo)志位判斷是否開啟PCIe中斷。狀態(tài)轉(zhuǎn)移如圖6所示。

在端點(diǎn)存儲器方面,2片16位的DDR2 SDRAM并接構(gòu)成一個(gè)32位的FPGA片外存儲器,并根據(jù)DDR2SDRAM芯片手冊在Altmemphy向?qū)е信渲煤孟嚓P(guān)時(shí)序與延遲參數(shù),即可生成DDR2 SDRAM控制器。在做電路圖設(shè)計(jì)時(shí),由于引腳驅(qū)動能力的問題,關(guān)鍵是FPGA對DDR2 SDRAM的引腳在連續(xù)的區(qū)域內(nèi)不能超過一定數(shù)量,最好能約束引腳區(qū)域,全編譯一遍后由軟件自由分配,再由人工作適當(dāng)調(diào)整,直到?jīng)]有嚴(yán)重警告。

3.3 數(shù)據(jù)收發(fā)仿真測試

當(dāng)用PCIe IP Compiler創(chuàng)建一個(gè)PCIe的硬核IP時(shí),會生成一個(gè)用戶可修改的測試文件頂層以及根聯(lián)合體模型。這樣就對測試應(yīng)用層接口功能提供了一個(gè)簡單的途徑,只需在測試文件中做一個(gè)模塊例化,即可構(gòu)建一個(gè)簡單的PCIe系統(tǒng)測試平臺。

如上共15個(gè)寄存器,其中tl_cfg_add和tl_cfg_ctl分別表示要更新的寄存器地址和對應(yīng)的寄存器數(shù)據(jù),tl_cfg_sts是配置的狀態(tài)。利用tl_cfg_ctl_wr和tl_cfg_sts_wr的跳變邊沿,由此可知對應(yīng)寄存器的內(nèi)容已發(fā)生更新,以此來確定數(shù)據(jù)的安全采樣時(shí)機(jī)。

如上信號tx_st_sop0的跳變啟動了一個(gè)TLP數(shù)據(jù)包的開始。應(yīng)用層參考tx_stream_read0信號開始往數(shù)據(jù)端口寫入數(shù)據(jù),其中前兩個(gè)數(shù)據(jù)是TLP的包頭。分解成雙字格式為:0x40000020,0x010800ff,0x000001880和0x00000000。即這是一個(gè)32位地址的寫存儲器TLP,數(shù)據(jù)長度為32雙字。當(dāng)tx_stream_read0變?yōu)榈碗娖?個(gè)周期后應(yīng)停止寫入數(shù)據(jù),直到tx_stream_read0再次變?yōu)楦唠娖?個(gè)周期后可繼續(xù)寫入數(shù)據(jù)。

如上信號rx_st_sop0出現(xiàn)高電平表明一個(gè)TLP數(shù)據(jù)包的開始。rx_st_data0的前兩個(gè)數(shù)據(jù)是TLP的數(shù)據(jù)包頭,分解為雙字后是:0x4a000020,0x00000080,0x01080270和0x000 00000。由這些包頭信息可知這是—個(gè)帶數(shù)據(jù)的完成TLP,完成者ID是0x0000,請求者ID是0x0108。且其后含有32個(gè)雙字的數(shù)據(jù),第一個(gè)雙字是0xaaa00001,第二個(gè)雙字是0xaaa 0002,直到0xaaa0020。rx_st_eop0在最后一個(gè)數(shù)據(jù)0xaaa0020aaa001f出現(xiàn)時(shí)發(fā)生跳變,表明TLP數(shù)據(jù)包結(jié)束。

4 結(jié)束語

仿真結(jié)果表明,使用Altera Cyclone IV GX系列FPGA搭建的PCIe接口能夠方便地實(shí)現(xiàn)高速數(shù)據(jù)傳輸應(yīng)用。隨著器件的發(fā)展和IP核的開發(fā),多通道的PCIe總線技術(shù)將會迅速發(fā)展,并對大數(shù)據(jù)、高速數(shù)據(jù)提供安全可靠的傳輸管道。

電子發(fā)燒友App

電子發(fā)燒友App

評論