VHDL是一種應用廣泛的硬件描述語言,設計者可以通過它編寫代碼,通過模擬器仿真驗證其功能,完成邏輯綜合與邏輯優化,最后通過下載到相應的可編程邏輯器件(如FPGA)中來實現設計。本設計是利用Quartus II軟件,采用VHDL語言設計一個用8個開關對應8個數字顯示。按sw0到sw7可以顯示1到8的數值,并在選擇開關時發出聲響。完成后下載到實驗箱,實現設計功能。

1、Quartus II簡介

Max+plus II 作為Altera的上一代PLD設計軟件,由于其出色的易用性而得到了廣泛的應用。目前Altera已經停止了對Max+plus II 的更新支持。Quartus II 是Altera公司繼Max+plus II之后開發的一種針對其公司生產的系列CPLD/PGFA器件的綜合性開發軟件,它的版本不斷升級,從4.0版到10.0版,該軟件有如下幾個顯著的特點:

1)Quartus II 的優點

該軟件界面友好,使用便捷,功能強大,是一個完全集成化的可編程邏輯設計環境,是先進的EDA工具軟件。該軟件具有開放性、與結構無關、多平臺、完全集成化、豐富的設計庫、模塊化工具等特點,支持原理圖、VHDL、VerilogHDL以及AHDL(Altera Hardware Description Language)等多種設計輸入形式,內嵌自有的綜合器以及仿真器,可以完成從設計輸入到硬件配置的完整PLD設計流程。

Quartus II可以在XP、Linux以及Unix上使用,除了可以使用Tcl腳本完成設計流程外,提供了完善的用戶圖形界面設計方式。具有運行速度快,界面統一,功能集中,易學易用等特點。

2)Quartus II對器件的支持

Quartus II支持Altera公司的MAX 3000A系列、MAX 7000系列、MAX 9000系列、ACEX 1K系列、APEX 20K系列、APEX II系列、FLEX 6000系列、FLEX 10K系列,支持MAX7000/MAX3000等乘積項器件。支持MAX II CPLD系列、Cyclone系列、Cyclone II、Stratix II系列、Stratix GX系列等。支持IP核,包含了LPM/MegaFunction宏功能模塊庫,用戶可以充分利用成熟的模塊,簡化了設計的復雜性、加快了設計速度。此外,Quartus II 通過和DSP Builder工具與Matlab/Simulink相結合,可以方便地實現各種DSP應用系統;支持Altera的片上可編程系統(SOPC)開發,集系統級設計、嵌入式軟件開發、可編程邏輯設計于一體,是一種綜合性的開發平臺。

3)Quartus II對第三方EDA工具的支持

對第三方EDA工具的良好支持也使用戶可以在設計流程的各個階段使用熟悉的第三放EDA工具。

Altera的Quartus II可編程邏輯軟件屬于第四代PLD開發平臺。該平臺支持一個工作組環境下的設計要求,其中包括支持基于Internet的協作設計。Quartus平臺與Cadence、ExemplarLogic、 MentorGraphics、Synopsys和Synplicity等EDA供應商的開發工具相兼容。改進了軟件的LogicLock模塊設計功能,增添 了FastFit編譯選項,推進了網絡編輯性能,而且提升了調試能力。

1.2、VHDL簡介

在傳統的硬件電路設計中,主要的設計文件是電路原理圖,而采用HDL設計系統硬件電路時主要使用HDL編寫源程序。所謂硬件描述語言HDL(HardwareDes cription Language),就是該語言可以描述硬件電路的功能,信號連接關系及定時關系。許多公司開發了自己專有的HDL,包括Zycad公司的ISP,Gateway DesignAutomation公司的Verilog以及Mentor Graphics公司的BLM。其中,Silicon Compiler公司的M及Gateway公司的Verilog以C語言為基礎。UDL/I在日本以標準HDL的形式出現。多年來設計者一直使用這些專用的HDL。1982年,各ASIC芯片廠商相繼開發了用于各自目的的HDL。1987年底,IEEE確認美國國防部開發的VHDL為標準硬件描述語言(IEEE.1076)。之后,各EDA公司研制的硬件電路設計工具逐漸向VHDL靠攏,VHDL在電子設計領域得到廣泛的接受,1993年,IEEE對VHDL進行了修訂,公布了新版本的VHDL(即IEEE.1076.1993)。現在,VHDL和Verilog作為IEEE的工業標準硬件描述語言,在電子工程領域,從各公司的設計人員到各大學的教授、學生,都極其重視對其的學習研究,VHDL已成為事實上的通用硬件描述語言。有專家認為,在21世紀中,幾乎全部的數字系統設計任務將由VHDL與Verilog語言承擔,VHDL將是電子工程設計人員的必備知識。VHDL和其他語言相比,最大的區別在于設計方法上的差別。

VHDL的主要優點有:

(1)VHDL支持自頂至下的和基于庫的設計方法,而且支持同步電路、異步電路、現場可編程門陣列器件FPGA(field programmable gate array)以及其他隨機電路的設計。VHDL具有比其他硬件描述語言更強的行為描述能力,基于抽象的行為描述風格避開了具體的器件結構,使設計人員能從邏輯行為上描述和設計大規模電子系統。目前流行的EDA工具和VHDL綜合器大都能實現行為描述到RTL(Register Transfer Level)描述的轉換。

(2)VHDL語句的行為描述能力和程序結構決定了它具有支持大規模設計的分解和已有設計再利用的功能,它支持系統的數學模型直到門級電路的描述,并且高層次的行為描述與低層次的門級電路描述、結構描述可以混合使用。這些特點符合IC設計的市場要求。VHDL支持系統級描述,這是它優于其他VHDL的最重要的特點。例如,Verilog語言是一種門級電路描述語言,其風格接近于電路原理圖,設計者需要搞清楚具體的電路結構的細節,因此工作量通常較大。VHDL語言卻最適合于描述電路的行為,即描述電路的功能,然后由綜合器來生成符合要求的電路網絡。設計者在熟悉基本單元電路的描述風格,積累一定的設計經驗后,就會為用VHDL設計同等性能電路的高效率所鼓舞。

(3)VHDL的硬件描述與具體的工藝技術和硬件結構無關,當門級或門級以上的描述通過仿真檢驗后,再利用相應的工具將設計映射成不同的工藝,因此電路的設計與工藝的改變是相互獨立的。彼此的改變不會產生不良影響,并且VHDL硬件描述語言的實現目標器件的選擇范圍廣泛,可使用各系列的CPLD、FPGA及各種門陣列器件。

(4)VHDL具有類屬描述語句和子程序調用等功能,對于己完成的設計源程序,可以通過修改類屬參數表和函數的辦法來改變設計的規模和結構。VHDL具有豐富的仿真語句和庫函數,使得門電路級的功能仿真、檢查成為可能,使設計者對整個工程設計的結構和功能的可行性做出決策。

(5)VHDL作為一種IEEE的工業標準,使VHDL的設計成果便于重復利用和交流。這就更進一步推動了VHDL語言的推廣及完善。另外,由于其語法嚴格,給閱讀和使用帶來極大的便利。

2、硬件設計

本設計硬件平臺采用武漢理工大學EDA實驗箱,如下圖所示。

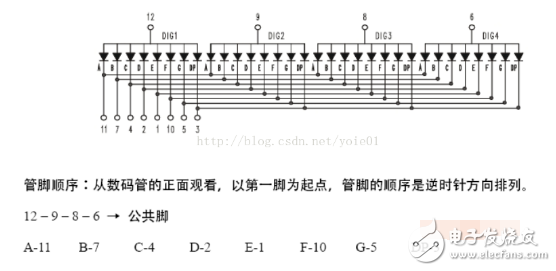

所用到的部分有LED數碼管、開關、蜂鳴器等,具體連接如下。

data_o[0] PIN_103 key[0] PIN_49

data_o[1] PIN_100 key[1] PIN_50

data_o[2] PIN_99 key[2] PIN_51

data_o[3] PIN_98 key[3] PIN_52

data_o[4] PIN_97 key[4] PIN_53

data_o[5] PIN_96 key[5] PIN_54

data_o[6] PIN_94 key[6] PIN_55

data_o[7] PIN_91 key[7] PIN_56

l[0] PIN_83 clk PIN_16

l[1] PIN_84 bell PIN_78

l[2] PIN_85

其中data_o[0]—data_o[7]為每個LED數碼管0-7的段選,key[0]—key[7]為控制開關0-7,l[0]—l[3]控制8個LED數碼管,clk為時鐘輸入,bell為蜂鳴器

3、軟件設計

3.1、設計方案

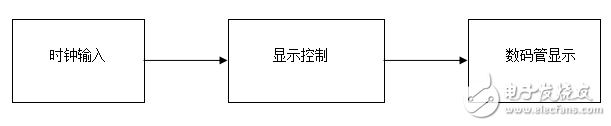

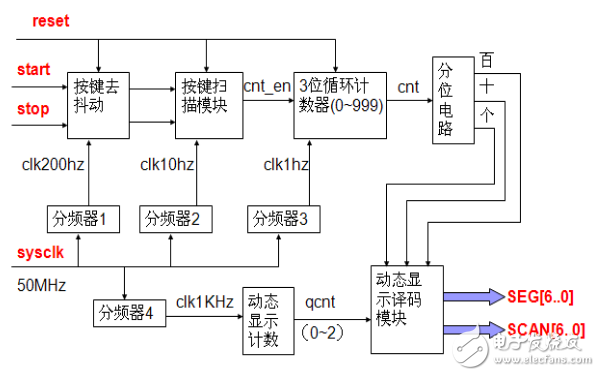

本設計的VHDL程序主要有共有3個部分:分頻、數碼管掃描進程、顯示控制進程。方案原理圖如下。

3.2、完整程序

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY key IS

PORT(clk : IN STD_LOGIC;

key : in std_logic_vector(7 downto 0);

l : out STD_LOGIC_VECTOR(2 downto 0);

data_o : out STD_LOGIC_VECTOR(7 downto 0);

bell : out STD_LOGIC:=‘0’

);

END key;

ARCHITECTURE an OF key IS

signal clk_1k : std_logic;

signal p : integer range 0 to 7;

begin

process(clk)

variable cnt1 : integer range 0 to 200;

variable cnt2 : integer range 0 to 125;

begin

if clk‘event and clk=’1‘ then

if cnt1=200 then

cnt1:=0;

if cnt2=125 then

cnt2:=0;

clk_1k《=not clk_1k;

else

cnt2:=cnt2+1;

end if;

else

cnt1:=cnt1+1;

end if;

end if;

end process;

process(p,clk_1k)

begin

if clk_1k=’1‘ and clk_1k’event then

if p=7 then

p《=0;

else

p《=p+1;

end if;

end if;

case p is

when 0 =》 l《=“000”;

when 1 =》 l《=“001”;

when 2 =》 l《=“010”;

when 3 =》 l《=“011”;

when 4 =》 l《=“100”;

when 5 =》 l《=“101”;

when 6 =》 l《=“110”;

when 7 =》 l《=“111”;

when others=》

end case;

end process;

process(clk_1k)

FUNCTION b_to_s7(bcd8421:INTEGER RANGE 0 TO 9) RETURN STD_LOGIC_VECTOR IS

VARIABLE smg7: STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

CASE bcd8421 IS

WHEN 0 =》 smg7:=“11111100”;

WHEN 1 =》 smg7:=“01100000”;

WHEN 2 =》 smg7:=“11011010”;

WHEN 3 =》 smg7:=“11110010”;

WHEN 4 =》 smg7:=“01100110”;

WHEN 5 =》 smg7:=“10110110”;

WHEN 6 =》 smg7:=“10111110”;

WHEN 7 =》 smg7:=“11100000”;

WHEN 8 =》 smg7:=“11111110”;

WHEN 9 =》 smg7:=“11110110”;

END CASE;

RETURN smg7;

END b_to_s7;

begin

if clk_1k=‘1’ then

case key is

when “11111111”=》bell《=‘0’;

when “11111110”=》 data_o《=b_to_s7(1);bell《=‘1’;

when “11111101”=》data_o《=b_to_s7(2);bell《=‘1’;

when “11111011”=》data_o《=b_to_s7(3);bell《=‘1’;

when “11110111”=》data_o《=b_to_s7(4);bell《=‘1’;

when “11101111”=》data_o《=b_to_s7(5);bell《=‘1’;

when “11011111”=》data_o《=b_to_s7(6);bell《=‘1’;

when “10111111”=》data_o《=b_to_s7(7);bell《=‘1’;

when “01111111”=》data_o《=b_to_s7(8);bell《=‘1’;

when others=》data_o《=“10001111”;bell《=‘1’;

end case;

end if;

end process;

end an;

4、實驗結果

所編寫程序經過下載到所用實驗箱后,當分別撥動開關sw0—sw7時,在LED數碼管上分別顯示數字1—8,并且蜂鳴器發出聲響,有關部分運行結果的如下圖所示。

電子發燒友App

電子發燒友App

評論