采用Spartan-6 FPGA加速紋理映射:這種要求嚴苛的圖形流程曾經(jīng)是定制ASIC內(nèi)核的應(yīng)用,而如今卻成為低成本FPGA的天下。

作為一種以 FPGA 為構(gòu)建基礎(chǔ),而非采用專業(yè)多媒體片上系統(tǒng)的手持設(shè)備,Milkymist One 無須計算機的輔助即能為聚會和音樂會提供視頻特效。在 Milkymist One 中,Spartan-6 FPGA 基本可實現(xiàn)系統(tǒng)的整個數(shù)字化部分。另外,F(xiàn)PGA 的強大功能還足以處理紋理映射,這種高端圖形功能代表了系統(tǒng)必須執(zhí)行的最密集的數(shù)據(jù)處理任務(wù)。在傳統(tǒng)上,紋理映射屬于 ASIC 圖形處理單元的領(lǐng)地,而在更早以前則是高端工作站的屬地。

新應(yīng)用領(lǐng)域的出色表現(xiàn)

無論是音樂節(jié)目主持人、綜藝節(jié)目主持人還是其他活動的組織者都能在音樂會、節(jié)日以及俱樂部中使用Milymist One(見圖1)營造出具有極強娛樂性的視頻效果。將攝像頭與視頻投影儀連接在一起,按下電源按鈕,數(shù)秒鐘后拍攝的一切就變成栩栩如生、似幻似真的光色效果。將攝像頭聚焦于舞臺上的舞者,指向參加聚會的人群乃至玩具或其他對象,讓觀眾為這種特效營造的效果如癡如醉。如果沒有攝像系統(tǒng)的加入,Milymist One可以單純地根據(jù)環(huán)境聲響生成效果,特別適用于希望能以交鑰匙解決方案實現(xiàn)簡單視覺效果的樂隊、俱樂部和聚會組織者。

該器件可支持來自多個源頭的輸入:MIDI鍵盤、USB計算機鍵盤、DMX桌面以及OpenSoundControl (OSC)客戶端。用戶甚至能夠使用智能手機與視覺效果無線地互動,只需要將一個WiFi路由器連接至以太網(wǎng)端口即可。另一個選擇是使用廣受青睞的 Arduino 電路板,利用其大量的傳感器界面來通過MIDI對Milymist One進行控制。

我們必須克服設(shè)計這種器件的重大挑戰(zhàn)。我們的處理算法要求將相當數(shù)量的計算功能和存儲器帶寬用于處理高幀率和低時延的視頻。另外,器件還必須與多種I/O協(xié)議實現(xiàn)接口相連。就本應(yīng)用而言,包含CPU和圖形加速功能的多媒體片上系統(tǒng)是許多工程師的首選。然后,他們會選用一些外部芯片來處理所有的接口。通過充分發(fā)揮賽靈思器件的功能和靈活性,我們能夠在單個Spartan-6 FPGA中實現(xiàn)我們系統(tǒng)幾乎全部的數(shù)字部分,從而既可以降低成本、精減芯片數(shù)量,又能夠顯著提升靈活性。

Milymist One的硬件

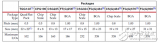

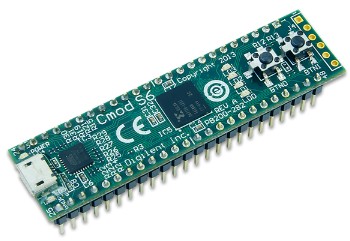

Milkymist One系統(tǒng)電路板的核心是一塊賽靈思XC6SLX45(見圖2)。該FPGA包含我們系統(tǒng)的所有數(shù)字邏輯,如軟核CPU、存儲器控制器、硬件加速器以及I/O外設(shè)等。

通過使用Spartan-6的“主BPI”模式,F(xiàn)PGA 可從NOR閃存芯片中讀取配置數(shù)據(jù)。該閃存芯片隨后使用“現(xiàn)場執(zhí)行 (execute-in-place)”方案運行引導載入程序,即一邊從NOR閃存獲取處理器指令,一邊對其進行執(zhí)行。引導載入程序隨后激活 SDRAM,并加載應(yīng)用軟件。該閃存芯片還負責存儲這類應(yīng)用軟件,并保留使用YAFFS2的用戶數(shù)據(jù)。YAFFS2 是一種可提供損耗均衡和日志功能的閃存優(yōu)化型文件系統(tǒng)。

我們的應(yīng)用軟件能夠從互聯(lián)網(wǎng)下載 FPGA 數(shù)據(jù)流更新,并將它們寫入閃存中。拜Spartan-6 FPGA所具有的多重載入 (MultiBoot)特性所賜,如果某個失效的更新會導致錯誤的數(shù)據(jù)流,則系統(tǒng)能夠進行失效保護。

與FPGA直接連接的一對DDR SDRAM芯片可提供128MB的系統(tǒng)存儲器。為有助于滿足該接口嚴格的時序要求,Spartan-6 FPGA可為其提供雙數(shù)據(jù)速率I/O寄存器、運行時間可編程延遲鎖相環(huán)(帶DCM)以及I/O延遲元件。

我們的器件可支持兩個全速的USB主機端口。FPGA在此處再一次負責提供大部分硬件。Spartan 6可直接驅(qū)動模擬收發(fā)器芯片,以便輕松將LVCMOS 3.3V電平轉(zhuǎn)換為能夠完美符合USB標準的信號。串行接口引擎和主控制器邏輯采用FPGA架構(gòu)實現(xiàn)。在原型設(shè)計階段,甚至能夠僅使用電阻和USB連接器與賽靈思ML401開發(fā)板的I/O擴展連接器相連,就能成功地將USB器件直接與FPGA相連。

在視頻輸出方面,F(xiàn)PGA可驅(qū)動一個3通道數(shù)模轉(zhuǎn)換器,以生成VGA端口的RGB分量。Spartan-6中包含的DCM CLKGEN原語具有高度的靈活性,能夠針對像素時鐘將多種不同頻率進行綜合,從而使器件能夠支持大量的視頻模式。

此外,如何對由VGA端口輸出的復(fù)合視頻信號(CVBS)進行綜合也在研究中。市面上已經(jīng)有一些計算機圖形卡,能夠使用低成本的無源適配器將CVBC器件與VGA輸出相連接。不過,在一套采用FPGA的系統(tǒng)上生成原色分量也是完全可行的。我們僅需要使用數(shù)字信號處理技術(shù)實現(xiàn)CVBS信號發(fā)生器,然后將生成的數(shù)據(jù)送給VGA數(shù)模轉(zhuǎn)換器即可。這樣,我們的器件就能輕松地與音樂以及現(xiàn)場表演場地仍然大量使用的傳統(tǒng)視頻投影儀和視頻混合控制臺相連接。

我們的設(shè)計可將Spartan 6與一對RS485收發(fā)器相連接,為DMX512提供支持。該協(xié)議可用于進行舞臺上的燈光控制,能夠讓器件將周邊的燈光與可視效果進行同步。在此,整個DMX512信號發(fā)送系統(tǒng)也是采用FPGA來實現(xiàn)的,而外部組件基本都是模擬組件。

此外,為了能與常用的控制器和傳感器進行交互,我們的系統(tǒng)還支持MIDI。我們的設(shè)計實現(xiàn)與DMX512類似,只有模擬外部組件。我們還支持以太網(wǎng)(僅使用一顆PHY芯片)、音頻(通過通用的AC97編解碼器)以及PAL、SECAM和NTSC擊JJ式視頻輸入。

這些外設(shè)大多數(shù)都能從FPGA獲取時鐘,而FPGA則使用其數(shù)字時鐘管理器(DCM)從統(tǒng)一的50MHz時鐘源將必要的頻率進行綜合。我們的電路板上只有兩個額外的晶振,而且為進一步減少成本,正在考慮在將來的PCB版本中使用更多FPGA生成的時鐘將其更換。

何謂紋理映射?

在所有Milkymist器件的FPGA必須執(zhí)行的數(shù)據(jù)處理任務(wù)中,紋理映射是密集程度最高的。紋理映射是OpenGL及DirectX等已加速3D API的一種通用計算機圖形運算,通常用于在屏幕上繪制帶紋理的3D多邊形。此外,其還能扭曲圖像(見圖3),而且我們也常將其用于此目的。

通用的圖形處理單元在三角形上執(zhí)行紋理映射,并且將更加復(fù)雜的多邊形分解為一系列的三角形。輸入到算法中的是待填充的三角形3個頂點的2D位置(也可能是原始3D坐標的投影),以及這3個頂點的2D紋理坐標。之后,該算法再逐像素繪制有紋理的三角形,方法是為每個像素線性地內(nèi)插紋理坐標,然后復(fù)制這些坐標處的紋理像素(也稱為紋理元素)。

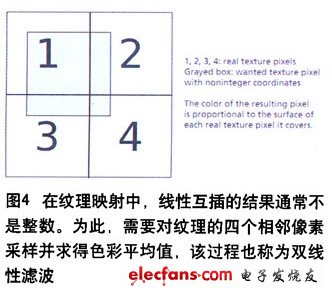

通過簡單地改變各頂點的位置或者每個頂點的紋理坐標的位置,紋理映射能夠?qū)崿F(xiàn)縮放、旋轉(zhuǎn)或者比例尺變化等圖像處理運算。但常見的問題是線性內(nèi)插的結(jié)果并非整數(shù),這就意味著應(yīng)該在四個相鄰的像素(見圖4)中對紋理進行采樣。在這種情況下,為了實現(xiàn)更理想的渲染,應(yīng)讀取四個像素,并將其色彩值進行平均(根據(jù)比例取不同的權(quán)重),這個流程被稱為雙線性濾波。我們的應(yīng)用需要雙線性濾波來實現(xiàn)理想的可視結(jié)果。

紋理映射,是一個計算強度大以及所需存儲器非常密集的進程,這從性能的角度即決定了軟件實現(xiàn)的不可行,在需要雙線性濾波的時候尤為如此。

FPGA實現(xiàn)

預(yù)計用于讀取幀緩沖器的存儲器延遲將成為性能制約因素。我們沒有采用高級預(yù)獲取技術(shù)等復(fù)雜且資源密集的技術(shù)來降低存儲延遲,而是簡單地采用直接映射的像素元素高速緩存,不僅簡單而且還能快速命中。另外,在設(shè)計紋理映射單元其余部分的時候,還需要注意讓存儲器讀取延遲成為唯一的制約因素。

采用這種高速緩存可實現(xiàn)高達90%的命中率,以每個周期命中一次,每9個周期失的一次計算,存儲器的平均存取時間為1.8個周期。采用80MHz的系統(tǒng)時鐘,則此類高速緩存的每秒吞吐能力為44M像素,足以滿足我們的應(yīng)用所需。

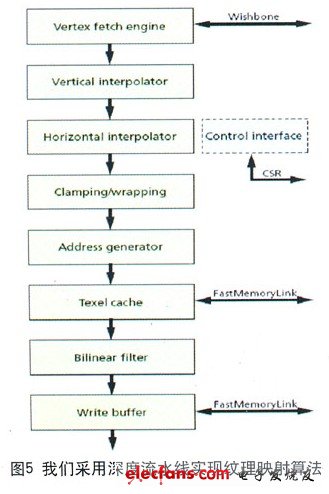

為確保存儲器存取時間是唯一的制約因素,我們在設(shè)計系統(tǒng)其余部分時,使之能夠支持每個時鐘周期大約一個輸出像素的處理能力。與之相對應(yīng),算法的實現(xiàn)以占用空間為主(硬件組件很少或者根本沒有基于時間的資源共享),但不要求復(fù)制資源密集的大型硬件單元。以空間為主的實現(xiàn)所用面積比時間共享的大,但更簡單明了,需要的多路復(fù)用器數(shù)量越少,也能夠更好地避免走線擁塞,從而更加簡便地實現(xiàn)FPGA的時序收斂。為此,我們?yōu)榧y理映射算法選擇了深度流水線實現(xiàn)。

流水線的頭幾級用于從存儲器中獲取低帶寬的頂點信息,然后使用某種Bresenham算法的變體計算內(nèi)插紋理坐標與目標坐標。我們通過采用行為Verilog HDL來實現(xiàn)這些級,隨后使用免費的XST綜合器(1SE WebPACK設(shè)計套件的組成部分)進行處理以生成經(jīng)優(yōu)化的網(wǎng)表。地址生成器能夠充分利用Spartan—6 FPGA的DSP48A1 Slice提供的硬件乘法器,高效率地計算與內(nèi)插坐標對應(yīng)的紋理幀緩沖器中的存儲器地址。XST綜合器能夠根據(jù)HDL源代碼中乘法運算符自動推導硬件乘法器,從而使其使用方法既簡單又方便。

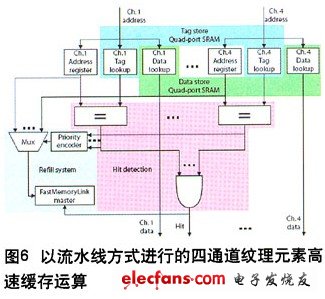

若要從存儲器中獲取紋理元素數(shù)據(jù),則會變得更加復(fù)雜。在每個時鐘周期,我們都需要從高速緩存中獲取4個不同的像素。準備4個不同的高速緩存沒有必要,因為雙線性濾波器的不同通道通常使用來自同一高速緩存線路的數(shù)據(jù)。因此我們需要一個4端口SRAM,但這看似在FPGA中比較困難。

幸運的是,Spartan-6 FPGA中真正的雙端口SRAM可提供理想的解決方案。我們通過使用兩個原始的雙端口SRAM復(fù)制數(shù)據(jù),以適當?shù)拇鷥r實現(xiàn)了4端口SRAM。在正常運行狀態(tài)下(命中),每個端口為一個通道服務(wù)。在失的后重新填充高速緩存的時候,讀取被禁用,而且可將兩個端口(每個原始雙端MSRAM各一個)用于將數(shù)據(jù)送給存儲器。

圖6是紋理元素高速緩存的簡化方框圖。在每個時鐘周期中,紋理元素高速緩存均以流水線的方式處理來自每個通道的存儲器地址。如果這些存儲器地址命中高速緩存,并且“命中”信號始終保持高電平,那么流水線就會一直運行。

如果發(fā)生失的,“命中”信號會轉(zhuǎn)為低電平(流水線停頓),隨即由優(yōu)先級編碼器和多路復(fù)用器(mux)選擇失的的地址之一(可以是1個,也可以是多個)。存儲器總線主系統(tǒng)發(fā)出一個存儲器交易事務(wù)以從系統(tǒng)存儲器中檢索數(shù)據(jù),然后替換高速緩存線路的內(nèi)容,并對標簽進行重寫。該地址現(xiàn)在變成命中高速緩存狀態(tài)。如果沒有其他地址未命中高速緩存,紋理元素高速緩存就已經(jīng)成功地處理該4通道交易事務(wù),而且“命中”信號會再次轉(zhuǎn)為高電平,以進行到下一個周期的處理。否則,該流程將重復(fù)進行,直到所有的地址都命中高速緩存為止。

可以看到,在現(xiàn)代FPGA中,只要將用于存儲的Block RAM的數(shù)量翻倍,同時輔以合理數(shù)量的控制邏輯,就能夠?qū)崿F(xiàn)理想的4端口高速緩存系統(tǒng)。

緊隨紋理元素高速緩存之后,雙線性濾波器將4個獲取到的紋理元素的結(jié)果混合在一起。在此,我們的設(shè)計再次充分發(fā)揮了Spartan 6中DSP48A1Slice的性能,能夠迅速計算出加權(quán)和。最后,可使用寫入緩沖器將結(jié)果存儲到基于SDRAM的系統(tǒng)存儲器中。

一旦與我們的軟核片上系統(tǒng)相集成后,我們的紋理映射單元就會僅使用低成本Spartan 6 FPGA的一小部分資源,卻能提供每秒7000萬像素的峰值填充速率以及每秒3700萬像素的平均填充速率。與純軟件相比,即便是與使用運行在高性能(及高能耗)ASIC CPU的軟件相比,性能也是一大飛躍,能夠充分滿足我們應(yīng)用的要求。

高度靈活的單芯片

采用高性能可重配置 FPGA,可在高度靈活的單芯片中將過去只有ASIC才能處理的繁重圖形處理功能與非常特定的I/O接口結(jié)合在一起。

Milkymist系統(tǒng)能夠充分利用Spartan 6 FPGA的眾多特性:I/O延遲組、DDR寄存器、大型真雙端口Block RAM、DSP Slice、靈活的DCM CLKGEN組件,能夠從NOR閃存進行配置以及多重引導功能。我們的完整設(shè)計僅使用了FPGA資源的大約一半,為將來的改良和特性預(yù)留了充裕的空間。這對成本像XC6SLX45這樣低的芯片來說是非常了不起的。

對于未來的功能改進而言,整個FPGA設(shè)計是屬于開源的,而且其許可和開發(fā)模式與Linux內(nèi)核一樣。設(shè)計人員能夠使用免費的ISE WebPACK設(shè)計軟件(同時提供Linux版和Windows版)重新構(gòu)建完整的比特流。

最后需要指出的是,該器件的總功耗不足5W,從而不僅充分凸現(xiàn)了以單芯片F(xiàn)PGA為核心的解決方案的又一優(yōu)勢所在,同時還進一步推翻了所有FPGA系統(tǒng)都是高功耗系統(tǒng)的錯誤認識。

電子發(fā)燒友App

電子發(fā)燒友App

評論