ADSP-TS201S - TigerSHARC-R Embedded Processor - Analog Devices

2022-11-04 17:22:44

ADSP-TS201SABP-050 245PCS現貨

2019-01-07 10:27:12

PCS.預計春節后3月份到貨。ADSP-TS201SAPBZ-060 在途400只+公司庫存285只=685PCS ADSP-TS201SAPBZ050 2404 PCS ADSP-TS201SABP-050 245 PCS ADSP-TS201SYBPZ050873 PCS

2018-12-21 19:48:14

端,最大系統時鐘是核時鐘的1/4。同時SCLK也為外部接口總線提供時鐘。ADSP一TS201內部有一個PLL,通過設置SCLKRATE2~0引腳將SCLK倍頻到所需的核時鐘。在設計過程中,為了保證時鐘

2019-04-12 07:00:11

{:12:}{:12:}{:12:}{:12:}{:12:}報道:ADSP-TS201誰用過

2012-09-19 14:14:35

用于多處理TigerSHARC系統的集群總線通信的詳細信號完整性和時序分析。該系統由8個ADSP-TS101S器件,一個主處理器和SDRAM組成,其集群總線運行頻率為100MHz。包括仿真結果和物理

2019-08-30 09:24:28

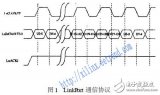

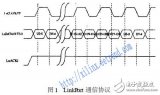

太多。而采用鏈路口通信不但能有效緩解DSP總線上的壓力,而且傳輸速度快,與FPGA之間的連線相對也少得多,故鏈路口方式更適合于FPGA與DSP之間進行實時數據通信。1 TS101和TS201的鏈路口分析

2019-06-21 05:00:07

在使用StratixII90的FPGA與TS201進行數據通信時,FPGA向TS201發送數據,link時鐘為384MHz,之前已經做了幾十塊板卡,低溫測試通過,最近做的幾個板卡,高溫和常溫試驗都

2014-11-04 15:18:49

在使用StratixII90的FPGA與TS201進行數據通信時,FPGA向TS201發送數據,link時鐘為384MHz,之前已經做了幾十塊板卡,低溫測試通過,最近做的幾個板卡,高溫和常溫試驗都

2014-11-04 15:20:49

TS201與TS101的性能比較,但沒有針對兩者的鏈路口進行詳細介紹,本文對兩者的鏈路口進行了細致的分析和比較。文獻[4]所設計的采集系統中,DSP與FGA的通信僅限于FPGA發、TS101收的單工通信

2018-12-04 10:39:29

TS201與TS101的性能比較,但沒有針對兩者的鏈路口進行詳細介紹,本文對兩者的鏈路口進行了細致的分析和比較。文獻[4]所設計的采集系統中,DSP與FGA的通信僅限于FPGA發、TS101收的單工通信

2019-06-19 05:00:08

)來通知接收準備好和數據塊傳輸結束。 采用FPGA與DSP通過鏈路口通信的關鍵是令雙方通信的握手信號達成協議,促使數據傳輸的進行。實際上,如果考慮TS201的LVDS信號形式已經被轉換完畢,則

2019-06-21 05:00:04

TS201 link口傳輸數據,一個link口為發送,一個link口為接收,link口和相關DMA配置和初始化完成后,在主函數當中收發一直運行,目前只發送4個unsigned int型數據,link口的傳輸是按照4字傳輸,現在接收不到數據,用示波器觀察LACKO信號一直為低電平。

2024-01-11 07:13:23

您好!我按照adi官網的ts201開發板的電路設計復制相關電路,選著的EPROM的啟動模式。但是程序燒寫進去后,斷電重啟一直無法加載程序。經過測試發現,正常情況下TS201的bms引腳在啟動后一段

2024-01-11 07:02:02

TS201的核電壓1。05V,I/O電壓2.5V,DRAM電壓1.5V的上電順序應該誰先誰后啊?如果兩個電壓間隔幾十ms建立可不可以?

我現在調整電壓上電順序,會導致DSP不加載程序。

2024-01-09 08:18:32

如題,我電腦已多次正確安裝并激活visual dsp++5.0程序,但是將ts201仿真器插入u***時,顯示未找到驅動程序,請問怎么辦

2019-01-10 14:45:39

ADI TS201的RS422串口通信 和與SDRAM讀寫的程序交流

2018-10-30 09:18:47

KIT LITE EVAL FOR ADSP-TS201S

2023-03-22 19:55:59

與Flash接口設計ADSP-TS201是ADI公司的TigerSHARC系列處理器的一種器件,其內核工作頻率可高達600 MHz,指令周期為1.6 ns,片內存儲器

2008-10-07 11:01:37

。 LTC2208IUP#PBF公司備貨2000 PCS.預計春節后3月份到貨。ADSP-TS201SAPBZ-060 在途400只+公司庫存285只=685PCS ADSP-TS201SAPBZ050 2404 PCS

2019-02-13 10:39:34

交流下ADSP TS201的RS422串口通信,EMIF的SDRAM,沒思路啊

2018-10-30 09:57:11

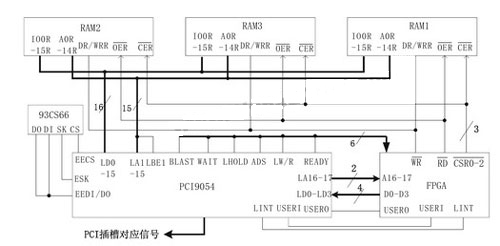

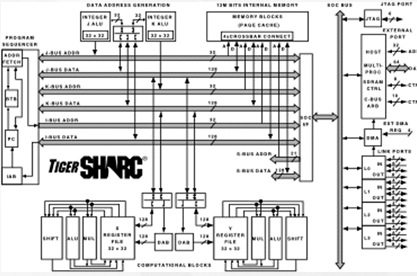

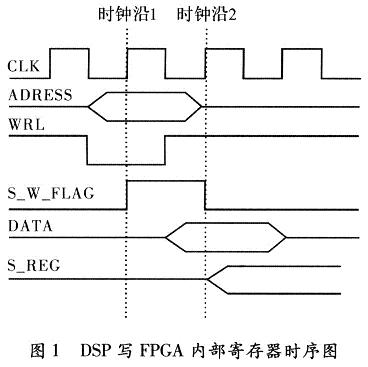

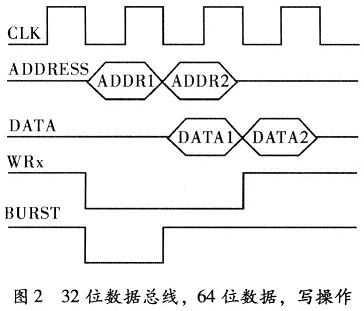

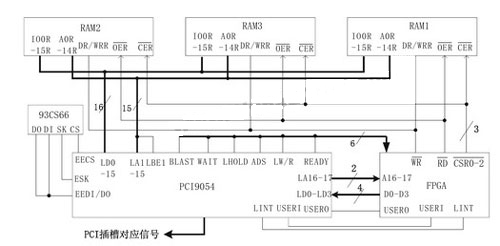

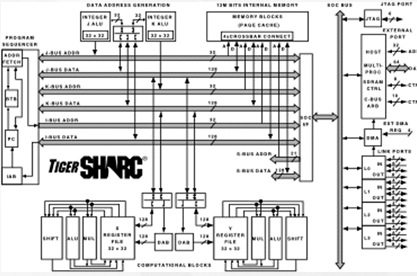

本文主要結合ADI公司的高性能ADSP-TS201的結構特點,討論了在系統設計的過程中應該重點注意的幾個問題和ADSP-TS201的外部接口技術,并給出了其與SDRAM,FPGA的連接實例,對基于TigerSHARC系列DSP的應用設計具有實用的參考價值。

2021-05-27 06:59:04

總線)。因此,由多ADSP- TS201 S組成的DSP并行處理系統從數據傳輸方式來看,不外乎有以下三種模型:高速鏈路口(LINK)耦合模型;高速外部總線口(簇總線)耦合模型;高速鏈路口 (LINK

2019-05-21 05:00:19

基于FPGA的PCI總線接口設計

2020-03-15 11:43:10

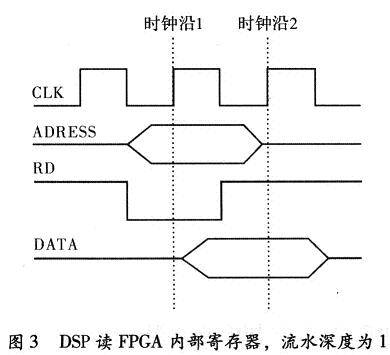

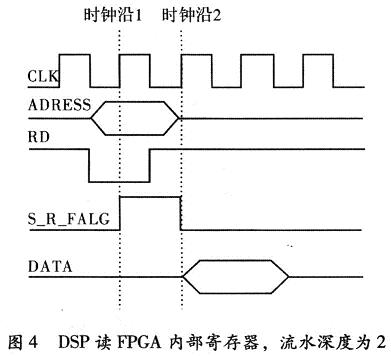

什么是DSP流水線協議?如何利用FPGA與ADSP TS201去設計總線接口?

2021-04-28 06:31:06

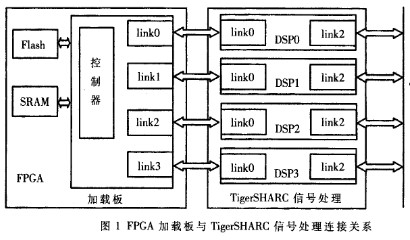

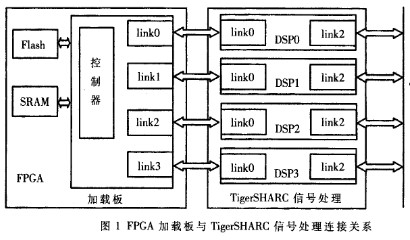

在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛。那么,我們該怎么利用FPGA與ADSP TS201設計總線接口呢?

2019-08-09 06:56:11

PCI總線是什么?有什么特點?如何利用FPGA去設計PCI總線的接口電路?設計PCI總線接口時應注意哪些問題?

2021-05-31 06:37:24

什么是PCI總線?它有什么特點?如何利用FPGA設計PCI總線的接口電路?設計PCI總線接口時應注意哪些問題?

2021-04-29 06:10:31

如題,我電腦已多次正確安裝并激活visual dsp++5.0程序,但是將ts201仿真器插入usb時,顯示未找到驅動程序,請問怎么辦

2024-01-12 06:00:28

您好!我按照adi官網的ts201開發板的電路設計復制相關電路,選著的EPROM的啟動模式。但是程序燒寫進去后,斷電重啟一直無法加載程序。經過測試發現,正常情況下TS201的bms引腳在啟動后一段

2018-08-01 07:58:17

ADSP-TS201的鏈路口程序應怎么寫啊,毫無頭緒啊,寄存器也看不懂,ADI公司沒找到參考的鏈路口程序啊

2018-12-10 09:17:06

你好,我用的是TS201,現在沒有板子,只是在仿真下,建立一個工程,驗證某個算法。我在程序中定義了一個 數組 float zzz[36000],編譯后,它提示下面的錯誤out of memory

2018-10-19 09:44:09

TS201的核電壓1。05V,I/O電壓2.5V,DRAM電壓1.5V的上電順序應該誰先誰后啊?如果兩個電壓間隔幾十ms建立可不可以?我現在調整電壓上電順序,會導致DSP不加載程序。

2019-03-08 08:04:56

介紹了一種基于CPCI總線并采用TS201,stratix和GA3816作為系統信號的高速信號處理平臺。同時簡單介紹了GA3816芯片的一些特點,詳細說明了該信號處理系統的結構和功能,給出了系統

2009-03-07 10:01:32 4

4 基于FPGA的PCI總線接口設計::PCI是一種高性能的局部總線規范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接

2009-06-25 08:17:18 48

48 在機載SAR 的實時成像處理器中,回波信號方位向帶寬以及方位向采樣率不能很好的滿足成像處理的要求,本文選擇ADSP-TS201 處理器芯片對回波信號在成像之前對其進行方位向預處

2009-08-05 09:45:52 18

18 ADSP-TS101 是ADI 公司新一代高性能浮點DSP,開始應用在高速數據采集和處理系統中。TS101 外部總線接口可編程,方便和各種總線外設接口。本文結合TS101 與同步FIFO、SDRAM 和FPGA 的接

2009-08-11 09:49:31 28

28 本文采用 altera 公司cyclone 系列芯片ep1c12 實現了與ts101/ts201 兩種芯片的鏈路口的雙工通信,并給出了具體的設計實現方法。其中ts101 的設計已經成功應用于某信號處理機中。

2009-12-03 16:32:07 18

18 為滿足復雜信號處理的實時性要求,通過對高速數字信號處理器TS201 的系統結構及其軟件開發過程的研究,在TS201 EZ-KIT 板上實現了自適應旁瓣對消(ASLC)處理,結果表明了TS201 數字

2010-01-07 12:01:33 24

24 本文提出了一種基于TS201的高速數據記錄儀,能將雷達模擬信號轉換成的數字信號經過處理后實時的按FAT32文件系統存儲到固態盤中去。采用DSP+FPGA的硬件架構,FPGA作為接口處理單元,DSP

2010-07-15 16:42:10 23

23 描述ADSP-TS201S是TigerSHARC處理器系列中的最新款器件之一。ADI公司的TigerSHARC處理器面向眾多依靠多個處理器共同工作來執行計算密集型實時功能的信號處理應用,非常適合

2024-01-26 11:33:09

隨著技術的發展, 往往需要在不同的系統之間實現高速通信, 現介紹了一種基于LVDS的高速數據傳輸的接口LinkPort , 給出了在Xilinx 的FPGA 中實現該接口的原理以及關鍵設計, 并成功

2010-09-22 08:26:14 98

98 軍事領域常選擇ADI公司的TS201芯片用于信號處理平臺,但由于其采用基于電路交換的LINK口進行連接,難以實現軍方對電子系統設計提出的可重構性的需求。FPGA可以用來實現接口轉換

2010-10-15 09:31:25 12

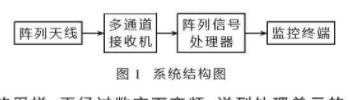

12 介紹了一種基于ADSP-TS201的無線電測向系統。給出了系統的總體結構和工作原理,研究了MUSIC測向算法及基于零點預處理的波束合成算法,介紹了DSP模塊的設計思想和程序流程圖。實

2010-11-22 14:52:42 39

39 采用ADSP-TS201S芯片的圖像采集處理系統

隨著人們對實時信號處理要求的不斷提高和大規模集成電路的迅速發展,作為數字信號處理核心和標志的數字

2009-03-30 12:19:18 1162

1162

摘 要 :PCI是一種高性能的局部總線規范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接口的

2009-06-20 13:13:28 936

936

應用領域: 6U VME TigerSHARC201FPGA信號處理機主要面向雷達、聲納、通信、圖象處理等高速信號處理領域。采用專用DSP與FPGA可編程邏輯器組成陣列化并行處理機,已經越來越成為當前數字信號處理發展的趨勢。 雷航科技的6U VME TigerSHARC201FPGA信號處理機就

2011-02-28 12:05:32 64

64 為了解決 雷達信號處理 中的高速運算, 大容量存儲和高速數據傳輸的問題, 提出采用 TS201 芯片實現雷達信號處理機設計, 利用其超高性能的處理能力和易于構造多處理并行系統的特

2011-07-20 17:20:13 65

65 數字信號處理器DSP是一種具有特殊結構的微處理器,它專門為實現數字信號處理的各種算法而設計,因而在硬件結構上具有特殊性。TS201是ADI公司TigerSHARC系列中集成了定點和浮點計算功

2011-09-21 11:59:38 1964

1964 設計并實現了一種基于ADSP TS201的組網雷達數據融合實時處理系統。主要闡述了雙ADSP TS201并行處理系統的結構、算法量的估計與結果分析。系統可滿足集中式組網融合和分布式組網融合

2011-10-09 10:49:40 30

30 2015-10-16 16:00:35 0

0 基于ADSP_TS201S的多DSP并行系統設計

2015-12-29 17:33:04 22

22 TS201的實時圖像處理系統鏈路口通信設計

2017-08-31 15:10:19 10

10 大規模集成電路技術的發展,作為數字信號處理的核心數字信號處理器(DSP)得到了快速的發展和應用。ADSP-TS201DSP是美國模擬器件(ADD公司繼TSl01之后推出的一款高性能處理器。此系列DSP性價比很高,兼有FPGA和ASIC信號處理性能和指令集處理器的高

2017-10-20 15:01:32 0

0 共享與鏈路口混合耦合的多DSP并行處理系統方案。在設計中,利用FPGA實現數據傳輸和CPCI接口的邏輯控制。經驗證,該系統具有運算能力強、片間通信靈活、并行處理效率高等優點。 關鍵詞:多DSP并行系統;ADSP-TS201S;FPGA;CPCI接口 0 引言 在寬帶雷達信號處理中,存在諸如回波

2017-10-31 16:41:04 0

0 。LVDS差分信號技術降低了對噪聲的關注。TS201 使用LinkPort 進行高速通信,解決了TS201 之間的通信瓶頸問題,但無法和需要高速通信的實時系統之間實現連接。FPGA 具有接口靈活,硬件設計軟件化的功能

2018-07-18 14:32:00 2537

2537

現代雷達信號處理已成為雷達功能實現的關鍵,本文根據某型雷達信號處理機的系統需要,對其硬件結構及軟件設計做了系統優化。設計了1套以4片 TS201和1片FPGA為核心信號處理板,該系統僅用l副板卡

2017-12-11 02:21:07 1881

1881

TigerSHARC系列處理器是ADI公司推出的高性能數字信號處理器,包含ADSP TS101、ADSP TS201、ADSP TS202、ADSP TS203。TigerSHARC系列處理器

2019-04-19 08:05:00 1943

1943

TS201是ADI公司繼ADSP-TS101之后又推出的新一代高性能Tiger-SHARC處理器,它集成了更大容量的存儲器,性價比很高。它兼有ASIC和FPGA的信號處理性能和指令集處理器的高度可編程性與靈活性,適用于高性能、大存儲量的信號處理和圖像應用。其特點如下:

2020-08-27 09:05:59 2258

2258

模擬器件公司(Analog Devices)推出的下一代TigerSHARC處理器ADSP-TS201,ADSP-TS-202和ADSP-TS203。它的每瓦DSP性能是最高的。

2021-01-11 12:01:00 1803

1803

MT-201:FPGA與ADC數字數據輸出的接口

2021-03-21 09:52:10 7

7 ADSP-TS201S Iba-DataFile BGA包(09/2003)

2021-04-12 16:09:33 10

10 ADSP-TS201S EZ-KIT精簡版?超級政府/超級政府手冊

2021-04-13 10:25:37 0

0 ADSP-TS201 EZ-KIT Lite電路板設計數據庫

2021-04-13 12:13:17 1

1 EE-201:ADSP-TS20x TigerSHARC?處理器片上SDRAM控制器

2021-04-13 18:00:50 6

6 EE-198:ADSP-TS201S TigerSHARC?處理器IBIS文件用戶指南

2021-04-13 18:10:30 8

8 ADSP-TS201S:TigerSHARC嵌入式處理器過時數據表

2021-04-15 18:45:56 6

6 EE-205:將代碼從ADSP-TS101S TigerSHARC?處理器移植到ADSP-TS201S TigerSHARC處理器的注意事項

2021-04-16 13:54:51 9

9 EE-283:采用ADSP-TS20x TigerSHARC?處理器的外部總線仲裁

2021-04-16 15:34:05 10

10 EE-170:評估ADSP-TS201S TigerSHARC?處理器的功耗

2021-04-21 10:41:30 6

6 EE-182:ADSP-TS201S TigerSHARC?處理器的散熱設計

2021-04-22 09:46:01 10

10 ADSP-TS201S EZ-KIT Lite評估系統手冊(3.0版,2007年1月)

2021-05-13 08:49:32 0

0 ADSP-TS201S EZ-KIT Lite評估系統手冊(2.0版,2005年1月)

2021-05-13 19:09:15 0

0 ADSP-TS201 TigerSHARC處理器編程參考

2021-05-18 09:21:19 1

1 ADSP-TS201 TigerSHARC處理器硬件參考

2021-05-18 15:46:19 1

1 ADSP-TS201S EZ-KIT精簡版?超級政府/超級政府手冊

2021-05-24 18:47:02 0

0 EE-218:為ADSP-TS201 TigerSHARC?處理器編寫高效浮點FFT

2021-05-26 09:17:20 5

5 ADSP-TS201S EZ-KIT Lite為開發人員提供一種經濟有效的方法,可以初步評估ADSP-TS201S TigerSHARC? 處理器和其多處理器能力。 該EZ-KIT Lite包括桌面

2021-06-09 08:59:50 4

4 ADSP-TS201S Iba數據文件BGA包(092003)

2021-06-16 12:02:33 2

2 ADSP-TS201S EZ-KIT Lite?手冊

2021-06-17 09:57:57 2

2 ADSP-TS201 EZ-KIT Lite電路板設計數據庫

2021-06-17 16:05:58 0

0 EE-201 ADSP-TS20x TigerSHARC?處理器片上SDRAM控制器

2021-06-18 10:47:01 4

4 EE-198 ADSP-TS201S TigerSHARC?處理器IBIS文件用戶指南

2021-06-18 11:13:33 2

2 電子發燒友網為你提供ADI(ti)TS201S-EZLITE相關產品參數、數據手冊,更有TS201S-EZLITE的引腳圖、接線圖、封裝手冊、中文資料、英文資料,TS201S-EZLITE真值表,TS201S-EZLITE管腳等資料,希望可以幫助到廣大的電子工程師們。

2021-09-02 12:00:02

電子發燒友網站提供《基于ADSP-TS201的著陸雷達恒虛警電路實現.pdf》資料免費下載

2023-10-23 09:59:21 0

0 電子發燒友網站提供《TigerSHARC? ADSP-TS201S處理器的散熱設計要點.pdf》資料免費下載

2023-11-29 11:12:01 0

0

電子發燒友App

電子發燒友App

評論