資料介紹

上海2013年10月24日電 /美通社/ -- 電子設(shè)計(jì)自動化技術(shù)的領(lǐng)導(dǎo)廠商 Mentor Graphics近日發(fā)布一份題為《轉(zhuǎn)向使用即插即用的分層 DFT 的好處》的研究報(bào)告。

一、背景

傳統(tǒng)的全芯片 ATPG 正日漸衰退,對于許多現(xiàn)有的和未來的集成芯片器件來說,一項(xiàng)主要挑戰(zhàn)就是如何為龐大數(shù)量的設(shè)計(jì)創(chuàng)建測試圖案。對于有百萬門甚至數(shù)億門的設(shè)計(jì),傳統(tǒng)上等到設(shè)計(jì)完成再創(chuàng)建測試圖案的方法是不切實(shí)際的,產(chǎn)生所有這些圖案需要龐大的計(jì)算能力和相當(dāng)多的時(shí)間。分層可測試性設(shè)計(jì)通過在區(qū)塊或內(nèi)核上完成了 DFT 插入和圖案生成解決了這個(gè)問題。這大大減少了圖案生成時(shí)間和所需的計(jì)算資源。它還能讓你在設(shè)計(jì)過程中提前完成大部分 DFT 和圖案生成,從而大幅提高可預(yù)測性并降低風(fēng)險(xiǎn)。本文將介紹分層 DFT 流程的:插入掃描包裝器 (Wrapper)、為內(nèi)核生成灰盒圖像,將內(nèi)核級圖案重定向到集成芯片頂層的簡單映射步驟。

二、為什么即插即用是合理的?

即插即用這種方法帶來的一個(gè)重要好處就是,在設(shè)計(jì)過程中你可以在內(nèi)核層面提前完成所有工作。這降低了許多類型的風(fēng)險(xiǎn),因?yàn)槿魏螁栴}都可以提前解決,讓最終芯片測試架構(gòu)和結(jié)果變得更可預(yù)見。在內(nèi)核層面做更多的測試工作還能讓各單獨(dú)的開發(fā)團(tuán)隊(duì)獨(dú)立工作,然后向做芯片集成工作的同事交付標(biāo)準(zhǔn)的 DFT 操作和測試圖案等數(shù)據(jù)。此外,一旦設(shè)計(jì)和圖案數(shù)據(jù)完成,同樣的數(shù)據(jù)可以被重新用于任何使用該內(nèi)核的芯片設(shè)計(jì)。即插即用方法同樣非常靈活。如果設(shè)計(jì)出現(xiàn)問題,需要進(jìn)行工程更改(ECO),那么只需要對進(jìn)行ECO的內(nèi)核重新生成測試圖案。

三、使用包裝器鏈打造獨(dú)立內(nèi)核

分層和內(nèi)核的即插即用方法的基本要求之一是,確保每個(gè)內(nèi)核可以獨(dú)立進(jìn)行測試。DFT 工具可以從內(nèi)核IO開始,并橫穿內(nèi)核邏輯直到找到第一個(gè)寄存器,然后將其包括在包裝器鏈中。這些單元由于同時(shí)執(zhí)行功能性任務(wù)和測試任務(wù),因而被稱為共享包裝器單元。許多設(shè)計(jì)包含寄存器IO,這樣進(jìn)出內(nèi)核的信號的時(shí)序能得到很好地確定。這使包裝器插入變得非常簡單。

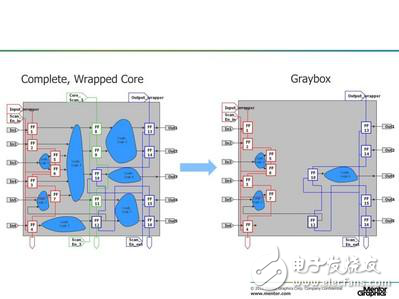

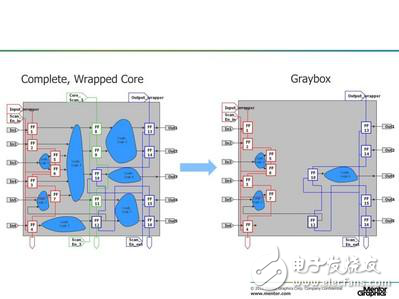

包裝器鏈同時(shí)還支持頂層IC建模和規(guī)則檢查。一旦包裝器鏈被插入,DFT 工具程序可以分析任何內(nèi)核,并找出IO和包裝器鏈之間存在什么樣的邏輯。利用該邏輯,內(nèi)核的部分圖像被寫出,我們稱之為灰盒(圖1)。灰盒被用來驗(yàn)證內(nèi)核在頂層的連接是否正確(設(shè)計(jì)規(guī)則檢查),同時(shí)也被用來創(chuàng)建各種內(nèi)核之間的簡單互連測試。

圖1:當(dāng)掃描鏈插入內(nèi)核,包裝器鏈的結(jié)構(gòu)允許將內(nèi)核隔離為一個(gè)完整的包裝器內(nèi)核,如左圖所示。右圖顯示了一個(gè)灰盒模型,其中頂層測試只需要內(nèi)核IO和包裝器鏈之間的邏輯。

圖1:當(dāng)掃描鏈插入內(nèi)核,包裝器鏈的結(jié)構(gòu)允許將內(nèi)核隔離為一個(gè)完整的包裝器內(nèi)核,如左圖所示。右圖顯示了一個(gè)灰盒模型,其中頂層測試只需要內(nèi)核IO和包裝器鏈之間的邏輯。

一、背景

傳統(tǒng)的全芯片 ATPG 正日漸衰退,對于許多現(xiàn)有的和未來的集成芯片器件來說,一項(xiàng)主要挑戰(zhàn)就是如何為龐大數(shù)量的設(shè)計(jì)創(chuàng)建測試圖案。對于有百萬門甚至數(shù)億門的設(shè)計(jì),傳統(tǒng)上等到設(shè)計(jì)完成再創(chuàng)建測試圖案的方法是不切實(shí)際的,產(chǎn)生所有這些圖案需要龐大的計(jì)算能力和相當(dāng)多的時(shí)間。分層可測試性設(shè)計(jì)通過在區(qū)塊或內(nèi)核上完成了 DFT 插入和圖案生成解決了這個(gè)問題。這大大減少了圖案生成時(shí)間和所需的計(jì)算資源。它還能讓你在設(shè)計(jì)過程中提前完成大部分 DFT 和圖案生成,從而大幅提高可預(yù)測性并降低風(fēng)險(xiǎn)。本文將介紹分層 DFT 流程的:插入掃描包裝器 (Wrapper)、為內(nèi)核生成灰盒圖像,將內(nèi)核級圖案重定向到集成芯片頂層的簡單映射步驟。

二、為什么即插即用是合理的?

即插即用這種方法帶來的一個(gè)重要好處就是,在設(shè)計(jì)過程中你可以在內(nèi)核層面提前完成所有工作。這降低了許多類型的風(fēng)險(xiǎn),因?yàn)槿魏螁栴}都可以提前解決,讓最終芯片測試架構(gòu)和結(jié)果變得更可預(yù)見。在內(nèi)核層面做更多的測試工作還能讓各單獨(dú)的開發(fā)團(tuán)隊(duì)獨(dú)立工作,然后向做芯片集成工作的同事交付標(biāo)準(zhǔn)的 DFT 操作和測試圖案等數(shù)據(jù)。此外,一旦設(shè)計(jì)和圖案數(shù)據(jù)完成,同樣的數(shù)據(jù)可以被重新用于任何使用該內(nèi)核的芯片設(shè)計(jì)。即插即用方法同樣非常靈活。如果設(shè)計(jì)出現(xiàn)問題,需要進(jìn)行工程更改(ECO),那么只需要對進(jìn)行ECO的內(nèi)核重新生成測試圖案。

三、使用包裝器鏈打造獨(dú)立內(nèi)核

分層和內(nèi)核的即插即用方法的基本要求之一是,確保每個(gè)內(nèi)核可以獨(dú)立進(jìn)行測試。DFT 工具可以從內(nèi)核IO開始,并橫穿內(nèi)核邏輯直到找到第一個(gè)寄存器,然后將其包括在包裝器鏈中。這些單元由于同時(shí)執(zhí)行功能性任務(wù)和測試任務(wù),因而被稱為共享包裝器單元。許多設(shè)計(jì)包含寄存器IO,這樣進(jìn)出內(nèi)核的信號的時(shí)序能得到很好地確定。這使包裝器插入變得非常簡單。

包裝器鏈同時(shí)還支持頂層IC建模和規(guī)則檢查。一旦包裝器鏈被插入,DFT 工具程序可以分析任何內(nèi)核,并找出IO和包裝器鏈之間存在什么樣的邏輯。利用該邏輯,內(nèi)核的部分圖像被寫出,我們稱之為灰盒(圖1)。灰盒被用來驗(yàn)證內(nèi)核在頂層的連接是否正確(設(shè)計(jì)規(guī)則檢查),同時(shí)也被用來創(chuàng)建各種內(nèi)核之間的簡單互連測試。

圖1:當(dāng)掃描鏈插入內(nèi)核,包裝器鏈的結(jié)構(gòu)允許將內(nèi)核隔離為一個(gè)完整的包裝器內(nèi)核,如左圖所示。右圖顯示了一個(gè)灰盒模型,其中頂層測試只需要內(nèi)核IO和包裝器鏈之間的邏輯。

圖1:當(dāng)掃描鏈插入內(nèi)核,包裝器鏈的結(jié)構(gòu)允許將內(nèi)核隔離為一個(gè)完整的包裝器內(nèi)核,如左圖所示。右圖顯示了一個(gè)灰盒模型,其中頂層測試只需要內(nèi)核IO和包裝器鏈之間的邏輯。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 可視化即插即用工具箱開源分享

- 電源系統(tǒng)設(shè)計(jì):非完全“即插即用”

- 價(jià)格最親民的TI DLP?Pico? display評估模塊,支持即插即用和顯示功能

- 索引即插即用主板REV000

- 索引即插即用主板REV001

- 90 W即插即用100米5e類電纜的以太網(wǎng)供電

- IT8661F即插即用超級AT IO芯片的用戶手冊免費(fèi)下載 2次下載

- 基于即插即用的智能變電站信息自動校核技術(shù) 0次下載

- 基于通用即插即用協(xié)議服務(wù)系統(tǒng)模型 0次下載

- Linux下即插即用設(shè)備的安裝 0次下載

- TE Connectivity 即插即用加速度傳感器7204A 0次下載

- TE Connectivity 即插即用加速度傳感器4807A 0次下載

- TE Connectivity 即插即用加速度傳感器 8811- 0次下載

- 基于轉(zhuǎn)換模塊的空間即插即用綜合電子系統(tǒng)研究 0次下載

- 一種新型即插即用智能記錄儀的研究與設(shè)計(jì)

- DFT設(shè)計(jì)—MBIST算法測試 5148次閱讀

- 即插即用型一體化盒式DC/DC電源解決方案 846次閱讀

- 即插即用!百度提出S3IM:用于NeRF提點(diǎn)的Magic Loss 766次閱讀

- Lightelligence使用Cadence Xcelium多核加速DFT仿真 1948次閱讀

- 如何通過即插即用數(shù)字輸入D類放大器實(shí)現(xiàn)卓越的音頻性能 1342次閱讀

- 分層單體架構(gòu)系統(tǒng)的風(fēng)格及其本質(zhì) 1398次閱讀

- 分層DFT技術(shù)如何實(shí)現(xiàn)在最大化SoC 1061次閱讀

- 如何使用DFT App進(jìn)行硬件加速仿真設(shè)計(jì) 2127次閱讀

- pcb分層原因 1.1w次閱讀

- PCB分層起泡失效案例分析 1w次閱讀

- EDA明導(dǎo)國際Calibre平臺已支持最新的TSMC 12FFC制程設(shè)計(jì) 2753次閱讀

- 如何使用 DFT App 進(jìn)行硬件仿真 3013次閱讀

- FFT太慢太死板?滑動DFT讓計(jì)算飛起來! 1w次閱讀

- 分層 DFT 流程及步驟介紹 1.1w次閱讀

- 詳細(xì)剖析OPC和即插即用技術(shù) 6093次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費(fèi)下載

- 0.00 MB | 1497次下載 | 免費(fèi)

- 2TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費(fèi)

- 3單片機(jī)典型實(shí)例介紹

- 18.19 MB | 103次下載 | 1 積分

- 4S7-200PLC編程實(shí)例詳細(xì)資料

- 1.17 MB | 28次下載 | 1 積分

- 5筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 6開關(guān)電源原理及各功能電路詳解

- 0.38 MB | 15次下載 | 免費(fèi)

- 79天練會電子電路識圖

- 5.91 MB | 6次下載 | 免費(fèi)

- 8100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234314次下載 | 免費(fèi)

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費(fèi)

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費(fèi)

- 4LabView 8.0 專業(yè)版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費(fèi)

- 5555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33564次下載 | 免費(fèi)

- 6接口電路圖大全

- 未知 | 30321次下載 | 免費(fèi)

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費(fèi)

- 8開關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21540次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537794次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234314次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191183次下載 | 免費(fèi)

- 7十天學(xué)會AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183278次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138039次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論