描述線性時不變離散時間系統(tǒng)的作用,所以將其替換成 z 變換進(jìn)行描述,則在分析求解過程中會更加的清晰。 關(guān)鍵詞:z變換,DFT,電阻網(wǎng)絡(luò) 01電阻網(wǎng)絡(luò) 一、問題來源 在網(wǎng)文 ?Infinite Ladder of 1Ω of Resistor[1]?中討論了如下無窮電阻網(wǎng)絡(luò)兩個相鄰節(jié)點之間的

2022-08-16 16:26:17 1764

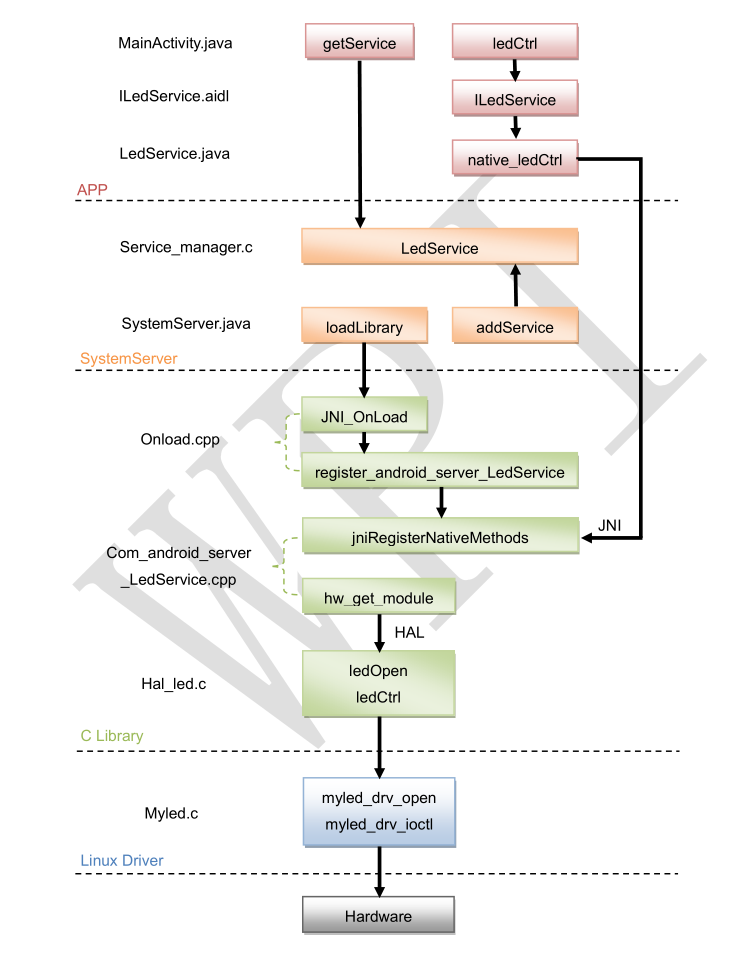

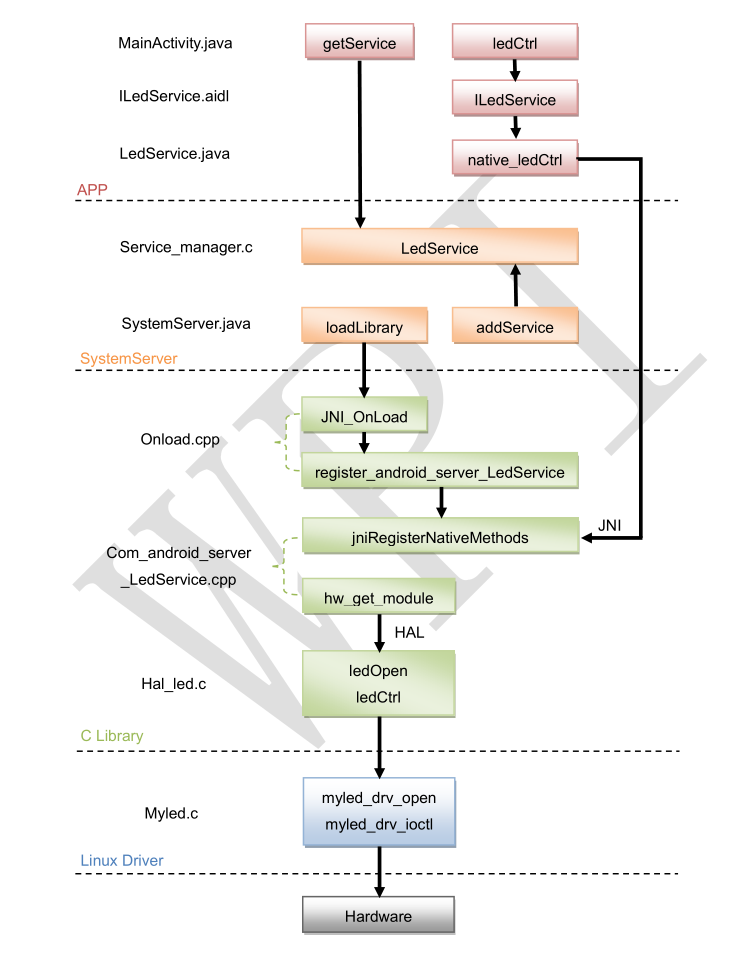

1764 本文我們要講的是在用 i.MX8 平臺開發(fā)時,Android APP 如何進(jìn)行訪問硬件驅(qū)動。

2023-12-04 13:50:10 379

379

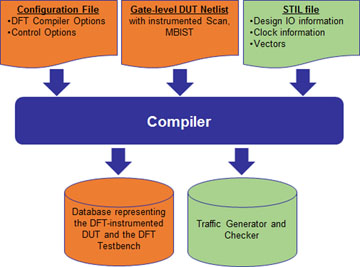

DFT:全稱是 Design for Test,可測性設(shè)計,通過在芯片原始設(shè)計中插入各種用于提高芯片可測試性(包括可控制性和可觀測性)的硬件邏輯,從而使芯片變得容易測試,大幅度節(jié)省芯片測試的成本

2021-07-23 07:28:32

最大以及測試時間最短。 圖1:一個典型的百萬門復(fù)雜ASIC設(shè)計,包含有內(nèi)核、嵌入式存儲器、專用邏輯和通信接口電路 如(圖1)所示的設(shè)計需要較早在宏觀上進(jìn)行考慮,以得出最優(yōu)DFT/BIST策略。比如

2011-12-15 09:53:14

設(shè)計中插入各種用于提高芯片可測試性(包括可控制性和可觀測性)的硬件邏輯,從而使芯片變得容易測試,大幅度節(jié)省芯片測試的成本。DFT工程師經(jīng)典教程書籍 [hide][/hide]

2012-01-11 14:33:22

DFT是什么?DFT在芯片設(shè)計領(lǐng)域的含義,即可測性設(shè)計(Design for Test), 可測試性設(shè)計(Design for Test,簡稱DFT)是電路和芯片設(shè)計的重要環(huán)節(jié),它通過在芯片原始

2012-01-11 14:28:06

期的要求。DFT運算速度遠(yuǎn)遠(yuǎn)低于FFT,但是,對樣本數(shù)沒有要求。基于變頻電量測量特殊性以及兩種算法的特點,湖南銀河電氣有限公司的WP4000變頻功率分析儀采用高性能的嵌入式微處理器,采用DFT算法進(jìn)行

2014-05-22 20:43:36

樓主應(yīng)推薦一些硬件仿真芯片sst89e516,以及仿真監(jiān)控softice,方便學(xué)習(xí)51內(nèi)核的便宜簡單仿真。使學(xué)習(xí)更生動。

2013-11-27 14:47:44

ATK-DAP仿真器 BURNER 5V

2023-03-28 13:05:53

ATK-HSDAP仿真器 BURNER

2023-03-28 13:05:52

DAP仿真器 BURNER

2023-03-28 13:06:20

KIT ANDROID OPEN ACCESSORY APP

2023-03-29 22:53:38

(x)為圖6中的縱坐標(biāo)值。 圖6 DFT-S-OFDM系統(tǒng)中,π/2-BPSK調(diào)制時,F(xiàn)DSS與不進(jìn)行FDSS的PAPR比較 從圖6的PAPR CCDF仿真結(jié)果可以看出,與不使用FDSS相比

2020-12-03 15:46:13

用Labview仿真出兩個硬件,可不可以進(jìn)行虛擬連線

2015-04-24 20:56:08

NLVSV1T34DFT2G

2023-03-29 16:27:51

The following is the Job Description of this position-- DFT Engineer. If someone is interested, plz feel

2016-07-15 13:58:30

ST-LINK仿真器 BURNER 5V

2023-03-28 13:06:38

STC8 進(jìn)行硬件仿真時,提示連接不上! USB轉(zhuǎn)TTL用的是PL2302!下載沒問題,主頻是24兆

2023-11-07 07:29:48

USB Blaster仿真器 BURNER 5V

2023-03-28 13:06:20

用于硬件仿真平臺的新型應(yīng)用程序,開辟了硬件仿真的新**。新型Veloce Apps包括Veloce Deterministic ICE、Veloce DFT和Veloce FastPath,可以

2016-04-15 16:25:55

stm32使用stlink進(jìn)行硬件仿真,具有很大的優(yōu)點,能夠?qū)崟r監(jiān)測到io電平,對于時序分析和debug具有很大幫助,而對于stc系列單片機,如果單純地使用軟件仿真,實際中仿真會很不方便,這就為尋求

2021-11-18 08:58:18

一個APP如何控制多個智能硬件,機智云告訴你其實只需要花三分鐘使用“綁定其他產(chǎn)品”即可實現(xiàn)。綁定其它產(chǎn)品的應(yīng)用是為了實現(xiàn)一個App可以控制多款產(chǎn)品的需求而必須進(jìn)行的操作。詳細(xì)說明在App開發(fā)

2018-03-20 10:33:44

【作者】:郭澤華;【來源】:《電聲技術(shù)》2010年02期【摘要】:DFT和MDCT是音頻編碼算法中應(yīng)用較多的2種時頻分析方法。給出了一種同時計算DFT系數(shù)和MDCT系數(shù)的算法,并對原理進(jìn)行了簡要分析

2010-04-23 11:13:23

什么是數(shù)字信號處理DFT?貌似有很多DFT啊

2011-12-15 09:39:26

最近在使用CCS3.3對C6414的BIOS做硬件仿真實驗,在simulator環(huán)境下是否可以通過pin connect來作為外部中斷輸入源,對硬件中斷進(jìn)行仿真。若可行,具體怎么操作。

另外,上述的這種情況是不是不能在simulator下仿真,必須在emulator下?

2018-06-24 02:45:23

我正在使用Xilinx 14.7在Virtex 5中進(jìn)行硬件協(xié)同仿真。我嘗試通過獲取源屬性來啟用硬件模擬。但我無法在源屬性中看到該選項。為什么會發(fā)生這種情況以及如何解決?

2020-03-12 06:27:08

基于FPGA的超高速FFT硬件實現(xiàn)介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達(dá)4 096點的大點數(shù)超高速FFT硬件系統(tǒng)設(shè)計與實現(xiàn)方法,當(dāng)多組大點數(shù)進(jìn)行FFT運算時,利用FPGA

2009-06-14 00:19:55

基于掃描的DFT方法掃描設(shè)計的基本原理是什么?掃描設(shè)計測試的實現(xiàn)過程是怎樣的?基于掃描的DFT對芯片測試的影響有哪些?

2021-05-06 09:56:36

如何使用KEIL進(jìn)行軟硬件仿真

2012-08-20 14:14:51

我想使用ML550板進(jìn)行硬件協(xié)同仿真(通過Mathworks Simulink / Sysgen)。 ML550不是Sysgen下拉菜單中的一個選擇。我認(rèn)為我需要安裝一個驅(qū)動程序 - 任何人都知道從哪里獲取它?

2019-08-29 10:32:14

如何利用DAGC技術(shù)去調(diào)整DFT的輸入功率?

2021-05-20 06:54:26

正在學(xué)習(xí)Real-Time DSP和圖像處理的內(nèi)容,遇到一個問題,如何能在Labview中實現(xiàn)二維DFT?我知道對于一個N*N的矩陣,進(jìn)行二維DFT時,實際上是先對該矩陣的每個列向量進(jìn)行DFT運算

2012-06-27 05:23:25

提高DFT設(shè)計測試覆蓋率的有效方法是什么

2021-05-07 06:37:41

急招DFT工程師,職位JD如下,有興趣簡歷請投遞1736253011@qq.comDFT工程師Responsibilities: 1. Participate in SoC level

2017-04-14 14:11:16

招聘三個人1、專做ic設(shè)計流程的高級工程師2、主要做pcie開發(fā)的高級工程師3、dft負(fù)責(zé)人,全模塊都負(fù)責(zé)過的高級工程師(ATPG,MBIST,SCAN 等)招聘2-5年的數(shù)字ic設(shè)計工程師3人,主要是RTL代碼編寫能力,再加上后期的仿真驗證求推薦,***@qq.com

2016-09-07 17:04:19

自己制作的Matlab DFT習(xí)題

2020-10-31 21:13:21

百分之百的覆蓋率。另外,結(jié)構(gòu)測試向量在DFT應(yīng)用過程中起著至關(guān)重要的作用,為了得到高效率的此類測試向量,需要在設(shè)計階段實現(xiàn)特定的輔助性設(shè)計;通過增加一定的硬件開銷,獲得最大可測試性。而此類的輔助性設(shè)計就包括掃描鏈

2016-05-25 15:32:58

DFT是什么原理?

2021-06-17 08:54:06

`其中的分辨率f△代進(jìn)去以后DFT表達(dá)式就變成了x[n]exp(-j2pi*n*k*fs/N),和DSP課本上的DFT公式不一樣啊,為什么和fs有關(guān)呢?`

2013-05-30 01:02:42

什么軟件可以進(jìn)行STM32的硬件仿真呢,就想proteus對單片機的仿真一樣

2014-12-29 19:38:16

性(包括可控制性和可觀測性)的硬件邏輯,從而使芯片變得容易測試,大幅度節(jié)省芯片測試的成本。超完善的DFT學(xué)習(xí)資料[hide][/hide]

2011-12-15 09:32:30

硬件仿真...信息:[SDAccel 60-280]其他參數(shù):' - d acc -k test.xclbin'信息:[SDAccel 60-174]正在運行仿真命令行:/home/lvs

2020-04-20 09:49:40

本帖最后由 機智小編 于 2017-3-29 13:59 編輯

為了降低開發(fā)智能硬件APP開發(fā)門檻,降低開發(fā)資源的投入,機智云在《APP開源框架》基礎(chǔ)上進(jìn)一步推出了實現(xiàn)項目完整控制功能的APP

2017-03-29 09:52:33

高速DAP仿真器 BURNER

2023-03-28 13:06:20

DFT 偽碼捕獲算法在進(jìn)行偽碼搜索的同時估計多普勒頻偏,為了滿足捕獲精度要求,需要增加DFT 點數(shù),但隨著運算點數(shù)的增加硬件實現(xiàn)難度成倍增長。本文提出一種基于FPGA 的在不

2009-09-22 09:59:21 12

12 硬件在環(huán)(HIL)仿真應(yīng)用中的LabVIEW FPGA:硬件在環(huán)(HIL)仿真可以對虛擬運行環(huán)境中的設(shè)備進(jìn)行非常逼真的模擬。一個典型的HIL系統(tǒng)包括用于從控制系統(tǒng)接收數(shù)據(jù)的傳感器、用于發(fā)送數(shù)據(jù)的

2009-10-01 19:06:04 25

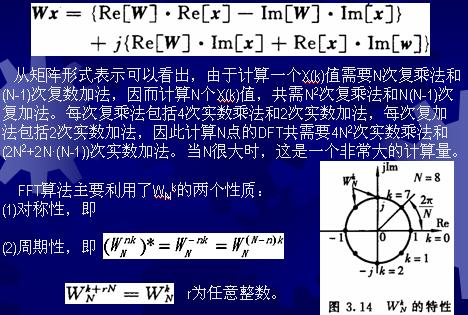

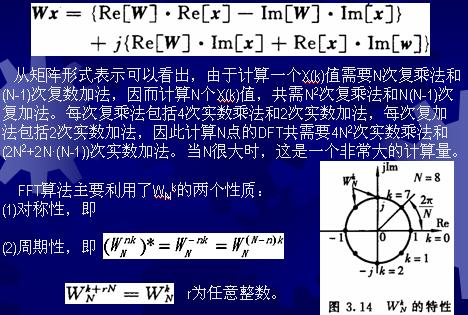

25 DFT的計算量

離散傅里葉變換在實際應(yīng)用中是非常重要的,利用它可以計算信號的頻譜、功率譜和線性卷積等。但是,如果使用定義式(

2008-10-30 12:59:19 4971

4971

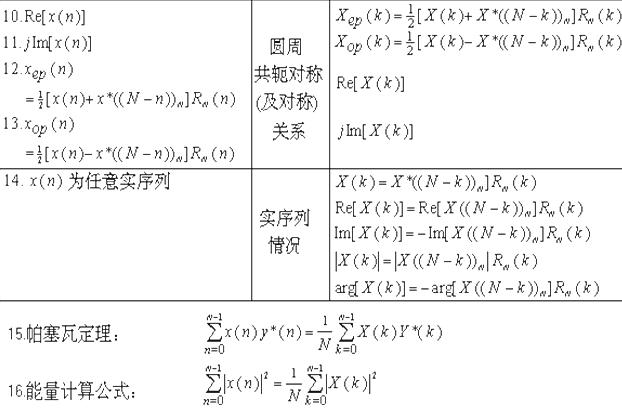

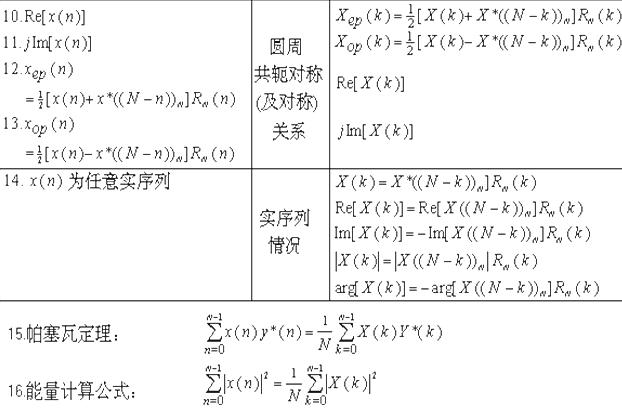

DFT性質(zhì)一覽表

2009-07-25 11:41:03 3998

3998

DFT:數(shù)字電路(fpga/asic)設(shè)計入門之可測試設(shè)計與可測性分析,離散傅里葉變換,(DFT)Direct Fouriet Transformer

可測試性技術(shù)(Design For Testability-

2010-06-07 11:00:48 29875

29875 ModelSim為HDL仿真工具,我們可以利用該軟件來實現(xiàn)對所設(shè)計的VHDL或Verilog程序進(jìn)行仿真,支持IEEE常見的各種硬件描述語言標(biāo)準(zhǔn)。可以進(jìn)行兩種語言的混合仿真,但推薦大家只對一種語言

2011-04-19 20:52:46 151

151 ModelSim為HDL仿真工具,我們可以利用該軟件來實現(xiàn)對所設(shè)計的VHDL或Verilog程序進(jìn)行仿真,支持IEEE常見的各種硬件描述語言標(biāo)準(zhǔn)。可以進(jìn)行兩種語言的混合仿真,但推薦大家只對一種語言

2011-05-27 16:41:59 132

132 本文基于PXI和cRIO搭建了ESP硬件在環(huán)仿真平臺。平臺可以將控制器放在仿真回路中,方便對控制器中的算法進(jìn)行測試。仿真試驗臺的搭建提高了ESP控制算法的開發(fā)速度。

2011-08-26 10:31:27 6238

6238

DFT在數(shù)字信號處理中有很重要的作用,如頻譜分析、FIR DF的實現(xiàn)、線性卷積等。一個重要的原因是DFT有高效算法。 為了了解高效算法的重要以及實現(xiàn)高效算法的思路,先介紹DFT的運算特

2011-09-07 23:59:55 57

57 首先給大家提供DFT和FFT的運算量的教程,內(nèi)容有直接用DFT計算運算量與用FFT計算的運算量比較和多種DFT算法(時間抽取算法DIT算法,頻率抽取算法DIF算法等.

2011-09-08 00:01:48 71

71 均衡技術(shù)是在接收端消除無線多徑衰落信道引起的碼間干擾的重要手段。介紹了一種利用單點DFT運算進(jìn)行均衡的算法,討論了在對該算法進(jìn)行定點仿真中遇到的幾個問題,最后給出了浮

2011-09-16 14:36:28 0

0 本內(nèi)容介紹了DFT可測試性設(shè)計的相關(guān)知識,并列舉了3中常見的可測性技術(shù)供大家學(xué)習(xí)

2012-05-30 16:42:27 7082

7082 俄勒岡州威爾遜維爾,2016 年 2 月 25 日 – Mentor Graphics公司(納斯達(dá)克代碼:MENT)今天宣布,推出用于 Veloce? 硬件仿真平臺的新型應(yīng)用程序,自此開辟了硬件仿真

2016-02-26 17:50:35 1068

1068 第3章--離散傅里葉變換(DFT)

2016-12-28 14:23:30 0

0 出的結(jié)果進(jìn)行閾值去噪處理,并根據(jù)循環(huán)前綴內(nèi)、外噪聲方差的均值在DFT插值的過程中設(shè)置相應(yīng)門限,然后對循環(huán)前綴內(nèi)的噪聲再次處理,以進(jìn)一步減小噪聲的影響。仿真實驗結(jié)果表明,在復(fù)雜度基本不變的前提下,該算法能夠較好地減小加性高

2017-11-25 11:50:29 1

1 高性能硬件與智能應(yīng)用程序的結(jié)合使得硬件仿真器更強大,能夠解決復(fù)雜的系統(tǒng)級設(shè)計驗證難題。 經(jīng)過三十年緩慢但穩(wěn)定的硬件仿真技術(shù)發(fā)展之后,就進(jìn)步加速和預(yù)期的新發(fā)展而言,其前景一片光明。在過去的 30 年中

2017-11-28 11:09:04 0

0 可測試性設(shè)計 (DFT) 在市場上所有的電子設(shè)計自動化 (EDA) 工具中是最不被重視的,縱然在設(shè)計階段提高芯片的可測試性將會大幅縮減高昂的測試成本,也是如此。最近的分析數(shù)據(jù)表明,在制造完成后測試

2017-11-28 11:28:38 0

0 DFT 是一種在設(shè)計階段將可測試性置入集成電路 (IC) 的方法,可以降低測試成本并提高制造良率,多年來以不同方式得到廣泛應(yīng)用。Ad-hoc 和結(jié)構(gòu)化這兩種方法能夠有效地檢測出電路中所有的故障,減少

2017-12-10 11:51:58 1

1 移動的信道信息和載波間干擾,然后,利用分組DFT算法進(jìn)行二次信道估計,并對ICI及其他干擾進(jìn)行二次消除,從而更加精確的估計出信道且進(jìn)一步提升系統(tǒng)性能。仿真結(jié)果表明:本文建議的GCE-BEM+ DFT和KL-BEM+ DFT算法性能相對于分組DFT算法、GCE-BEM和KL-BEM性能有了明顯的提升。

2017-12-27 11:52:43 3

3 Mentor Graphics公司今天宣布,憶芯科技 (Starblaze Technology) 已成功使用 Veloce 硬件加速仿真平臺進(jìn)行專業(yè)的高速企業(yè)級固態(tài)硬盤 (SSD) 存儲

2018-07-12 14:43:00 1619

1619 很多人認(rèn)為硬件加速器無非是一種速度更快的仿真器而已。毫無疑問,由于硬件加速器使用物理硬件進(jìn)行仿真,使用硬件加速器驗證復(fù)雜的集成電路和大型片上系統(tǒng)(SoC)能比軟件仿真器快若干數(shù)量級。與仿真用通用計算機相比,仿真用單一功能計算機能提供更高容量、更高效的系統(tǒng)。

2018-03-28 14:50:00 3160

3160

DFT。但由于上市時間方面的壓力,芯片在流片前只進(jìn)行了極少的DFT驗證,因此在芯片制造的過程中甚至在其返回到實驗室之后,必須繼續(xù)進(jìn)行DFT驗證。因此,我們需要的是一個硬件加速流程,從而可大幅縮短執(zhí)行完整驗證作業(yè)所需的仿真周期。

2018-03-01 11:13:33 1

1 了解如何使用Vivado System Generator for DSP進(jìn)行點對點以太網(wǎng)硬件協(xié)同仿真。

System Generator提供硬件協(xié)同仿真,可以將FPGA中運行的設(shè)計直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 使用,進(jìn)一步提升了現(xiàn)在的智能門禁系統(tǒng)的安全性,便利性。現(xiàn)在的智能硬件鎖基本都是通過物聯(lián)網(wǎng)技術(shù)對于功能的提升,人們通過app可以在線開鎖也可以通過指紋識別,人臉識別技術(shù)進(jìn)行開鎖,所以門鎖的開關(guān)數(shù)據(jù)直接

2018-12-11 17:05:38 568

568 本文檔詳細(xì)介紹的是KEIL C硬件仿真的操作步驟資料免費下載內(nèi)容包括了:第1步 在總目錄上用鼠標(biāo)“右鍵”選擇彈出菜單中的目標(biāo)屬性,第2步 進(jìn)入目標(biāo)屬性進(jìn)行晶振等參數(shù)的設(shè)置,第3步 輸出選項的設(shè)置

2019-03-08 15:16:00 17

17 通過此視頻可快速瀏覽 PADS DFT 審核的一些主要功能、優(yōu)點和易用性。在設(shè)計流程的早期使用 PADS DFT 審核可大幅降低 PCB 的批量投產(chǎn)時間,確保 100% 的測試點覆蓋和制造前所有網(wǎng)絡(luò)的可測試性。

2019-05-21 08:06:00 2927

2927 DFT 可以降低通過問題器件的風(fēng)險,如果最終在實際應(yīng)用中才發(fā)現(xiàn)器件有缺陷,所產(chǎn)生的成本將遠(yuǎn)遠(yuǎn)高于在制造階段發(fā)現(xiàn)的成本。它還能避免剔除無缺陷器件,從而提高良率。插入 DFT 亦能縮短與測試開發(fā)相關(guān)的時間,并減少測試裝配好的芯片所需的時間。

2019-09-16 14:31:51 1648

1648

用元素和測試點補充您的操作設(shè)計以促進(jìn)電路板的功能測試被稱為可測試性( DFT )設(shè)計。 DFT 與制造設(shè)計( DFM )不應(yīng)混淆,盡管兩者都是基于 CM 設(shè)備和過程能力的設(shè)計人員活動。 DFM

2020-10-12 20:42:17 3771

3771 VHDL與Verilog硬件描述語言在數(shù)字電路的設(shè)計中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設(shè)計復(fù)雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些

2021-08-04 14:16:44 3307

3307 stm32使用stlink進(jìn)行硬件仿真,具有很大的優(yōu)點,能夠?qū)崟r監(jiān)測到io電平,對于時序分析和debug具有很大幫助,而對于stc系列單片機,如果單純地使用軟件仿真,實際中仿真會很不方便,這就為尋求

2021-11-12 09:36:01 46

46 仿真APP是面向具體產(chǎn)品設(shè)備的專用仿真工具,是參數(shù)化模型、仿真流程、工業(yè)知識和專家經(jīng)驗的集成固化。仿真APP具備使用簡單、分享容易的特點,大幅度降低了仿真的技術(shù)門檻,既可以在企業(yè)內(nèi)部進(jìn)行分享應(yīng)用,又可以通過APP商店進(jìn)行交易共享,實現(xiàn)仿真知識的價值增值。

2022-03-04 13:41:15 1903

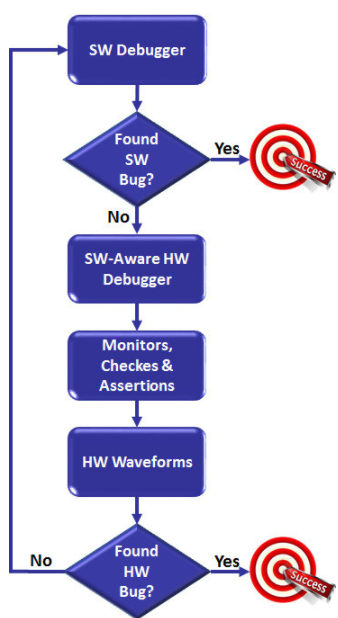

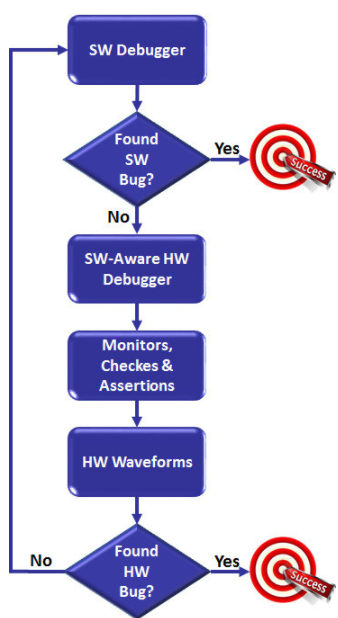

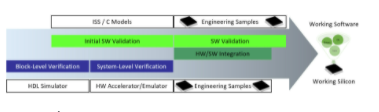

1903 工程團(tuán)隊發(fā)現(xiàn)現(xiàn)代硬件仿真器是測試硬件和在 SoC 設(shè)計中集成硬件和軟件的必要條件。它使他們能夠更有策略地進(jìn)行規(guī)劃并成功實施硬件/軟件聯(lián)合驗證。

2022-06-19 10:57:45 801

801

硬件仿真以前僅限于驗證超大型設(shè)計,如今已成為所有設(shè)計驗證和確認(rèn)流程的基礎(chǔ)。這種新發(fā)現(xiàn)的流行是日益增長的硅復(fù)雜性和嵌入式軟件的廣泛使用的結(jié)果。

2022-06-19 16:22:51 1824

1824

工程團(tuán)隊發(fā)現(xiàn)現(xiàn)代硬件仿真器是測試硬件和在 SoC 設(shè)計中集成硬件和軟件的必要條件。它使他們能夠更有策略地進(jìn)行規(guī)劃并成功實施硬件/軟件聯(lián)合驗證。

2022-07-09 07:59:00 523

523 在市場上所有的電子設(shè)計自動化 (EDA) 工具中,可測試設(shè)計 (DFT) 可能是最不被重視的。即使在設(shè)計階段將可測試性構(gòu)建到芯片中也會顯著降低高昂的測試成本。根據(jù)最近的分析,在制造后測試一批芯片以確定哪些部件沒有制造缺陷的成本已達(dá)到制造芯片成本的 40% 的驚人閾值。

2022-08-22 14:26:30 732

732

在本篇白皮書中,我們介紹了一個典型設(shè)計的 DFT 組件,并提出了多種可大幅改善 DFT 項目進(jìn)度的智能 DFT 方法。我們展示了如何將結(jié)構(gòu)化 DFT 和即插即用原則用于 DFT 基礎(chǔ)結(jié)構(gòu),來支持與其他設(shè)計開發(fā)工作相似的并行 DFT 開發(fā)和集成。

2022-11-30 10:15:00 575

575 相信很多ICer們在Light芯片的過程中無論前后端都聽過DFT設(shè)計測試,DFT全稱Design for Test(即可靠性設(shè)計),眾所周知,測試的目的是為了保證芯片成品的質(zhì)量以及功能邏輯的可靠性的必須 措施。

2023-03-06 14:45:10 2413

2413 DFT是確保芯片在制造過程中具有可測試性的一種技術(shù)。DFT友好的ECO是指在進(jìn)行ECO時, 不會破壞芯片的DFT功能或降低DFT覆蓋率的設(shè)計方法。

2023-03-06 14:47:07 1371

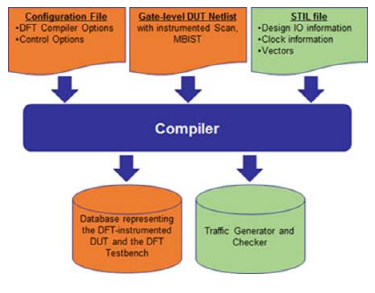

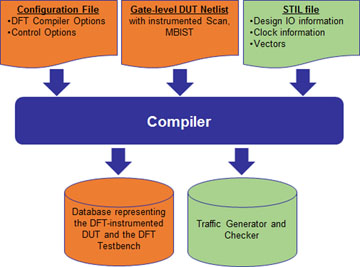

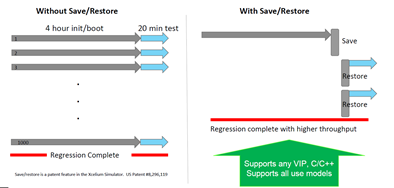

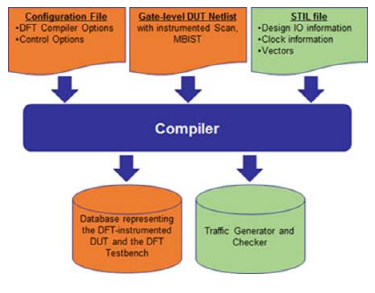

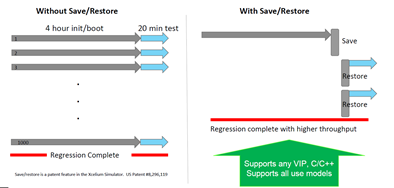

1371 當(dāng)今片上系統(tǒng)的設(shè)計復(fù)雜性日益增加,可能導(dǎo)致長達(dá)數(shù)小時、數(shù)天甚至數(shù)周的可測試性 (DFT) 仿真設(shè)計。由于這些往往發(fā)生在專用集成電路(ASIC)項目結(jié)束時,當(dāng)工程變更單(ECO)強制重新運行這些長時間

2023-04-20 10:21:24 1127

1127

DFT是確保芯片在制造過程中具有可測試性的一種技術(shù)。DFT友好的ECO是指在進(jìn)行ECO時, 不會破壞芯片的DFT功能或降低DFT覆蓋率的設(shè)計方法。DFT不友好的ECO會對芯片的測試和調(diào)試帶來很大的困難,可能導(dǎo)致芯片測試效率降低甚至無法測試。

2023-05-05 15:06:37 1262

1262

fft和dft的區(qū)別聯(lián)系 快速傅里葉變換(FFT)和離散傅里葉變換(DFT)是信號處理和數(shù)學(xué)計算領(lǐng)域中最常見的技術(shù)之一。它們都是用于將離散信號從時域轉(zhuǎn)換到頻域的方法,而在此轉(zhuǎn)換過程中,它們都利用

2023-09-07 16:43:53 3139

3139 英諾達(dá)發(fā)布了自主研發(fā)的靜態(tài)驗證EDA工具EnAltius?昂屹? DFT Checker,該工具可以在設(shè)計的早期階段發(fā)現(xiàn)與DFT相關(guān)的問題或設(shè)計缺陷。

2023-09-13 09:05:18 746

746 長。而通過專門的設(shè)備在硬件上調(diào)試芯片設(shè)計,利用專用的硬件系統(tǒng)對仿真進(jìn)行加速,如硬件仿真,便是重要的解決方案之一。硬件仿真首先將硬件設(shè)計(通常以HDL,例如Veril

2023-09-13 08:28:02 393

393

DFT PLL向量,ATE怎么用? 自動測試設(shè)備(ATE)對PLL(鎖相環(huán))進(jìn)行測試時,我們首先要明白PLL在系統(tǒng)級芯片(SoC)中的重要性。它是SoC中關(guān)鍵的時鐘或信號同步部件,其性能直接影響

2023-10-30 11:44:17 662

662

DFT全稱為Design for Test,可測性設(shè)計。就是說我們設(shè)計好一個芯片后,在仿真時可能99%的用例都通過了,怎么保證流片出來的實際芯片也能正常工作呢?

2023-12-06 15:02:43 405

405 ModelSim為HDL仿真工具,我們可以利用該軟件來實現(xiàn)對所設(shè)計的VHDL或Verilog程 序進(jìn)行仿真,支持IEEE常見的各種硬件描述語言標(biāo)準(zhǔn)。可以進(jìn)行兩種語言的混合仿真,但 推薦大家只對一種語言仿真。

2024-01-14 09:47:47 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論