資料介紹

引言

DFT(Discrete Fourier Transformation)是數字信號分析與處理如圖形、語音及圖像等領域的重要變換工具,直接計算DFT的計算量與變換區間長度N的平方成正比。當N較大時,因計算量太大,直接用DFT算法進行譜分析和信號的實時處理是不切實際的。快速傅立葉變換(Fast Fourier Transformation,簡稱FFT)使DFT運算效率提高1~2個數量級。其原因是當N較大時,對DFT進行了基4和基2分解運算。FFT算法除了必需的數據存儲器ram和旋轉因子rom外,仍需較復雜的運算和控制電路單元,即使現在,實現長點數的FFT仍然是很困難。本文提出的FFT實現算法是基于FPGA之上的,算法完成對一個序列的FFT計算,完全由脈沖觸發,外部只輸入一脈沖頭和輸入數據,便可以得到該脈沖頭作為起始標志的N點FFT輸出結果。由于使用了雙ram,該算法是流型(Pipelined)的,可以連續計算N點復數輸入FFT,即輸入可以是分段N點連續復數數據流。采用DIF(Decimation In Frequency)-FFT和DIT(Decimation In Time)-FFT對于算法本身來說是無關緊要的,因為兩種情況下只是存儲器的讀寫地址有所變動而已,不影響算法的結構和流程,也不會對算法復雜度有何影響。算法實現的可以是基2/4混合基FFT,也可以是純基4FFT和純基2FFT運算。

傅立葉變換和逆變換

對于變換長度為N的序列x(n)其傅立葉變換可以表示如下:

Nnk

X(k)=DFT[x(n)] = Σ x(n)W

n=0

式(1)

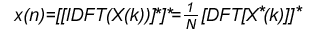

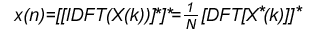

其中,W=exp(-2π/N)。 當點數N較大時,必須對式(1)進行基4/基2分解,以短點數實現長點數的變換。而IDFT的實現在DFT的基礎上就顯得較為簡單了:

式(2)

由式(2)可以看出,在FFT運算模塊的基礎上,只需將輸入序列進行取共軛后再進行FFT運算,輸出結果再取一次共軛便實現了對輸入序列的IDFT運算,因子1/N對于不同的數據表示格式具體實現時的處理方式是不一樣的。IDFT在FFT的基礎上輸入和輸出均有一次共軛操作,但它們共用一個內核,仍然是十分方便的。

基4和基2

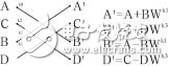

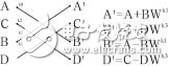

基4和基2運算流圖及信號之間的運算關系如圖1所示:

(a)基4蝶形算法(b)基2蝶形算法

以基4為例,令A=r0+j×i0;B=r1+j×i1;C=r2+j×i2;D=r3+j×i3;Wk0=c0+j×s0:Wk1=c1+j×s1;Wk2=c2+j×s2;Wk3=c3+j×s3。分別代入圖1中的基4運算的四個等式中有:

A‘=[r0+(r1×c1-i1×s1)+(r2×c2-i2×s2)+(r3×c3-i3×s3)]+j[i0+(i1×c1+r1×s1)+(i2×c2+r2×s2)+(i3×c3+r3×s3)] 式(3)

B’=[r0+(i1×c1+r1×s1)-(r2×c2-i2×s2)-(i3×c3+r3×s3)]+j[i0-(r1×c1-i1×s1)-(i2×c2+r2×s2)+(r3×c3-i3×s3)] 式(4)

C‘=[r0-(r1×c1-i1×s1)+(r2×c2-i2×s2)-(r3×c3-i3×s3)]+j[i0-(i1×c1+r1×s1)+(i2×c2+r2×s2)-(i3×c3+r3×s3)] 式(5)

D’=[r0-(i1×c1+r1×s1)-(r2×c2-i2×s2)+(i3×c3+r3×s3)]+j[i0+(r1×c1-i1×s1)-(i2×c2+r2×s2)-(r3×c3-i3×s3)] 式(6)

可以看出,式(3)至式(6)有多個公共項和類似項,這一點得到充分利用之后可以大大縮減基4和基2運算模塊中的乘法器的個數,如上面A‘至D’的四個等式中的這三對類似項:(r1×c1-i1×s1)與(i1×c1+r1×s1)、(r2×c2-i2×s2)與(i2×c2+r2×s2)、(r3×c3-i3×s3)與(i3×c3+r3×s3)以高于輸入數據率的時鐘進行時分復用,最終可以做到只需要3個甚至1個復數乘法器便可以實現。基2運算之所以采用圖1-(b)中的形式進行基2運算,是為了將基本模塊做成基4/2復用模塊,它對于N有著更大的適用性和可借鑒性。在基4、基2和基4/2模塊的基礎上,構建基16、基8和基16/8模塊有著非常大的意義。

算法實現

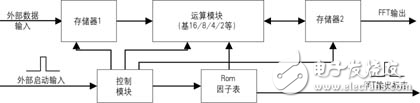

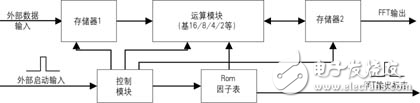

傅立葉變換實現時首先進行基2、基4分解,一般來說,如果算法使用基4實現,雖然使用的資源多了一些,但速度上的好處足以彌補。如果資源充足,使用基16、基8或基16/8復用模塊,速度可以大大提高。一般FFT實現簡單框圖如圖2所示。

在圖2中,運算模塊即為基2/4/8/16模塊或它們的復用模塊,Rom表中存儲的是N點旋轉因子表。控制模塊產生所有的控制信號,存儲器1和2的讀寫地址、寫使能、運算模塊的啟動信號及因子表的讀地址等信號。當然對于運算模塊為基16/8復用模塊時,控制模塊就需要產生模式選擇信號,如對于運算模塊是基4/2模塊時,該信號就決定了內部運算模塊是進行基4運算還是基2運算。存儲器1作為當前輸入標志對應輸入N點數據的緩沖器,存儲器2作為中間結果存儲器,用于存儲運算模塊計算出的各Pass的結果。在圖中的各種地址、使能和數據的緊密配合下,經過一定延時后輸出計算結果及其對應指示標志。圖2只是一定點或浮點的FFT實現模塊,如果是塊浮點運算,則必須加入一個數據因子控制器,控制每遍運算過程中的數據大小,并根據各個Pass的乘性因子之和的大小,對最終輸出進行大小控制,以保證每段FFT運算輸出增益一致。

外部輸入為N點數據段流和啟動信號(N點之間如無間隔,則每N數據點輸入一脈沖信號),一方面,外部數據存入存儲器1中,同時通過控制模塊的控制,讀出存儲器1中的前段N點數據和Rom表中的因子及相關控制信號送入運算核心模塊進行各個Pass的運算,每個Pass的輸出都存入存儲器2中,最后一個Pass的計算結果存入存儲器2中,并在下一個啟動頭到來后,輸出計算結果。對圖2的實現,除去運算模塊,關鍵是各個Pass數據因子讀寫地址及控制信號的配合。

速度、資源和精度

假定輸入數據的速率為fin,則每數據的持續時間T=1/fin,運算模塊的計算時鐘頻率為fa,對于N(N=2p,p即為Pass數目)點FFT計算時延與Pass數目直接相關。如果使用基2運算不考慮控制開銷,純粹的計算時延為td=p×N×T×fin/fa。顯然在fa》p× fin時,在N點內可完成FFT運算。否則不能完成,即不能實現流型的變換。這在N很大且輸入數據速率較高時以FPGA實現幾乎是不可能的,而且內部計算時鐘過高容易導致電路的工作不穩定。設基2時的最小可流型工作運算頻率為fa0,則使用基4實現流型的變換,計算時鐘fa= fa0就可以。而使用基8時計算時鐘fa= fa0便可完成,基16時為fa0的1/4。上面所討論的是純基運算,當N不為4的冪次方時(如N=2048=16×16×8,運算模塊為基16/8復用模塊),而又希望使用較低倍的時鐘完成運算時,圖2中的運算模塊必然包括基4/2復用模塊(即基16/8復用模塊),這也就是前面提到復用模塊的主要用意。由上面的分析可以得出結論,如果計算使用的基越大,完成速度越快。 但是,使用基16/8模塊所使用的邏輯資源要比基4/2模塊多將近一倍,這是因為基16/8復用模塊是以基4模塊和基4/2復用模塊構建而成。當然,可以直接實現基16/8復用模塊,但用FPGA很難解決復雜度和成本問題。另外,如果流型運算間隔比N點數據長度長一倍以上,可以考慮在較低的計算時鐘下使用基2運算模塊實現流型FFT。

運算結果的精度直接與計算過程中數據和因子位數(浮點算法)相關,如果中間計算的位數、存儲數據位數和Rom表中的位數越大,輸出精度就越大。當然,位數增大后邏輯運算資源和存儲資源都會直線上升。

浮點、塊浮點和定點FFT

根據運算過程中對數據位數取位和表示形式的不同,可以將FFT分為浮點FFT、塊浮點FFT和定點FFT。它們在實現時對于系統資源的要求是不同的,而且有著不同的適用范圍。

浮點FFT是基于數據表示為浮點的基礎之上的,即數據是由一純小數和一因子組成,輸入要轉成純小數和因子的浮點表示形式,所有計算過程中保存應得計算結果大小,而輸出要變成所需大小的定點表示形式。只要因子位數足夠大,浮點FFT計算是不會溢出的。而定點則是所有計算過程中都是定點運算,如果各個Pass的截位規則不適當,很容易出現溢出,必須要有溢出控制。塊浮點是介于它們之間的一種運算機制,它是根據本Pass的輸入數據的大小,在計算之前進行控制(數據上移一比特或下移一比特或乘以一特定因子),可以保證不溢出,但一般也需要溢出控制。

浮點運算沒有溢出,信號平均信噪比高,但由于因子的運算必然導致電路復雜,實現困難。定點運算實現簡單,難以保證不溢出,需要統計得出合適的截位規則,否則溢出嚴重導致輸出結果錯誤。塊浮點由于每個Pass(包括最后輸出前)結束后有一統計控制過程,延時較大,但是可以保證不溢出而且電路又相對浮點來說簡單得多。 應根據具體應用的具體要求,選擇合適的FFT。如果要求精度,并且要解決頻域很高的單頻干擾,就必須使用浮點的FFT,使用數據位數很大的定點和塊浮點也能解決這個問題,但位數的確定十分困難。如果不要求高精度,邏輯資源和Rom比較緊張,可考慮定點運算。如果輸入在頻域集中于幾個點上或者對精度要求一般,可以慢速處理,可以采用塊浮點運算,就能夠保證這幾點的信噪比,而忽略其他點處的信噪比。

DFT(Discrete Fourier Transformation)是數字信號分析與處理如圖形、語音及圖像等領域的重要變換工具,直接計算DFT的計算量與變換區間長度N的平方成正比。當N較大時,因計算量太大,直接用DFT算法進行譜分析和信號的實時處理是不切實際的。快速傅立葉變換(Fast Fourier Transformation,簡稱FFT)使DFT運算效率提高1~2個數量級。其原因是當N較大時,對DFT進行了基4和基2分解運算。FFT算法除了必需的數據存儲器ram和旋轉因子rom外,仍需較復雜的運算和控制電路單元,即使現在,實現長點數的FFT仍然是很困難。本文提出的FFT實現算法是基于FPGA之上的,算法完成對一個序列的FFT計算,完全由脈沖觸發,外部只輸入一脈沖頭和輸入數據,便可以得到該脈沖頭作為起始標志的N點FFT輸出結果。由于使用了雙ram,該算法是流型(Pipelined)的,可以連續計算N點復數輸入FFT,即輸入可以是分段N點連續復數數據流。采用DIF(Decimation In Frequency)-FFT和DIT(Decimation In Time)-FFT對于算法本身來說是無關緊要的,因為兩種情況下只是存儲器的讀寫地址有所變動而已,不影響算法的結構和流程,也不會對算法復雜度有何影響。算法實現的可以是基2/4混合基FFT,也可以是純基4FFT和純基2FFT運算。

傅立葉變換和逆變換

對于變換長度為N的序列x(n)其傅立葉變換可以表示如下:

Nnk

X(k)=DFT[x(n)] = Σ x(n)W

n=0

式(1)

其中,W=exp(-2π/N)。 當點數N較大時,必須對式(1)進行基4/基2分解,以短點數實現長點數的變換。而IDFT的實現在DFT的基礎上就顯得較為簡單了:

式(2)

由式(2)可以看出,在FFT運算模塊的基礎上,只需將輸入序列進行取共軛后再進行FFT運算,輸出結果再取一次共軛便實現了對輸入序列的IDFT運算,因子1/N對于不同的數據表示格式具體實現時的處理方式是不一樣的。IDFT在FFT的基礎上輸入和輸出均有一次共軛操作,但它們共用一個內核,仍然是十分方便的。

基4和基2

基4和基2運算流圖及信號之間的運算關系如圖1所示:

(a)基4蝶形算法(b)基2蝶形算法

以基4為例,令A=r0+j×i0;B=r1+j×i1;C=r2+j×i2;D=r3+j×i3;Wk0=c0+j×s0:Wk1=c1+j×s1;Wk2=c2+j×s2;Wk3=c3+j×s3。分別代入圖1中的基4運算的四個等式中有:

A‘=[r0+(r1×c1-i1×s1)+(r2×c2-i2×s2)+(r3×c3-i3×s3)]+j[i0+(i1×c1+r1×s1)+(i2×c2+r2×s2)+(i3×c3+r3×s3)] 式(3)

B’=[r0+(i1×c1+r1×s1)-(r2×c2-i2×s2)-(i3×c3+r3×s3)]+j[i0-(r1×c1-i1×s1)-(i2×c2+r2×s2)+(r3×c3-i3×s3)] 式(4)

C‘=[r0-(r1×c1-i1×s1)+(r2×c2-i2×s2)-(r3×c3-i3×s3)]+j[i0-(i1×c1+r1×s1)+(i2×c2+r2×s2)-(i3×c3+r3×s3)] 式(5)

D’=[r0-(i1×c1+r1×s1)-(r2×c2-i2×s2)+(i3×c3+r3×s3)]+j[i0+(r1×c1-i1×s1)-(i2×c2+r2×s2)-(r3×c3-i3×s3)] 式(6)

可以看出,式(3)至式(6)有多個公共項和類似項,這一點得到充分利用之后可以大大縮減基4和基2運算模塊中的乘法器的個數,如上面A‘至D’的四個等式中的這三對類似項:(r1×c1-i1×s1)與(i1×c1+r1×s1)、(r2×c2-i2×s2)與(i2×c2+r2×s2)、(r3×c3-i3×s3)與(i3×c3+r3×s3)以高于輸入數據率的時鐘進行時分復用,最終可以做到只需要3個甚至1個復數乘法器便可以實現。基2運算之所以采用圖1-(b)中的形式進行基2運算,是為了將基本模塊做成基4/2復用模塊,它對于N有著更大的適用性和可借鑒性。在基4、基2和基4/2模塊的基礎上,構建基16、基8和基16/8模塊有著非常大的意義。

算法實現

傅立葉變換實現時首先進行基2、基4分解,一般來說,如果算法使用基4實現,雖然使用的資源多了一些,但速度上的好處足以彌補。如果資源充足,使用基16、基8或基16/8復用模塊,速度可以大大提高。一般FFT實現簡單框圖如圖2所示。

在圖2中,運算模塊即為基2/4/8/16模塊或它們的復用模塊,Rom表中存儲的是N點旋轉因子表。控制模塊產生所有的控制信號,存儲器1和2的讀寫地址、寫使能、運算模塊的啟動信號及因子表的讀地址等信號。當然對于運算模塊為基16/8復用模塊時,控制模塊就需要產生模式選擇信號,如對于運算模塊是基4/2模塊時,該信號就決定了內部運算模塊是進行基4運算還是基2運算。存儲器1作為當前輸入標志對應輸入N點數據的緩沖器,存儲器2作為中間結果存儲器,用于存儲運算模塊計算出的各Pass的結果。在圖中的各種地址、使能和數據的緊密配合下,經過一定延時后輸出計算結果及其對應指示標志。圖2只是一定點或浮點的FFT實現模塊,如果是塊浮點運算,則必須加入一個數據因子控制器,控制每遍運算過程中的數據大小,并根據各個Pass的乘性因子之和的大小,對最終輸出進行大小控制,以保證每段FFT運算輸出增益一致。

外部輸入為N點數據段流和啟動信號(N點之間如無間隔,則每N數據點輸入一脈沖信號),一方面,外部數據存入存儲器1中,同時通過控制模塊的控制,讀出存儲器1中的前段N點數據和Rom表中的因子及相關控制信號送入運算核心模塊進行各個Pass的運算,每個Pass的輸出都存入存儲器2中,最后一個Pass的計算結果存入存儲器2中,并在下一個啟動頭到來后,輸出計算結果。對圖2的實現,除去運算模塊,關鍵是各個Pass數據因子讀寫地址及控制信號的配合。

速度、資源和精度

假定輸入數據的速率為fin,則每數據的持續時間T=1/fin,運算模塊的計算時鐘頻率為fa,對于N(N=2p,p即為Pass數目)點FFT計算時延與Pass數目直接相關。如果使用基2運算不考慮控制開銷,純粹的計算時延為td=p×N×T×fin/fa。顯然在fa》p× fin時,在N點內可完成FFT運算。否則不能完成,即不能實現流型的變換。這在N很大且輸入數據速率較高時以FPGA實現幾乎是不可能的,而且內部計算時鐘過高容易導致電路的工作不穩定。設基2時的最小可流型工作運算頻率為fa0,則使用基4實現流型的變換,計算時鐘fa= fa0就可以。而使用基8時計算時鐘fa= fa0便可完成,基16時為fa0的1/4。上面所討論的是純基運算,當N不為4的冪次方時(如N=2048=16×16×8,運算模塊為基16/8復用模塊),而又希望使用較低倍的時鐘完成運算時,圖2中的運算模塊必然包括基4/2復用模塊(即基16/8復用模塊),這也就是前面提到復用模塊的主要用意。由上面的分析可以得出結論,如果計算使用的基越大,完成速度越快。 但是,使用基16/8模塊所使用的邏輯資源要比基4/2模塊多將近一倍,這是因為基16/8復用模塊是以基4模塊和基4/2復用模塊構建而成。當然,可以直接實現基16/8復用模塊,但用FPGA很難解決復雜度和成本問題。另外,如果流型運算間隔比N點數據長度長一倍以上,可以考慮在較低的計算時鐘下使用基2運算模塊實現流型FFT。

運算結果的精度直接與計算過程中數據和因子位數(浮點算法)相關,如果中間計算的位數、存儲數據位數和Rom表中的位數越大,輸出精度就越大。當然,位數增大后邏輯運算資源和存儲資源都會直線上升。

浮點、塊浮點和定點FFT

根據運算過程中對數據位數取位和表示形式的不同,可以將FFT分為浮點FFT、塊浮點FFT和定點FFT。它們在實現時對于系統資源的要求是不同的,而且有著不同的適用范圍。

浮點FFT是基于數據表示為浮點的基礎之上的,即數據是由一純小數和一因子組成,輸入要轉成純小數和因子的浮點表示形式,所有計算過程中保存應得計算結果大小,而輸出要變成所需大小的定點表示形式。只要因子位數足夠大,浮點FFT計算是不會溢出的。而定點則是所有計算過程中都是定點運算,如果各個Pass的截位規則不適當,很容易出現溢出,必須要有溢出控制。塊浮點是介于它們之間的一種運算機制,它是根據本Pass的輸入數據的大小,在計算之前進行控制(數據上移一比特或下移一比特或乘以一特定因子),可以保證不溢出,但一般也需要溢出控制。

浮點運算沒有溢出,信號平均信噪比高,但由于因子的運算必然導致電路復雜,實現困難。定點運算實現簡單,難以保證不溢出,需要統計得出合適的截位規則,否則溢出嚴重導致輸出結果錯誤。塊浮點由于每個Pass(包括最后輸出前)結束后有一統計控制過程,延時較大,但是可以保證不溢出而且電路又相對浮點來說簡單得多。 應根據具體應用的具體要求,選擇合適的FFT。如果要求精度,并且要解決頻域很高的單頻干擾,就必須使用浮點的FFT,使用數據位數很大的定點和塊浮點也能解決這個問題,但位數的確定十分困難。如果不要求高精度,邏輯資源和Rom比較緊張,可考慮定點運算。如果輸入在頻域集中于幾個點上或者對精度要求一般,可以慢速處理,可以采用塊浮點運算,就能夠保證這幾點的信噪比,而忽略其他點處的信噪比。

下載該資料的人也在下載

下載該資料的人還在閱讀

更多 >

- 基于新型FPGA的FFT設計與實現 48次下載

- 如何使用FPGA實現全并行結構FFT 11次下載

- 如何使用FPGA實現基于修正Rife算法的正弦波頻率估計 7次下載

- 如何使用FPGA實現FFT的研究 15次下載

- 如何使用FPGA和CPLD實現FFT算法與仿真分析 19次下載

- 使用FPGA實現流水線結構的FFT處理器論文講解 12次下載

- LTE物理上行共享信道中FFT算法分析與FPGA實現 8次下載

- 基于FPGA的FFT實現方案 11次下載

- 數字信號處理技術FFT算法與FPGA的FFT變換設計 20次下載

- 基于Xilinx_FPGA_IP核的FFT算法的設計與實現 37次下載

- 基于FPGA的FFT信號處理器的設計與實現 44次下載

- FPGA內嵌的塊RAM在FFT算法中的應用 54次下載

- 利用CORDIC算法在FPGA中實現可參數化的FFT

- 利用CORDIC 算法在FPGA 中實現可參數化的FFT

- 基于FPGA的超高速FFT硬件實現

- 調用HLS的FFT庫實現N點FFT 1138次閱讀

- 從Xilinx FFT IP核到FPGA實現OFDM 1452次閱讀

- 利用FFT算法實現快速傅里葉變換 3332次閱讀

- 傅里葉變換(FFT)的主要思想與算法 3964次閱讀

- 用FPGA實現FFT算法的方法 5590次閱讀

- Xilinx FFT IP介紹與仿真測試 3059次閱讀

- 采用FPGA實現FFT算法 1.7w次閱讀

- 基于Xilinx FPGA 實現FFT算法的電力諧波檢測的設計方案詳解 3950次閱讀

- 基于FPGA的Cordic算法實現的設計與驗證 2812次閱讀

- 淺談FFT算法原理 基于FPGA的FFT算法的硬件實現 2.6w次閱讀

- 基于fft算法的MATLAB仿真 2707次閱讀

- 一種基于FPGA的數字頻譜儀設計與實現 1.3w次閱讀

- 【實用指南】教你使用FFT和示波器 6416次閱讀

- 實數FFT算法的設計及其C語言實現 1w次閱讀

- 利用FFT IP Core實現FFT算法 6938次閱讀

下載排行

本周

- 1電子電路原理第七版PDF電子教材免費下載

- 0.00 MB | 1491次下載 | 免費

- 2單片機典型實例介紹

- 18.19 MB | 95次下載 | 1 積分

- 3S7-200PLC編程實例詳細資料

- 1.17 MB | 27次下載 | 1 積分

- 4筆記本電腦主板的元件識別和講解說明

- 4.28 MB | 18次下載 | 4 積分

- 5開關電源原理及各功能電路詳解

- 0.38 MB | 11次下載 | 免費

- 6100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 7基于單片機和 SG3525的程控開關電源設計

- 0.23 MB | 4次下載 | 免費

- 8基于AT89C2051/4051單片機編程器的實驗

- 0.11 MB | 4次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 2PADS 9.0 2009最新版 -下載

- 0.00 MB | 66304次下載 | 免費

- 3protel99下載protel99軟件下載(中文版)

- 0.00 MB | 51209次下載 | 免費

- 4LabView 8.0 專業版下載 (3CD完整版)

- 0.00 MB | 51043次下載 | 免費

- 5555集成電路應用800例(新編版)

- 0.00 MB | 33562次下載 | 免費

- 6接口電路圖大全

- 未知 | 30320次下載 | 免費

- 7Multisim 10下載Multisim 10 中文版

- 0.00 MB | 28588次下載 | 免費

- 8開關電源設計實例指南

- 未知 | 21539次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935053次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537793次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234313次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191183次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183277次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138039次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論