完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 賽靈思

提供賽靈思公司最新的技術(shù)和產(chǎn)品信息,工程師最喜歡的賽靈思技術(shù)社區(qū)

文章:1699個(gè) 瀏覽:132288次 帖子:56個(gè)

Xylon在Embedded World 2015上使用MicroZed套件演示了面部檢測(cè)C可調(diào)用RTL IP

在大數(shù)據(jù)與人工智能迅速興起的時(shí)代,ACAP 理想適用于加速?gòu)V泛的應(yīng)用,其中包括 視頻轉(zhuǎn)碼、數(shù)據(jù)庫(kù)、數(shù)據(jù)壓縮、搜索、AI推斷、基因組學(xué)、機(jī)器視覺(jué)、計(jì)算存儲(chǔ)...

使用AWS F1開(kāi)發(fā)云規(guī)模FPGA加速

亞馬遜的Gadi Hutt在硅谷舉辦的第一屆年度Xilinx開(kāi)發(fā)者論壇上發(fā)表了主題演講。

業(yè)內(nèi)大多數(shù)FPGA 均提供數(shù)字時(shí)鐘管理( 賽靈思公司的全部FPGA 均具有這種特性)。賽靈思公司推出最先進(jìn)的FPGA 提供數(shù)字時(shí)鐘管理和相位環(huán)路鎖定。相...

2017-02-11 標(biāo)簽:FPGA賽靈思數(shù)字時(shí)鐘管理 1987 0

如何用單個(gè)賽靈思FPGA數(shù)字化數(shù)百個(gè)信號(hào)

在新型賽靈思 FPGA 上使用低電壓差分信號(hào)(LVDS),只需一個(gè)電阻和一個(gè)電容就能夠數(shù)字化輸入信號(hào)。由于目前這一代賽靈思器件上提供有數(shù)百個(gè) LVD...

協(xié)助全球最大的云端服務(wù)提供商著手開(kāi)發(fā)和部署可重配置加速平臺(tái)

All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX))宣布,將在 2016 全球超...

不可錯(cuò)過(guò)的400Gbps以太網(wǎng)演示

在那里,毫無(wú)疑問(wèn)你會(huì)駐足在賽靈思展位前(# 23)觀看一個(gè)基于賽靈思Virtex UltraScale VU095 FPGA評(píng)估板VCU109的Spir...

基于視頻/視覺(jué)的系統(tǒng)發(fā)展最新趨勢(shì)的討論

賽靈思廣播與專業(yè)音視頻業(yè)務(wù)部總監(jiān)Aaron Behman在本視頻中與您一起討論基于視頻/視覺(jué)的系統(tǒng)發(fā)展最新趨勢(shì),并解釋了賽靈思如何為高性能圖像處理搭配“...

Nextera視頻Sony NMI系統(tǒng)是一個(gè)即插即用的VoIP系統(tǒng),采用COTS IP開(kāi)關(guān)提供端對(duì)端壓縮或非壓縮視頻IP.Xilinx FPGA為系統(tǒng)提...

組合運(yùn)用多種智能I/O規(guī)劃工具能使引腳分配過(guò)程變輕松

對(duì)于需要在PCB板上使用大規(guī)模FPGA器件的設(shè)計(jì)人員來(lái)說(shuō),I/O引腳分配是必須面對(duì)的眾多挑戰(zhàn)之一。

This Webinar will provide insight into the role of All Programmable SoCs in ...

《UltraFAST 高層次生產(chǎn)力設(shè)計(jì)方法指南》簡(jiǎn)介

對(duì)寶貴的差異化邏輯使用并行開(kāi)發(fā)流程,實(shí)現(xiàn)您的產(chǎn)品在市場(chǎng)上的差異化,且 shell 可用于將 IP 與生態(tài)系統(tǒng)的其它部分集成。

2019-07-31 標(biāo)簽:控制系統(tǒng)賽靈思可編程 1927 0

如何使用純模式或組件模式進(jìn)行設(shè)計(jì)

了解SelectIO體系結(jié)構(gòu)的詳細(xì)信息,包括使用純模式或組件模式以及如何開(kāi)始使用純模式或組件模式進(jìn)行設(shè)計(jì)。 該視頻還介紹了高速SelectIO向?qū)У谋?..

2018-11-27 標(biāo)簽:賽靈思設(shè)計(jì) 1923 0

賽靈思攜手BEEcube推出全球首款毫米波原型設(shè)計(jì)平臺(tái)解決方案

致力于支持5G應(yīng)用創(chuàng)新開(kāi)發(fā),集成在BEEcube BEE7基帶平臺(tái)上的賽靈思256QAM毫米波調(diào)制解調(diào)器IP為寬帶回程原型設(shè)計(jì)提供完整的開(kāi)箱即用型解決方案

運(yùn)用 IP子系統(tǒng)將設(shè)計(jì)提升到全新的高度

賽靈思的新型LogiCOREIP子系統(tǒng)屬于高度可配置并根據(jù)市場(chǎng)量身定制的構(gòu)建模塊,其集成了多達(dá)80個(gè)不同的IP 核、軟件驅(qū)動(dòng)程序、設(shè)計(jì)實(shí)例和測(cè)試平臺(tái)。

基于AXI4的可編程SOC系統(tǒng)設(shè)計(jì)1

現(xiàn)在FPGA越來(lái)越被廣泛地應(yīng)用在各個(gè)領(lǐng)域中。Xilinx公司將專用的嵌入式處理器PowerPC硬核、ARM Cortex-A9 MP硬核和嵌入式處理器M...

賽靈思(Xilinx)FPGA用戶約束文件的分類和語(yǔ)法說(shuō)明

FPGA設(shè)計(jì)中的約束文件有3類:用戶設(shè)計(jì)文件(.UCF文件)、網(wǎng)表約束文件(.NCF文件)以及物理約束文件(.PCF文件),可以完成時(shí)序約束、管腳約束以...

Xilinx可編程邏輯器件設(shè)計(jì)與開(kāi)發(fā)(基礎(chǔ)篇)連載35:Spartan

ChipScope Pro 分析工具(Analyzer tool)直接與ICON、ILA、IBA、VIO及IBERT核相連,用戶可以實(shí)時(shí)地創(chuàng)建或修改觸發(fā)條件。

Xilinx的Dave Tokic與MathWorks高級(jí)應(yīng)用工程師Alex Schreiber談?wù)撍麄兊男耑ynq設(shè)計(jì)包。

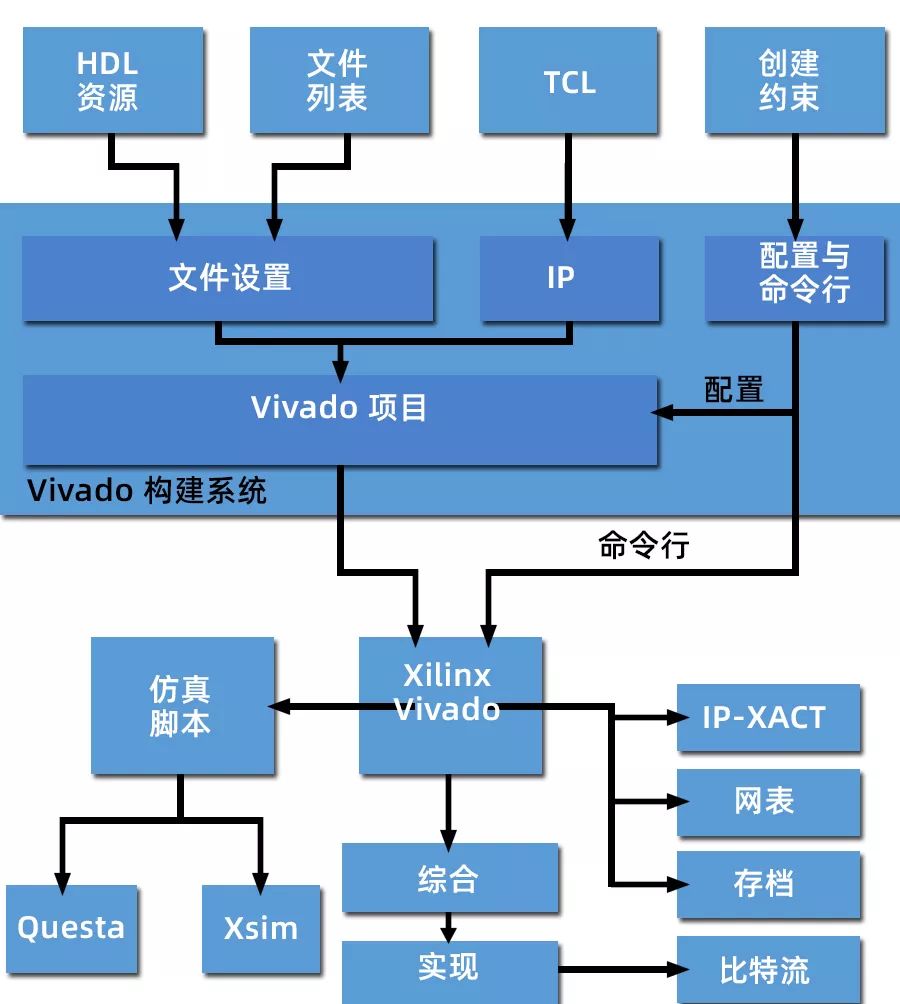

如何實(shí)現(xiàn) FPGA 構(gòu)建環(huán)境的自動(dòng)化

作者:Andreas Braun Stefan Wiehler 設(shè)計(jì)工程師,MLE 公司 創(chuàng)建 FPGA 設(shè)計(jì)和維護(hù) Vivado 設(shè)計(jì)套件項(xiàng)目時(shí),版本...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |