完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > cadence

鏗騰電子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一個專門從事電子設計自動化(EDA)的軟件公司,由SDA Systems和ECAD兩家公司于1988年兼并而成。是全球最大的電子設計技術(Electronic Design Technologies)、程序方案服務和設計服務供應商。其解決方案旨在提升和監控半導體、計算機系統、網絡工程和電信設備、消費電子產品以及其它各類型電子產品的設計。

文章:622個 瀏覽:143854次 帖子:518個

如何解決ALLEGRO16.2出現的“changes not saved, cannot update the env file”問題

運行Cadence16.2的Allegro PCB Editor時,在Setep→Use Preferences時出現以下提示對話框:No match...

AD PCB封裝轉Allegro封裝或者AD PCB轉Allegro PCB

AD封裝轉ALLEGRO封裝時,要把所有封裝放到一張PCB上或者分批次的放到PCB上,把PCB轉成ALLEGRO格式的,然后再用ALLEGRO導出PCB封裝

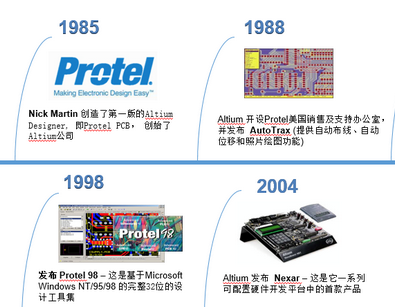

從Cadence到Altium Designer的轉換,為何設計中面臨越來越多挑戰

本篇文章主要介紹了PCB項目在不同開發平臺之間進行轉換的相關信息。Altium Designer 對基于不同開發平臺開發的PCB項目都可以進行無縫轉換,...

Cadence如何建立PCB?Cadence建立PCB步驟詳解

Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設計的方方面面,包括ASIC 設計、FPGA 設計和PCB 板設計。Cadence 在仿真、...

Allegro 擁有完善的 Constraint 設定,用戶只須按要求設定好布線規則,在布線中消除所有 DRC 就可以達到布線的設計要求,從而節約了煩...

Cadence發布業界首款已通過產品流片驗證的Xcelium并行仿真平臺

2017年3月1日,上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日發布業界首款已通過產品流片的第三代并行仿真平臺Xceli...

應對復雜SoC設計,Cadence發布Tempus時序Signoff解決方案

Cadence益華電腦總裁兼執行長陳立武表示:“在當今復雜SoC上達成設計收斂還要滿足上市時間要求,堪稱為一項艱巨的挑戰。我們開發了Tempus時序si...

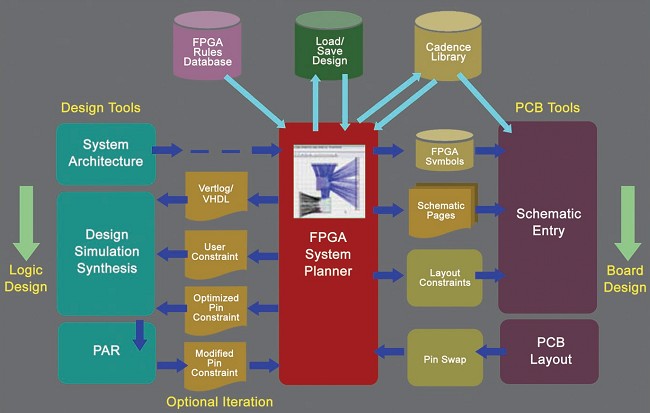

可編程邏輯廠商逐步開始從可編程邏輯芯片供應商向可編程邏輯系統商完成華麗轉身,正對EDA工具供應商提出更高的要求。鑒于日益升溫的FPGA市場,EDA業者加...

Cadence FSP:FPGA-PCB系統化協同設計工具介紹

Cadence FPGA System Planner(FSP)是一款完整性高的FPGA-PCB系統化協同設計工具。此次主要為大家介紹FPGA Syst...

ARM和Cadence協調Cortex-A9及A15的封裝設計工作

英國ARM和美國鏗騰設計系統(Cadence Design Systems)宣布,兩公司在ARM處理器內核“Cortex-A”系列的封裝設計(Harde...

CADENCE PCB設計解決方案能為解決與實現高難度的與制造密切相關的設計提供完整的設計環境,該設計解決方案集成了從設計構想至最終產品所需要的一切設計流程,

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |