能夠對這些數據進行處理。以下兩個例子說明了FPGA的I/O結構的發展。源同步接口在源同步接口中,發送器芯片發送數據字和數據采樣時鐘至接收器。接收器芯片使用時鐘來采集數據。從理論上說,源同步接口的速度

2018-11-26 11:17:24

,顯示接口只有6bit 的RGB接口和HDMI接口,無LVDS接口。但像性能更強大一點的全志T3和瑞芯微RK32x8平臺等,就內部集成專門的LVDS接口,不用再橋接一片轉換IC。

在實際應用中,通常我們

2023-06-05 17:31:08

)。從這些產品的數據表中我可以看出,對于大多數上述FPGA來說,這應該是可行的。然而,該設計可以使用比標準1.25V共模低的共模電壓。這可能是600mV的共模電壓。當共模電壓從標稱值1.25V降低時,FPGA上LVDS接收器的速度是否會降低?

2020-06-16 08:44:15

保證數據的正確讀取,如圖2所示。又由于DSP內部數據是32位的長字,所以寫入接收緩存前應該用一組D觸發器將數據進行32bit對齊,這里注意DSP鏈路口先傳輸32位數據中的低8位。 (2)控制部分:由

2019-06-19 05:00:08

保證數據的正確讀取,如圖2所示。又由于DSP內部數據是32位的長字,所以寫入接收緩存前應該用一組D觸發器將數據進行32bit對齊,這里注意DSP鏈路口先傳輸32位數據中的低8位。(2) 控制部分:由令牌

2018-12-04 10:39:29

可以分析一下這個接口的時序要求,然后對其進行約束。這個輸出的信號,其實是很典型的源同步接口,它的時鐘和數據都是由FPGA來驅動產生的。一般的源同步接口的寄存器模型如圖8.25所示。在我們的這個系統中

2015-07-29 11:19:04

!!!電子發燒友以后將呈現更多精彩紛呈的技術沙龍,期待大家的參與!活動詳情源同步設計極大地簡化時序參數,解決了管理高速信號中延遲的難題,卻帶來時序約束和分析難題,那么問題來了,如何來解決這個問題呢

2014-12-31 14:25:41

)LVDS差分對組成。四對轉換為21個并行數據位,五對轉換為28個并行數據位。注意,在時鐘上升沿和字邊界之間有一個2位偏移。每個字節有7位長。圖1 7:1LVDS接口每個通道包括一個串行LVDS數據對和一個源

2019-12-11 09:51:59

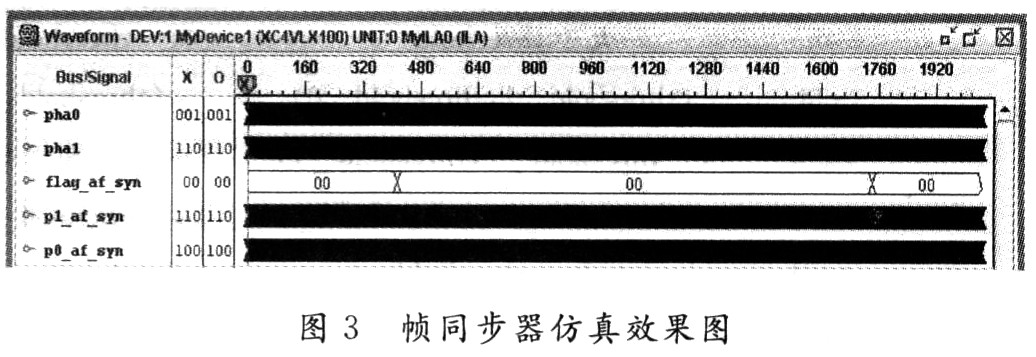

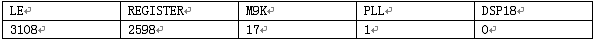

FPGA設計中幀同步系統的實現數字通信時,一般以一定數目的碼元組成一個個“字”或“句”,即組成一個個“幀”進行傳輸,因此幀同步信號的頻率很容易由位同步信號經分頻得出,但每個幀的開頭和末尾時刻卻無法由

2012-08-11 16:22:49

FPGA設計中幀同步系統的實現數字通信時,一般以一定數目的碼元組成一個個“字”或“句”,即組成一個個“幀”進行傳輸,因此幀同步信號的頻率很容易由位同步信號經分頻得出,但每個幀的開頭和末尾時刻卻無法由

2012-08-11 17:44:43

JESD204BSubclass1工作模式,通過FMC接口與高性能FPGA的GTH接口相連接收ADC采樣后的數據,最終通過PCIE金手指與PC端進行傳輸。5、JESD204B協議中自同步加解擾電路設計與實現作為JEDEC最新修訂

2019-12-03 17:32:13

(時鐘嵌入在比特流中,利用恢復時鐘技術CDR)b.不用擔心信道偏移(信道對齊可修復此問題,RX端FIFO緩沖器)c.不用再使用大量IO口,布線方便(高速串行解串器實現高吞吐量)d.多片IC同步方便

2019-12-04 10:11:26

的應用越來越廣泛。介紹了基于FPGA的LVDS_TX模塊在DAC系統中的應用,實現了高速LVDS數據的傳輸,應用時應要注意:LVDS并串轉換時,數據bit位的順序問題,正確相應的輸入數據排列才能得到正確的輸出

2019-05-28 05:00:03

我正在使用artix xc7a100t,我需要fpga生成lvds iostandard來驅動fpga之外的設備。我把差分時鐘放在15的bank的mrcc中,bank15的vcco可以是3.3V

2020-08-14 09:22:43

lvds如何用fpga或是matlab實現

2014-01-15 15:20:12

求助lvds如何用fpga或是matlab實現

2014-01-15 15:18:06

lvds如何用fpga,matlab實現?求助

2014-01-14 21:41:01

我研究了在設計中實現HDMI,DVI和Displayport的可行性。在這種設計中,FPGA將具有用于HDMI,DVI和DisplayPort的接收器,以接收來自外部源的信號。現在我不確定以下

2019-02-19 10:09:29

1、在FPGA中實現串口協議的設計在FPGA中實現串口協議,通過Anlogic_FPGA開發板上的“UART2USB”口接收從計算機發來的數據。實驗設計思路UART串口是一種類似于USB、VGA

2022-07-19 11:09:48

Xilinx FPGA上的JESD204B發送器和接收器框圖。發送器/接收器通道實現加擾和鏈路層;8B/10B編碼器/解碼器和物理層在GTP/GTX/GTHGbit 收發器中實現。圖4. 使用Xilinx

2018-10-16 06:02:44

,這個選通信號也可以稱為源同步時鐘信號。源同步時鐘系統中,數據和源同步時鐘信號是同步傳輸的,我們保證這兩個信號的飛行時間完全一致,這樣只要在發送端的時序是正確的,那么在接收端也能得到完全正確的時序。整個

2014-12-30 13:54:22

至A2.在MDK中修改MSP的值使MSP滿足8字節對齊3.全速運行程序,觀察buf中的字符為 1.234 結果正確4.回到第2步,修改MSP使之只滿足4字節對齊而不滿足8字節對齊5.全速運行程序,觀察

2015-01-19 11:43:10

咨詢一個初級A/D問題:AD9684中DCO時鐘的用法(FPGA控制)。AD9684與FPGA用LVDS模式接口互聯時,FPGA端如何使用?手冊中沒有詳細說明,是DCO上升沿捕獲數據,作為數據同步

2023-12-13 09:01:52

DSFH混合擴頻接收機解擴及同步技術FPGA實現 .docx

2012-08-11 09:45:43

和 CMOS 接口提供的優勢。有了 JESD204B,您無需再:使用數據接口時鐘(嵌入在比特流中)擔心信道偏移(信道對齊可修復該問題)使用大量 I/O(高速串行解串器實現高吞吐量)擔心用于同步多種 IC

2018-09-13 14:21:49

NUC980的網口的發送描述符的緩沖區地址要求 4字節對齊的問題,因為我用的協議棧里面要求IP數據段4字節對齊,加上以太網14字節,如果發送緩沖區要求4字節對齊,帶來的問題我必須要完成一次拷貝,不能把數據緩沖區直接發送

另外一個問題,我看接收緩沖區的地址好像沒有要求4字節對齊。

2023-06-27 07:34:15

把數據緩沖區直接發送

另外一個問題,我看接收緩沖區的地址好像沒有要求4字節對齊。

Receive Buffer Starting Address [31..0]

Transmit Buffer Starting Address [31..2]

2023-06-13 07:01:40

自己設計兩個板子,一個用于產生PN碼,通過數據現傳入另一個板子,然后在接收的板子中實現該PN碼的同步,然后輸出到示波器,對比產生的PN碼和輸出PN碼是否同步。 PN碼的同步過程該如何實現呀?一點不懂,大家可不可以推薦一些相關資料或者書籍,讓我學習學習,謝謝!!

2016-04-10 14:48:05

我發現了一個應用筆記,描述了Virtex 4中LVDS DDR接口的實現,它使用了位滑動對齊和訓練序列來實現500Mb / s的數據速率。有沒有人能夠在不使用位滑動對齊和訓練模式的情況下在virex

2019-03-08 13:39:47

視頻信號(包括數據與時鐘,其中數據位寬16位,時鐘1位,最高工作頻率148.5MHZ).2.遇到的問題時鐘相對于數據的延時,也就是信號的建立與保持時間在經過FPGA后出現偏移。造成后端的DA不能正確的采集到數據。

2014-02-10 16:08:02

我知道數據儲存的起始地址%對齊字節(N)=0才行,但是我不明白有兩點問題1:UCOSIII的系統中的浮點數打印任務的堆棧大小要8字節對齊,float無論在32位機還是64位機中都是4字節大小, 可為

2020-04-23 00:21:44

大家好這是我第一次發布東西,我正在設計一個lvds發射器,我需要知道virtex-6 FPGA中lvds接收器的輸入電容能夠測試我的發射器嗎?我查看了數據手冊,發現輸入芯片電容為8pF,這與virtex-6中lvds接收器的輸入電容相同。提前致謝易卜拉欣·艾哈邁德

2020-06-11 06:07:12

作者:黃忠老師(張飛實戰電子高級工程師)C語言是一種高級語言,在大多數情況下C語言的代碼是和具體的處理器體系結構無關的。然而,在嵌入式系統的編程中,有可能涉及對內存的具體操作。在大小端和內存對齊

2021-07-30 09:34:18

必須適當地與所有數據位的到達保持同步。如果接收器使用發射時鐘,可能會要求延遲從發送端到接收端的時鐘信號。 有時設計可能需要一個更高的時鐘頻率來運行FPGA上的邏輯。但是,只有低頻率輸出的時鐘源可以用

2020-04-25 07:00:00

很好的應用筆記,用于在spartan fpgas中實現serdes但是對Virtex5沒什么用?任何人都可以指出我使用V5 fpgas正確實現serdes(lvds)的一些資源。我將從主設備向10個從

2020-07-13 15:54:49

嗨,每個人,我都使用V4 FPGA從CMOS接收LVDS數據。同時,CMOS輸出一個LVDS時鐘資源'dck'作為同步時鐘。數據在上升沿和下降沿傳輸,如下圖所示。 我清楚地知道在verilog

2020-04-20 10:21:22

使用的開發環境為MAPLAB X IDE 1字節對齊的實現如下#pragma pack(1)typedef union{uint8_t buf[21];struct Message{uint8_t repeat : 2;uint8_t msgid : 6;...

2021-11-24 06:21:41

同一個時鐘域中,或者來自不同的源(即使它們具有相同的時鐘頻率)在將信號同步到 FPGA 或不同的時鐘域時,有多種設計可供選擇。在xilinx fpga中,最好的方法是使用xilinx參數化宏,創建這些

2022-10-18 14:29:13

把數據緩沖區直接發送

另外一個問題,我看接收緩沖區的地址好像沒有要求4字節對齊。

Receive Buffer Starting Address [31..0]

Transmit Buffer Starting Address [31..2]

2023-09-04 06:44:53

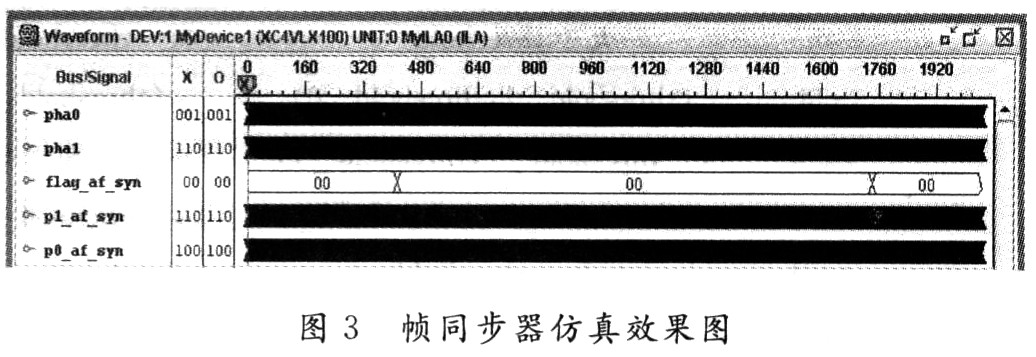

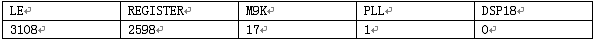

的FPGA實現,通過將Verilog文件導入到modelsim仿真可知,上述設計能正確的完成同步、跟蹤。當然如何快速的實現同步跟蹤一直是人們熱衷的話題。在FPGA實現中常用資源換取速度。在這里,我們可以

2015-10-16 21:39:57

判斷產品的功能是否正常。設計中的板卡為該遙測信號模擬源的組成部分,主要用于測試產品的LVDS總線協議的功能是否正常。由于待測信號的特殊應用,要求板卡能夠接收200 Mbit·s-1內的高速串行數據并能

2019-07-18 06:35:45

中優勢明顯。FPGA資源豐富、速度快、開發方便快捷,因此在高速數據通信中應用廣泛。DDS頻率合成技術通過頻率控制字、相位控制字及參考時鐘的控制來實現輸出信號的調頻調相,并且輸出信號具有頻率轉換快、頻率

2012-09-06 12:40:54

的協議會定義特殊的碼型(常見的碼型如8B/10B編碼中的K28.5)用于字對齊處理。另一些帶源同步時鐘的LVDS接口,通常會利用低頻的源同步時鐘來攜帶字對齊信息,用于接收端的正確恢復。FPGA對上述兩種

2019-07-29 07:03:50

在可靠的通信系統中,要保證接收端能正確解調出信息,必須要有一個同步系統,以實現發送端和接收端的同步,因此同步提取在通信系統中是至關重要的。

2019-09-19 07:28:51

在可靠的通信系統中,要保證接收端能正確解調出信息,必須要有一個同步系統,以實現發送端和接收端的同步,因此同步提取在通信系統中是至關重要的。一個簡單的接收系統框圖如圖1所示。

2019-09-17 06:28:08

AD接口:時鐘對齊、根據幀同步實現串轉并數據對齊.本人非常熟悉Virtex-5/Virtex-6/7 Series FPGA的內置SERDES模塊,包括ISERDES,OSERDES,IODELAY

2014-03-01 18:47:47

目前正在做一個AD9970+CCD的項目,通過FPGA接收并解析AD9970輸出的LVDS差分串行數據。由于AD9970輸出的是串行比特位流,FPGA首先需要判斷一個data word在 bit

2024-01-01 06:36:32

Hello我想使局部數組地址128字節對齊,不知道在C6000平臺,CCS5.5上,能否實現。全局變量,用DATA#pragma DATA_ALIGN(arr,128),但是不知道局部數組如何實現

2019-08-27 10:22:30

∑一△ADC原理是什么?LVDS收發器標準及其原理是什么?如何利用LVDS接收器去實現ADC?

2021-06-03 06:23:35

Spartan-3 FPGA系列如何僅通過在接收器數據通路中加入一個倒相器即可避免大量使用過孔?如何利用Spartan-3 FPGA進行LVDS信號倒相設計?

2021-05-06 07:30:25

在串行數據傳輸的過程中,如何在FPGA中利用低頻源同步時鐘實現LVDS接收字對齊呢?

2021-04-08 06:39:42

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。那么該如何在低端FPGA中實現DPA的功能呢?

2021-04-08 06:47:08

我們建議的設置如下:希望ADC工作在200 MHz,采樣速率為200 MSPS。最初,為了避免FPGA內部操作和ADC數據之間的同步問題,我們計劃從FPGA驅動ADC輸入時鐘。現在我們擔心高采樣率

2020-08-25 09:23:10

相對于FPGA來說,邊沿對齊源同步輸入端口,指的是FPGA同時接收外部器件傳過來的數據和時鐘信號,并且用接收到的時鐘信號去鎖存傳過來的數據。模型如下圖所示:對此模型進行約束,分下面幾個步驟:1.對時

2014-12-25 14:28:06

嗨,我需要通過FPGA內部的源同步信號,我該怎么做才能確保來自FPGA的信號在clk和數據之間具有正確的時序相位關系。與輸入的相同。我可以復制兩個輸出。請指教。

2020-05-22 14:19:26

測控系統中B碼同步技術的FPGA實現

2012-08-06 11:48:16

你好,我目前正在設計一個LVDS接收器和DAC ASIC。DAC是12位。我需要使用來自FPGA / Eval板的LVDS信號進行測試。任何人都可以推薦我可以用來測試我的ASIC的評估板或FPGA嗎?謝謝。問候,尼基爾

2019-09-19 12:27:09

我目前想要使用FPGA上自帶的LVDS模塊實現FPGA之間的通信。首先我測試了一塊FPGA自收自發,我的全局時鐘25M,數率200M,4個通道,8位因子,然后測試中我發現必須調整接收模塊的輸入

2014-04-03 23:27:32

使用外部時鐘CLK的數據接收數據?還是CLK需要 在FPGA上使用PLL再同步一下才能供給FPGA接收數據使用?

2012-07-16 09:03:27

在開發中遇到一個問題,input輸入框的內容需要進行右對齊,發現設置樣式text-align根本起不到效果,官方開發文檔也沒有具體的參照。請問,在JS組件input中如何才能實現內容對齊(或左或中或右)?是否支持此樣式屬性?

2022-03-29 14:43:26

目前正在做一個AD9970+CCD的項目,通過FPGA接收并解析AD9970輸出的LVDS差分串行數據。由于AD9970輸出的是串行比特位流,FPGA首先需要判斷一個data word在 bit

2019-03-01 14:09:48

大家好,C2000成員TMS320F28335在CCS3.3下是2字節對齊的,能不能改為1字節對齊?怎么改呢?再者,有沒有在F28335下成功移植了ucos+lwip的呢?

2018-08-20 06:41:43

#define PACK_STRUCT_END#define PACK_STRUCT_FIELD(x) x這幾個宏定義在這其實是啥也沒做 ,但在LWIP中不是要求禁止編譯器的字對齊嗎?我知道在keil中是使用的 #define PACK_STRUCT_BEGIN __packed

2019-11-06 22:36:45

我使用的是AD9681。由于硬件設計的問題,不能將FCO輸出的頻率作為FPGA中的LVDS接收模塊的輸入時鐘,導致接收到的數據不正確(FPGA中接收到的數據跟AD9681輸入信號不一致)。請問應該怎么使用AD9681輸出的DCO、FCO,使得接收到正確數據?

2018-10-08 16:48:55

我使用的是ad9681。由于硬件設計的問題,不能將FCO輸出的頻率作為fpga, fpga, fpga中的lvds 升數接收模塊的輸入時鐘,導致接收到的數據不正確(fpga, fpga, fpga中

2023-12-20 07:13:36

不同的頻率發送數據,自動檢測邏輯被用來檢測正在傳送的是哪種分辨率,并配置PCS以便在SERDES鎖相環中實現鎖定。 接收同步 一旦10位數據在FGPA中,執行上述定義的三個步驟(字節對齊、通道

2019-06-06 05:00:34

本文提出了一種基于詞性的判別函數,用來自動識別句子對齊結果的正確性。通過反向采用基于長度的對齊算法,糾正了初步對齊產生的連續性錯誤。該方法節省了人力,同時提

2009-09-18 10:56:31 8

8 本文主要闡述了在某雷達系統中為實現偽碼對齊,所采用的滑動控制方法的原理及在FPGA芯片上的實現。

2010-03-02 16:04:22 13

13 摘要:研究采用編碼擴頻的DS/FH混合擴頻接收機的核心模塊——同步及解擴部分的FPGA實現結構。將多種專用芯片的功能集成在一片大規模FPGA芯片上,實現了接收機的

2006-03-11 13:36:29 1496

1496

一種高速幀同步和相位模糊估計的方法及其FPGA實現

摘要:提出僅依靠接收符號和本地同步碼快速確定MPSK調制符號的幀同步,并同時估計其相位模糊值的計算方法,給

2010-01-27 09:38:17 1278

1278

在低成本FPGA中實現動態相位調整

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。ALTERA

2010-03-25 11:45:07 2338

2338

本文闡述了主同步搜索的改進型算法,并且針對這種算法提出了基于片上RAM 的實現方式,最大程度地節省了FPGA 的硬件資源,為WCDMA 同步的FPGA 實現提供了很好的解決方案。這種技術可

2011-05-14 16:45:53 30

30 本文描述TI 的客戶在不用 LVDS (低壓差分信號傳輸)驅動器時,如何采用LVDS 接收器于其他驅動器配合解決一些簡單的問題。

2011-07-18 15:21:36 30

30 介紹了LVDS技術的原理,對LVDS接口在高速數據傳輸系統中的應用做了簡要的分析,著重介紹了基于FPGA的LVDS_TX模塊的應用,并通過其在DAC系統中的應用實驗進一步說明了LVDS接口的優點。

2012-01-11 10:46:04 99

99 (Xilinx)FPGA中LVDS差分高速傳輸的實現

2017-03-01 13:12:04 64

64 為了能在GPS接收端獲取正確導航電文,研究了CJPS接收機位同步、幀同步的基本原理和實現方式。提出一種采用FPGA來實現位同步、幀同步系統的設計方案。使用Xilinx開發軟件,通過Verilog代碼

2017-11-07 17:13:39 10

10 超高速ADC通常采用LVDS電平傳輸數據,高采樣率使輸出數據速率很高,達到百兆至吉赫茲量級,如何正確接收高速LVDS數據成為一個難點。本文以ADS42LB69芯片的數據接收為例,從信號傳輸和數據解碼兩方面,詳述了實現LVDS數據接收應該注意的問題及具體實現方法,并進行實驗測試、驗證了方法的正確性。

2017-11-17 10:40:01 6131

6131 階段。針對GPS信號的BPSK調制和強度微弱等特點,模擬GPS 接收機基帶數字信號處理過程,首先介紹了科斯塔斯(Costas)接收機的工作原理,分析研究了基于FPGA的軟件無線電載波同步技術的實現方法,并采用Costas 環實現了載波同步,性能測試驗證了設計的正確性和可行性。

2017-11-17 12:01:01 5752

5752

上千M。使用lvds來接收高速ADC產生的數據會很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR這種資源在FPGA的IOB中多得是(每個IO都對應有,最后具體介紹),根本不擔心使用。

2018-06-30 10:23:00 21423

21423

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自帶有DPA電路,但低端的FPGA,如CYCLONE(r)系列中是沒有的。下面介紹如何在低端FPGA中實現這個DPA的功能。

2018-02-16 17:32:33 10345

10345

,采集卡上使用DS90CR288進行并轉串處理,這種方式占用FPGA管腳資源多。當傳輸24bit RGB信號時,需要使用24(信號)+4(同步控制)+1(時鐘)=29個管腳,而使用lvds傳輸,使用altlvds_tx核,只需要5對lvds信號即可,共占用10個管腳。

2020-12-30 16:57:27 24

24 基于FPGA的GPS接收機實現說明。

2021-04-09 14:01:04 51

51

電子發燒友App

電子發燒友App

評論