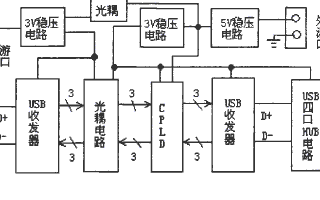

摘要:如果必須隔離一個與PC機連接的設備,人們很自然地會選擇USB接口。USB廣泛的工業(yè)支持和簡易結(jié)構(gòu)(USB電纜僅有4條線)使其成為一種通用的PC接口。USB控制器配合SPI接口的嵌入式系統(tǒng)可以很容易地實現(xiàn)電氣隔離。SPI接口由簡單的單向信號線構(gòu)成,可在任何速率下運行。

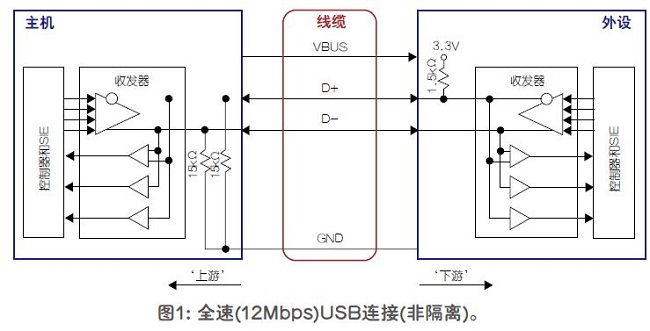

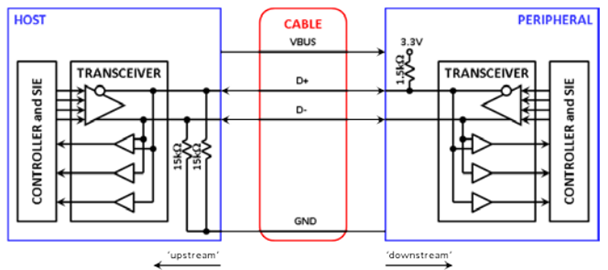

USB連接器包含四條線:2條用于電源供電(VBUS和GND),2條用于USB數(shù)據(jù)傳輸(D+和D-)。VBUS提供5V電源,電流可達500mA。D+和D-為雙向信號線,信號傳輸速率為12Mbps (每位83ns)。D+和D-信號電平為3.3V。

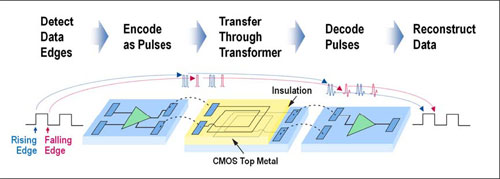

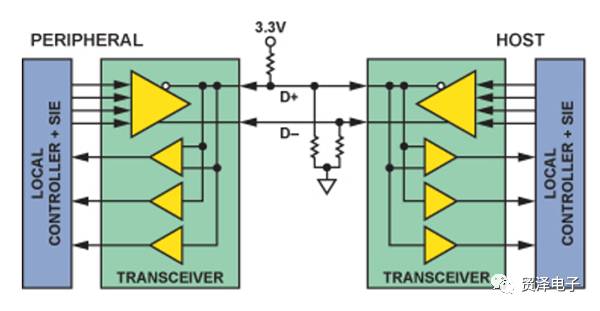

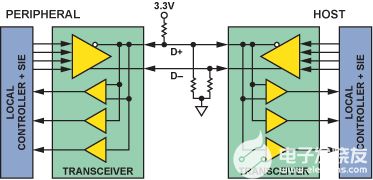

圖1. 一個USB外設可以在三個位置隔離:位置1,USB總線;位置2,收發(fā)器接口;位置3,應用接口。現(xiàn)在絕大部分設計中,SIE和收發(fā)器集成在一起,無法在位置2實現(xiàn)隔離。

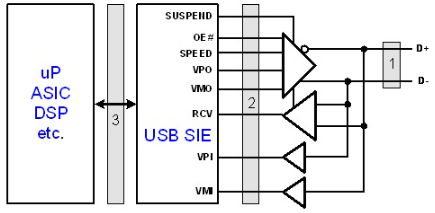

USB外設結(jié)構(gòu)框圖如圖1所示。從右至左來看該圖,USB收發(fā)器連接至D+和D-,發(fā)送或接收數(shù)據(jù)都由OE (輸出使能)控制。中間單元是USB串行接口引擎(SIE),其作用是將總線信號(由收發(fā)器發(fā)送和接收)轉(zhuǎn)換成字節(jié)數(shù)據(jù)或USB信號,以供USB外設使用。最左邊的單元是應用電路,可能是微處理器、專用集成電路或數(shù)字信號處理器(DSP)。

標記1、2和3的灰色的長方形,顯示了放置光耦、隔離USB設備與主計算機的三種可能位置。

圖2. 示波器顯示USB D+和D-信號(圖1中的位置1),83ns的位時間和嚴格匹配的上升/下降時間,使光耦隔離很難保持信號的保真度。D+和D-是雙向信號,使得隔離更加復雜。

符合這些要求的理想接口是SPI (串行外圍設備接口),該接口由Motorola定義,現(xiàn)已用于許多半導體器件。由于其簡單、高效,SPI成為非常流行的接口。

表1給出了SPI接口的4個信號。SPI為主從式接口,主接口啟動并控制與一個從接口的通信。主機提供從機選擇信號(SS#)和串行時鐘(SCLK),用于同步數(shù)據(jù)傳輸。SPI接口具有四種時鐘模式,具體由2個模式信號CPOL (時鐘極性)和CPHA (時鐘相位)決定,這些信號表示為(CPOL, CPHA)。

圖3描述了微處理器與SPI從設備間的SPI數(shù)據(jù)傳輸,圖3采用最常見的SPI模式(0,0)。在(0,0)模式中,時鐘在無效狀態(tài)下為低電平。SPI主機在第一個SCLK上升沿之前將MOSI數(shù)據(jù)準備好。SPI數(shù)據(jù)在SCLK下降沿變化,主從設備均在上升沿對數(shù)據(jù)進行采樣。

圖3. 工作在模式(0,0)的SPI接口,如果SCLK信號為低有效(靜止狀態(tài)為高),同樣的接口也可工作在模式(1,1)。這些低頻信號易于進行光隔離。

很容易在微處理器上實現(xiàn)SPI接口,即使是沒有包含硬件SPI單元的微處理器。SPI接口只需要微處理器通過4個通用IO引腳(GPIO)構(gòu)建圖3信號,子程序可通過直接觸發(fā)IO引腳的讀寫操作實現(xiàn)。

圖4顯示了USB外設控制器使用SPI接口時,SPI與USB的數(shù)據(jù)速率差異。圖中,主控制器實現(xiàn)USB鍵盤功能,并周期性地點亮一個LED燈。圖5所示SPI數(shù)據(jù)傳輸可由LED閃爍指示(觸發(fā)一個輸出位);USB通信為USB主機請求鍵盤數(shù)據(jù)。

兩種總線之間數(shù)據(jù)速率的差異很顯著。頻率較低的單向SPI信號比12MHz的雙向USB總線信號更易于隔離。SPI信號使隔離方法變得非常簡單,能在任何頻率下運行,適用于各種光隔離器。

圖4. SPI數(shù)據(jù)速率和USB信號速率的比較。SPI信號更易于通過光耦傳輸。

系統(tǒng)如何按照圖4使得存在巨大差異的USB控制器的SPI總線速率與USB信號速率協(xié)調(diào)工作呢?USB的優(yōu)點之一是通過內(nèi)部流量控制實現(xiàn)“自節(jié)流”。通過使用“NAK" (非應答)握手信號完成信號流量控制。由此,外圍設備告知主機請求的數(shù)據(jù)還沒準備好,主機應稍后再試。

圖5. USB總線的低速外圍設備對主機IN數(shù)據(jù)請求的響應。主機在信息包362-364中發(fā)出數(shù)據(jù)請求。外圍設備發(fā)出信息包420表示數(shù)據(jù)準備就緒。插入的IN-NAK信息包為USB流量控制,外圍設備在數(shù)據(jù)準備就緒之前始終響應NAK。

圖5顯示了USB數(shù)據(jù)傳輸?shù)牧髁靠刂茩C制。從信息包362開始,主機發(fā)出Get_Descriptor-Configuration請求。信息包363從第二個字節(jié)到最后一個字節(jié)的09表示主機請求外設發(fā)送9個字節(jié)的數(shù)據(jù)。外設在信息包364中對請求應答,然后對請求進行譯碼,并將請求數(shù)據(jù)裝入數(shù)據(jù)FIFO的末端0處。低速外圍設備需要一定時間才會應答這個請求,低速SPI總線會進一步延長響應時間。

988.667微秒后(信息包364后),主機在信息包366中開始請求發(fā)送數(shù)據(jù)。外設沒有數(shù)據(jù),USB硬件自動產(chǎn)生NAK握手響應,表明“忙碌中,稍后再試”。主機在信息包368中重試,并從外設獲得同樣的NAK應答。這個IN-NAK過程一直持續(xù)到信息包419,外設最終完成請求數(shù)據(jù)的裝載,并在數(shù)據(jù)末端0處準備數(shù)據(jù)發(fā)送。此時,外設在信息包420中將以9字節(jié)的數(shù)據(jù)包響應取代NAK,主機在信息包421中應答。

IN-NAK響應(圖5中用虛線矩形標出)可能發(fā)生多次,這意味著SPI接口的工作速率沒有最低限制。允許設計者調(diào)整SPI數(shù)據(jù)速率,以適應高性價比設計中的光耦選擇。

詳細電路圖(PDF, 204kB)

圖6. 隔離USB設計原理圖,左邊部分由USB總線自身供電,右邊部分使用隔離電源供電。在SPI接口處進行隔離,使得設計簡單,并且不受USB總線時序的影響。

圖6是利用Atmel?的低成本微處理器AtTiny13 (U6)、光耦HCPL-2531 (U3-5)和MAX3420E (U1)構(gòu)建,MAX3420E是帶有SPI接口的USB外設控制器。雖然U6不包含硬件SPI單元,通過對GPIO引腳進行“逐位控制”可以很容易地實現(xiàn)SPI接口。U1提供四個通用輸入、四個通用輸出引腳取代(加至) U6實現(xiàn)SPI接口的引腳。這個設計使用兩個輸出引腳驅(qū)動LED指示器D1和D2,一個輸入引腳連接至按鈕PB1。因為U1本身包含由SPI接口控制的IO引腳,這些IO與U6本質(zhì)上是隔離的,因此不需要額外隔離。

圖7. 在隔離接口兩側(cè)的SPI SCLK信號,上部:ISOVCC = 8.3V,ISOGND = 5V。下部:由USB供電:VCC = 3.3V,GND = 0V。

圖7顯示了隔離接口兩側(cè)的SCLK信號,兩條曲線的基線都在屏幕底部。上部曲線顯示由U6產(chǎn)生的SCLK信號,但有5V的偏移。

圖8. 隔離的SCK信號(上部)和處于MAX3420E側(cè)的SCK信號(下部),擴大比例顯示。

圖8是圖7放大比例后的圖形,用于說明光耦的性能。這個設計中選擇的電阻使光耦在起始位置有0.5μs的延遲。SCLK中間部分的短脈沖由U6驅(qū)動SCLK IO引腳的程序產(chǎn)生。U6的這部分程序如圖9所示。

圖9. AtTiny13對MAX3420E寄存器進行讀操作的匯編程序。在此可以調(diào)整SPI接口的時序以提高光耦的性價比。

在r4標號前,SCK信號驅(qū)動為低電平,然后再次驅(qū)動為高電平(SCLK_LO和SCLK_HI是匯編宏,不需要改變代碼就可以很容易對實際電路的IO引腳賦值)。

這兩個語句之間插入少量NOP指令,圖8中的窄脈沖可以變寬,由此,使用低速光耦(這意味著更低的成本)成為可能。這個方法證明在光隔離應用中使用SPI接口的靈活性。

概述

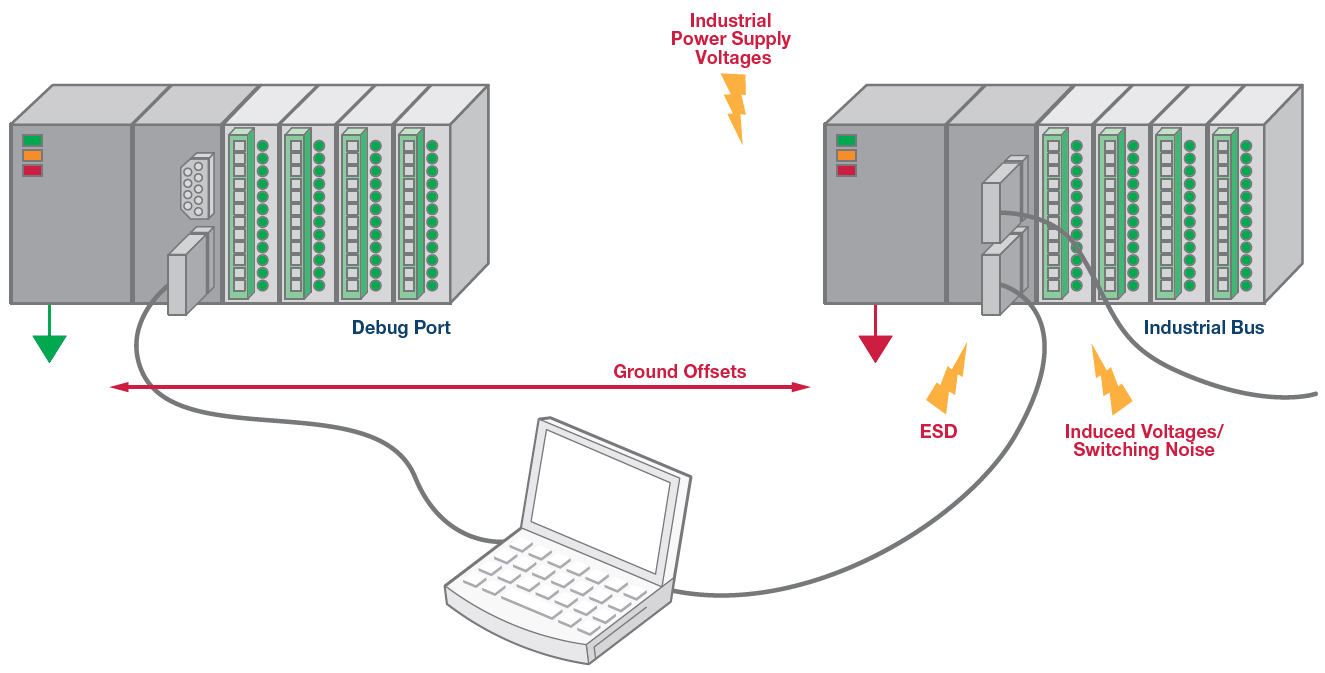

通用串行總線(USB)已經(jīng)成為外圍設備與個人計算機連接的標準方式。如果一個與PC連接的設備需要電氣隔離,USB將是一個很自然的選擇接口。USB的兩個著名的隔離應用是基于PC平臺的醫(yī)療設備和具有很大地電位差的工業(yè)應用。USB基礎信號

USB具有以下三種工作速率:- 低速,1.5Mbps

- 全速,12Mbps

- 高速,480Mbps

USB連接器包含四條線:2條用于電源供電(VBUS和GND),2條用于USB數(shù)據(jù)傳輸(D+和D-)。VBUS提供5V電源,電流可達500mA。D+和D-為雙向信號線,信號傳輸速率為12Mbps (每位83ns)。D+和D-信號電平為3.3V。

USB隔離的設計挑戰(zhàn)

圖1. 一個USB外設可以在三個位置隔離:位置1,USB總線;位置2,收發(fā)器接口;位置3,應用接口。現(xiàn)在絕大部分設計中,SIE和收發(fā)器集成在一起,無法在位置2實現(xiàn)隔離。

USB外設結(jié)構(gòu)框圖如圖1所示。從右至左來看該圖,USB收發(fā)器連接至D+和D-,發(fā)送或接收數(shù)據(jù)都由OE (輸出使能)控制。中間單元是USB串行接口引擎(SIE),其作用是將總線信號(由收發(fā)器發(fā)送和接收)轉(zhuǎn)換成字節(jié)數(shù)據(jù)或USB信號,以供USB外設使用。最左邊的單元是應用電路,可能是微處理器、專用集成電路或數(shù)字信號處理器(DSP)。

標記1、2和3的灰色的長方形,顯示了放置光耦、隔離USB設備與主計算機的三種可能位置。

圖2. 示波器顯示USB D+和D-信號(圖1中的位置1),83ns的位時間和嚴格匹配的上升/下降時間,使光耦隔離很難保持信號的保真度。D+和D-是雙向信號,使得隔離更加復雜。

位置1

下列理由說明在USB總線上進行光耦隔離是不切實際的,見圖2:- 信號速率為12MHz,對于性價比較高的隔離器來說成本過高。

- D+和D-信號的傳輸延遲、偏差必須完全一致,使用光耦隔離器很難滿足一致性要求。

- 總線為雙向,而隔離器為單向,使光耦隔離更加復雜。而且對于一個使用集成收發(fā)器的外圍設備,無法得到OE信號(指示傳輸方向)。

位置2

使用外置收發(fā)器的USB外設其收發(fā)器接口暴露在外部,對于這些單向信號可以考慮使用光耦隔離。盡管如此,這個位置和位置1有著相同問題:數(shù)據(jù)速率過高,而且有多路12MHz速率的信號需要隔離。VPO、VMO、RCV、VPI和VMI信號都運行在12MHz速率,必須嚴格保持這些信號傳輸延遲、偏差的一致性。此外,現(xiàn)代USB設計中將SIE和收發(fā)器集成在同一芯片,也很難獲得這個接口。位置3

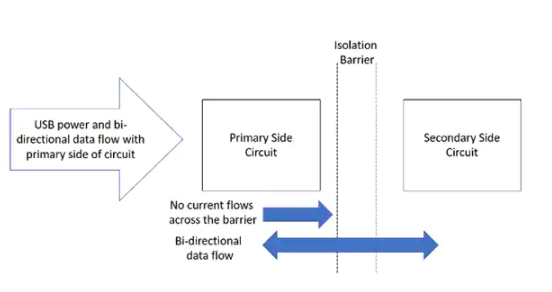

這是最有希望實現(xiàn)隔離的位置,這個接口工作速率低于USB數(shù)據(jù)速率和線速率,且該接口可以完全由單向信號構(gòu)成。事實上,一個理想的接口應該只使用少量單向信號,且這些信號的數(shù)據(jù)速率遠低于USB的12MHz信號速率。符合這些要求的理想接口是SPI (串行外圍設備接口),該接口由Motorola定義,現(xiàn)已用于許多半導體器件。由于其簡單、高效,SPI成為非常流行的接口。

SPI基礎信號

表1. SPI信號| SPI Signal | Description | Comments |

| SS# | Slave Select | Selects the chip for data transmission, supplied by the master |

| MOSI | Master Out Slave In | Unidirectional data pin |

| MISO | Master In Slave Out | Unidirectional data pin |

| SCLK | Serial Clock | Serial clock, supplied by the master |

表1給出了SPI接口的4個信號。SPI為主從式接口,主接口啟動并控制與一個從接口的通信。主機提供從機選擇信號(SS#)和串行時鐘(SCLK),用于同步數(shù)據(jù)傳輸。SPI接口具有四種時鐘模式,具體由2個模式信號CPOL (時鐘極性)和CPHA (時鐘相位)決定,這些信號表示為(CPOL, CPHA)。

圖3描述了微處理器與SPI從設備間的SPI數(shù)據(jù)傳輸,圖3采用最常見的SPI模式(0,0)。在(0,0)模式中,時鐘在無效狀態(tài)下為低電平。SPI主機在第一個SCLK上升沿之前將MOSI數(shù)據(jù)準備好。SPI數(shù)據(jù)在SCLK下降沿變化,主從設備均在上升沿對數(shù)據(jù)進行采樣。

圖3. 工作在模式(0,0)的SPI接口,如果SCLK信號為低有效(靜止狀態(tài)為高),同樣的接口也可工作在模式(1,1)。這些低頻信號易于進行光隔離。

很容易在微處理器上實現(xiàn)SPI接口,即使是沒有包含硬件SPI單元的微處理器。SPI接口只需要微處理器通過4個通用IO引腳(GPIO)構(gòu)建圖3信號,子程序可通過直接觸發(fā)IO引腳的讀寫操作實現(xiàn)。

圖4顯示了USB外設控制器使用SPI接口時,SPI與USB的數(shù)據(jù)速率差異。圖中,主控制器實現(xiàn)USB鍵盤功能,并周期性地點亮一個LED燈。圖5所示SPI數(shù)據(jù)傳輸可由LED閃爍指示(觸發(fā)一個輸出位);USB通信為USB主機請求鍵盤數(shù)據(jù)。

兩種總線之間數(shù)據(jù)速率的差異很顯著。頻率較低的單向SPI信號比12MHz的雙向USB總線信號更易于隔離。SPI信號使隔離方法變得非常簡單,能在任何頻率下運行,適用于各種光隔離器。

圖4. SPI數(shù)據(jù)速率和USB信號速率的比較。SPI信號更易于通過光耦傳輸。

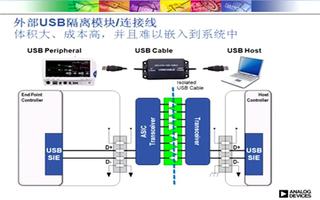

系統(tǒng)如何按照圖4使得存在巨大差異的USB控制器的SPI總線速率與USB信號速率協(xié)調(diào)工作呢?USB的優(yōu)點之一是通過內(nèi)部流量控制實現(xiàn)“自節(jié)流”。通過使用“NAK" (非應答)握手信號完成信號流量控制。由此,外圍設備告知主機請求的數(shù)據(jù)還沒準備好,主機應稍后再試。

SPI數(shù)據(jù)速率和USB NAK

圖5. USB總線的低速外圍設備對主機IN數(shù)據(jù)請求的響應。主機在信息包362-364中發(fā)出數(shù)據(jù)請求。外圍設備發(fā)出信息包420表示數(shù)據(jù)準備就緒。插入的IN-NAK信息包為USB流量控制,外圍設備在數(shù)據(jù)準備就緒之前始終響應NAK。

圖5顯示了USB數(shù)據(jù)傳輸?shù)牧髁靠刂茩C制。從信息包362開始,主機發(fā)出Get_Descriptor-Configuration請求。信息包363從第二個字節(jié)到最后一個字節(jié)的09表示主機請求外設發(fā)送9個字節(jié)的數(shù)據(jù)。外設在信息包364中對請求應答,然后對請求進行譯碼,并將請求數(shù)據(jù)裝入數(shù)據(jù)FIFO的末端0處。低速外圍設備需要一定時間才會應答這個請求,低速SPI總線會進一步延長響應時間。

988.667微秒后(信息包364后),主機在信息包366中開始請求發(fā)送數(shù)據(jù)。外設沒有數(shù)據(jù),USB硬件自動產(chǎn)生NAK握手響應,表明“忙碌中,稍后再試”。主機在信息包368中重試,并從外設獲得同樣的NAK應答。這個IN-NAK過程一直持續(xù)到信息包419,外設最終完成請求數(shù)據(jù)的裝載,并在數(shù)據(jù)末端0處準備數(shù)據(jù)發(fā)送。此時,外設在信息包420中將以9字節(jié)的數(shù)據(jù)包響應取代NAK,主機在信息包421中應答。

IN-NAK響應(圖5中用虛線矩形標出)可能發(fā)生多次,這意味著SPI接口的工作速率沒有最低限制。允許設計者調(diào)整SPI數(shù)據(jù)速率,以適應高性價比設計中的光耦選擇。

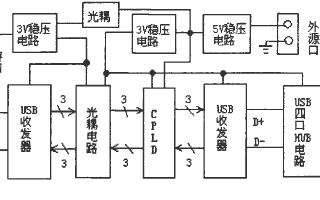

隔離USB設計實例

詳細電路圖(PDF, 204kB)

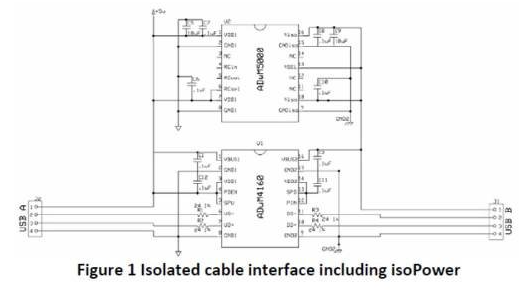

圖6. 隔離USB設計原理圖,左邊部分由USB總線自身供電,右邊部分使用隔離電源供電。在SPI接口處進行隔離,使得設計簡單,并且不受USB總線時序的影響。

圖6是利用Atmel?的低成本微處理器AtTiny13 (U6)、光耦HCPL-2531 (U3-5)和MAX3420E (U1)構(gòu)建,MAX3420E是帶有SPI接口的USB外設控制器。雖然U6不包含硬件SPI單元,通過對GPIO引腳進行“逐位控制”可以很容易地實現(xiàn)SPI接口。U1提供四個通用輸入、四個通用輸出引腳取代(加至) U6實現(xiàn)SPI接口的引腳。這個設計使用兩個輸出引腳驅(qū)動LED指示器D1和D2,一個輸入引腳連接至按鈕PB1。因為U1本身包含由SPI接口控制的IO引腳,這些IO與U6本質(zhì)上是隔離的,因此不需要額外隔離。

圖7. 在隔離接口兩側(cè)的SPI SCLK信號,上部:ISOVCC = 8.3V,ISOGND = 5V。下部:由USB供電:VCC = 3.3V,GND = 0V。

圖7顯示了隔離接口兩側(cè)的SCLK信號,兩條曲線的基線都在屏幕底部。上部曲線顯示由U6產(chǎn)生的SCLK信號,但有5V的偏移。

圖8. 隔離的SCK信號(上部)和處于MAX3420E側(cè)的SCK信號(下部),擴大比例顯示。

圖8是圖7放大比例后的圖形,用于說明光耦的性能。這個設計中選擇的電阻使光耦在起始位置有0.5μs的延遲。SCLK中間部分的短脈沖由U6驅(qū)動SCLK IO引腳的程序產(chǎn)生。U6的這部分程序如圖9所示。

圖9. AtTiny13對MAX3420E寄存器進行讀操作的匯編程序。在此可以調(diào)整SPI接口的時序以提高光耦的性價比。

在r4標號前,SCK信號驅(qū)動為低電平,然后再次驅(qū)動為高電平(SCLK_LO和SCLK_HI是匯編宏,不需要改變代碼就可以很容易對實際電路的IO引腳賦值)。

這兩個語句之間插入少量NOP指令,圖8中的窄脈沖可以變寬,由此,使用低速光耦(這意味著更低的成本)成為可能。這個方法證明在光隔離應用中使用SPI接口的靈活性。

電子發(fā)燒友App

電子發(fā)燒友App

評論