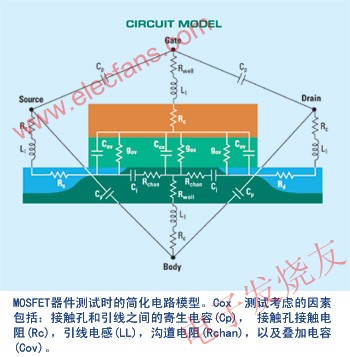

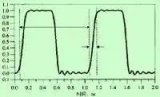

對(duì)于超薄介質(zhì),由于存在大的漏電和非線性,通過標(biāo)準(zhǔn)I-V和C-V測(cè)試不能直接提取氧化層電容(Cox)。然而,使用高頻電路模型則能夠精確提取這些參數(shù)。隨著業(yè)界邁向65nm及以下的節(jié)點(diǎn),對(duì)于高性能/低成本數(shù)字電路,RF電路,以及模擬/數(shù)模混合電路中的器件,這方面的挑戰(zhàn)也在增加。

減少使用RF技術(shù)的建議是在以下特定的假設(shè)下提出來: 假設(shè)RF技術(shù)不能有效地應(yīng)用,尤其是在生產(chǎn)的環(huán)境下,這在過去的確一直是這種情況。

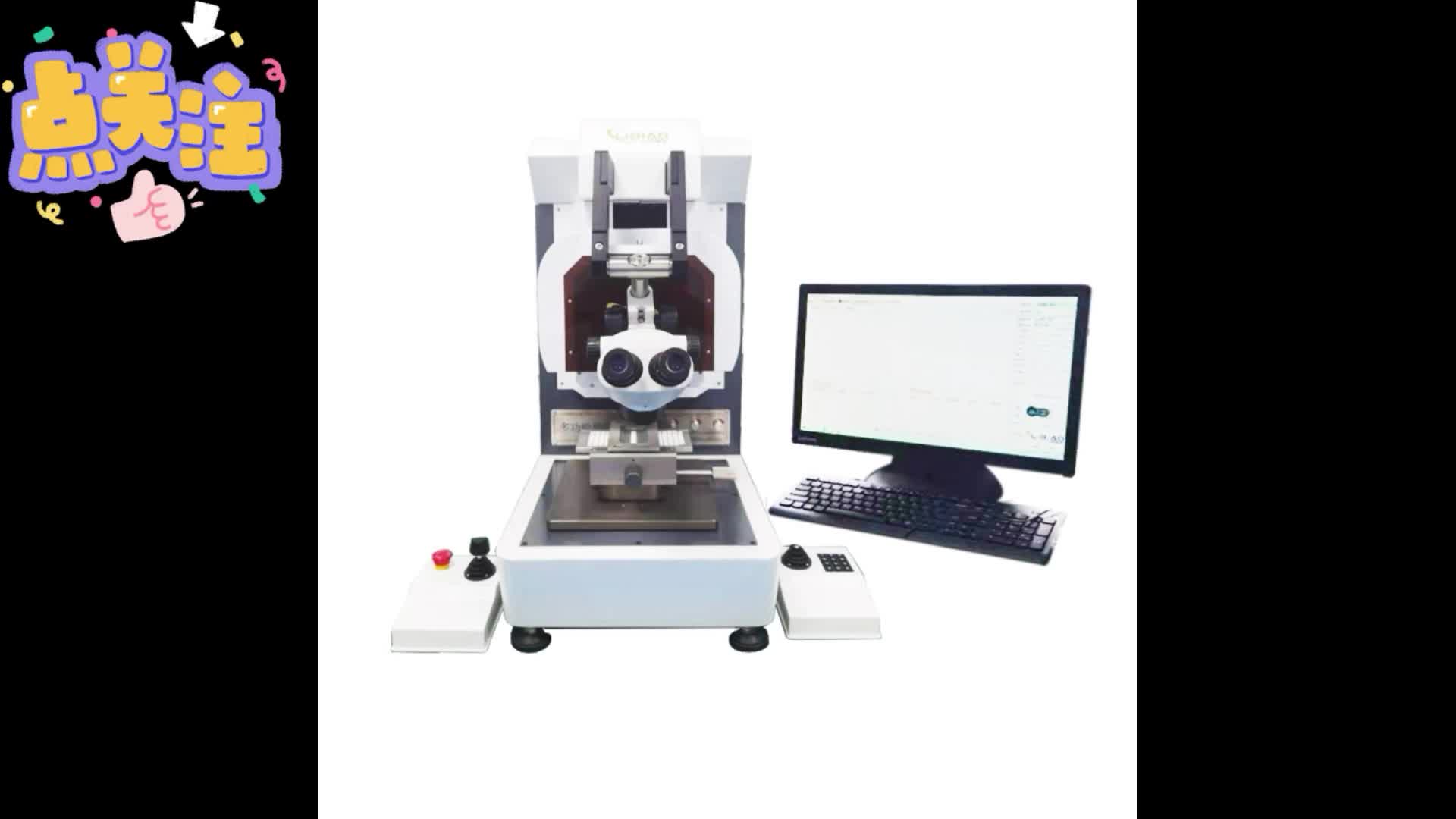

但是,現(xiàn)在新的參數(shù)測(cè)試系統(tǒng)能夠快速、準(zhǔn)確、可重復(fù)地提取RF參數(shù),幾乎和DC測(cè)試一樣容易。最重要的是,通過自動(dòng)校準(zhǔn)、去除處理(de-embedding)以及根據(jù)待測(cè)器件(DUT)特性進(jìn)行參數(shù)提取,探針接觸特性的自動(dòng)調(diào)整,已經(jīng)能夠?qū)崿F(xiàn)RF的完整測(cè)試。這方面的發(fā)展使得不必需要RF專家來保證得到好的測(cè)試結(jié)果。在生產(chǎn)實(shí)驗(yàn)室,根據(jù)中間測(cè)試結(jié)果或者操作需要,自動(dòng)探針臺(tái)和測(cè)試控制儀能夠完成過去需要人為干涉的事情。世界范圍內(nèi),已經(jīng)有7家半導(dǎo)體公司驗(yàn)證了這種用于晶圓RF生產(chǎn)測(cè)試的系統(tǒng)。

RF測(cè)試的應(yīng)用

無論你是利用III-V簇晶圓生產(chǎn)用于手機(jī)配件的RF芯片,還是利用硅技術(shù)生產(chǎn)高性能模擬電路,在研發(fā)和生產(chǎn)中預(yù)測(cè)最終產(chǎn)品的性能和可靠性,都需要晶圓級(jí)RF散射參數(shù)(s)的測(cè)量。這些測(cè)試對(duì)DC數(shù)據(jù)是重要的補(bǔ)充,相對(duì)于單純的DC測(cè)試,它用更少的測(cè)試卻能提供明顯更多的信息。實(shí)際上,一個(gè)兩通道的s參數(shù)掃描能同時(shí)提取阻抗和電容參數(shù),而采用常規(guī)DC方法,則需要分開測(cè)試,甚至需要單獨(dú)的結(jié)構(gòu)以分離工藝控制需要的信息。

功放RF芯片的功能測(cè)試是這種性能的另外一種應(yīng)用。這些器件非常復(fù)雜,然而價(jià)格波動(dòng)大。生產(chǎn)中高頻低壓的測(cè)試條件排除了通常阻礙晶圓級(jí)測(cè)試的功耗問題。也不存在次品器件昂貴的封裝費(fèi)用。已知良品芯片技術(shù)也可以應(yīng)用于晶圓級(jí)測(cè)試中,它能夠明顯改進(jìn)使用RF芯片的模塊的良率。

芯片制造商也可以利用晶圓級(jí)RF測(cè)試來提取各種高性能模擬和無線電路的品質(zhì)因數(shù)。比如濾波器、混頻器以及振蕩器。SoC(System-on-chip)器件制造商希望這種子電路測(cè)試技術(shù)能夠降低總體的測(cè)試成本。

130nm節(jié)點(diǎn)以下的高性能邏輯器件中,表征薄SiO2和高介電常數(shù)(high-k)柵介質(zhì)的等效氧化層厚度(EOT)非常關(guān)鍵。RF測(cè)試在介電層的精確建模方面扮演了重要角色,它能夠去除掉寄生元件,而這種寄生效應(yīng)在傳統(tǒng)的二元模型中將阻礙C-V數(shù)據(jù)的正確表示。中高頻 (MFCV, HFCV) 電容測(cè)量技術(shù)不可能因?yàn)閮x器而對(duì)測(cè)試引入串聯(lián)阻抗。

標(biāo)準(zhǔn)I-V/C-V測(cè)試面臨的挑戰(zhàn)

產(chǎn)品研發(fā)階段的設(shè)計(jì)工程師采用的仿真模型,包括從s參數(shù)數(shù)據(jù)提取的RF參數(shù)和I-V/C-V數(shù)據(jù)。先進(jìn)的設(shè)計(jì)工具要求的是統(tǒng)計(jì)模型,不是單個(gè)的一套參數(shù)。這使得良率和功能特性的最優(yōu)化成為可能。如果I-V和C-V參數(shù)基于統(tǒng)計(jì)結(jié)果,而RF不是的話,那么這個(gè)模型就是非物理的和不可靠的。

在有些情況下,比如電感、I-V和C-V信息的價(jià)值都非常有限。但是,Q在使用的頻率之下,作為電感表征和控制的參數(shù),則具有很高的價(jià)值。I-V和C-V測(cè)試中面臨的挑戰(zhàn)是要理解,什么時(shí)候它是產(chǎn)品特性的主要表征,什么時(shí)候不是。許多模擬和無線器件特性的只要表征參數(shù)是Ft和Fmax。理想的情況下,在第3諧波以外的使用情況下,它們是需要測(cè)量并提取出來的RF參數(shù)。對(duì)于數(shù)字和存儲(chǔ)器產(chǎn)品,只要器件的模型保持簡(jiǎn)化,那么I-V和C-V對(duì)于有源和無源器件來說都是很有價(jià)值的測(cè)量項(xiàng)目。前面提到的,柵介質(zhì)的測(cè)量具有復(fù)雜的C-V模型。

采用RF/RF C-V的顧慮

不可靠的測(cè)試會(huì)阻礙生產(chǎn)管理。好器件的壞測(cè)量結(jié)果被稱為alpha錯(cuò)誤。在生產(chǎn)中,這可能意味著有晶圓被誤廢棄。讓人誤解的ITRS信息,以及許多公司在他們的建模實(shí)驗(yàn)室經(jīng)歷緩慢、艱苦的過程,這些結(jié)合起來都使得工程師不情愿采用量產(chǎn)RF測(cè)試,他們認(rèn)為會(huì)有高的alpha錯(cuò)誤率。

人們還認(rèn)識(shí)到生產(chǎn)能力和運(yùn)營(yíng)成本將是不可接受的,而且還需要高水準(zhǔn)的技術(shù)支持來解釋測(cè)量結(jié)果。沒有可靠的校準(zhǔn)、以及接觸電阻問題所帶來的重復(fù)測(cè)試,造成了早期的RF系統(tǒng)的低生產(chǎn)能力。過去舊系統(tǒng)的校準(zhǔn)并不是對(duì)不同的測(cè)量頻率配置都有效。高的運(yùn)營(yíng)成本還與手動(dòng)測(cè)試黃金標(biāo)準(zhǔn)校正片有關(guān)系,它用的是軟墊和昂貴的RF探針,這種探針會(huì)由于過度壓劃而很快壞掉,從而成本大增。市場(chǎng)上還有一種錯(cuò)誤的理解,認(rèn)為晶圓級(jí)的s參數(shù)測(cè)試需要專門的探針和卡盤。

生產(chǎn)中關(guān)于RF測(cè)試需要額外關(guān)注的方面:

● 需要改變大量的測(cè)試結(jié)構(gòu)。

● 結(jié)果不穩(wěn)定,隨設(shè)備、人和時(shí)間的變化而發(fā)生變化。

● RF專家必須照顧呵護(hù)每一臺(tái)設(shè)備。

● 對(duì)于不同的批次可能需要完全不同的處理和操作流程。

● 懷疑這是否能夠成為實(shí)時(shí)技術(shù)。

● 實(shí)驗(yàn)室級(jí)別的結(jié)果不可靠。

fab在這些認(rèn)知的基礎(chǔ)上仍然維持現(xiàn)狀,像“瞎蒼蠅”一樣進(jìn)行著RF芯片、新柵極材料和其他先進(jìn)器件的設(shè)計(jì)和工藝開發(fā)。結(jié)果是設(shè)計(jì)與工藝的相互作用,大大增加了成本和走向市場(chǎng)的時(shí)間,同時(shí)還伴隨著更低的初始良率。

生產(chǎn)解決方案

使晶圓級(jí)RF測(cè)試成為生產(chǎn)工藝控制工具的關(guān)鍵在于測(cè)試的完全自動(dòng)化。這意味著機(jī)器人要把晶圓、校準(zhǔn)標(biāo)準(zhǔn)、探針卡傳送到需要這些東西的地方。換句話說,設(shè)計(jì)測(cè)試系統(tǒng)時(shí)一個(gè)主要的目標(biāo)是沒有人為干預(yù)的情況下數(shù)據(jù)的完整性。

現(xiàn)在的第三代測(cè)試機(jī)臺(tái)具有達(dá)到40GHz的這種測(cè)試能力。不像實(shí)驗(yàn)室的儀器,這些專門設(shè)計(jì)用于量產(chǎn)環(huán)境的測(cè)試機(jī)臺(tái),根據(jù)不同的應(yīng)用,支持從6到65GHz的升級(jí)。要求第三代測(cè)試機(jī)臺(tái)能夠自動(dòng)進(jìn)行寄生去除處理,并根據(jù)DUT特性進(jìn)行選擇測(cè)試,這是獲得可信的Cox, Fmax和Q值所面臨的主要技術(shù)挑戰(zhàn)。這些算法,再加上改進(jìn)的互連技術(shù),以及自動(dòng)的校準(zhǔn)過程,使得從s參數(shù)測(cè)試迅速準(zhǔn)確地提取RF參數(shù)成為可能。

精確的寄生去除處理包括糾正隨機(jī)的測(cè)量假象。比如,在一個(gè)特征阻抗為50Ω的系統(tǒng)中,接觸電阻的任何變化都會(huì)限制測(cè)量的可重復(fù)性。設(shè)備制造商必須確定RF測(cè)試中所有不穩(wěn)定的起源,從而在設(shè)計(jì)測(cè)量系統(tǒng)時(shí)有針對(duì)性地加以消除。系統(tǒng)互聯(lián)的創(chuàng)新設(shè)計(jì)改進(jìn)了系統(tǒng)中主要部件之間連接的可重復(fù)性。

設(shè)備制造商為了保證測(cè)量的可重復(fù)性,還要注意的其他方面如:測(cè)量自動(dòng)化,探針接觸阻抗的修正,探針變形量(overdrive)的調(diào)整,探針的清潔初始化。控制好探針的變形量以及必要時(shí)對(duì)探針進(jìn)行清洗,這些都會(huì)明顯延長(zhǎng)探針的壽命,這會(huì)降低主要的耗材成本(每根RF探針價(jià)值大約$1000)。這應(yīng)該也是測(cè)試機(jī)臺(tái)統(tǒng)計(jì)過程控制的一部分。

在具有穩(wěn)定已知的誤差分布,以及不確定性特征的條件下,來源于收集數(shù)據(jù)的史密斯曲線就不會(huì)存在非物理假象;不再需要由專家來分析和解釋這些結(jié)果了。在舊的系統(tǒng)中,RF測(cè)試專家需要對(duì)數(shù)據(jù)進(jìn)行監(jiān)控(跟蹤每個(gè)測(cè)試系列的曲線等),尋找奇怪的、或者意外的測(cè)量結(jié)果,然后分析這些結(jié)果以確認(rèn)它們代表的是工藝的變化,而不是測(cè)量的異常。

第三代參數(shù)測(cè)試儀通過改進(jìn)邏輯方法使得持續(xù)監(jiān)控RF測(cè)量成為現(xiàn)實(shí),降低甚或消除了對(duì)于RF專家技術(shù)支持的需求。使用這些系統(tǒng),不周生產(chǎn)層面的操作者能夠通過大量的產(chǎn)品和生產(chǎn)設(shè)備獲取可重復(fù)的、實(shí)時(shí)的測(cè)量結(jié)果。RF測(cè)試幾乎和DC測(cè)試一樣容易,它也成為完全表征晶圓器件時(shí)的必需之舉。實(shí)際上,一套第三代系統(tǒng)可以同時(shí)進(jìn)行DC和RF測(cè)試(見“RF測(cè)試的創(chuàng)新設(shè)計(jì)”)。這個(gè)系統(tǒng)包含了許多其他的改進(jìn),以提高產(chǎn)能,使它在工藝監(jiān)控的量產(chǎn)晶圓級(jí)測(cè)試方面更實(shí)用。這些特點(diǎn)加速了建模實(shí)驗(yàn)室的測(cè)量工作,同時(shí)又不降低測(cè)量結(jié)果的實(shí)驗(yàn)室級(jí)別,從而縮短了研發(fā)周期和進(jìn)入市場(chǎng)的時(shí)間。所有這些都可以通過簡(jiǎn)單的系統(tǒng)升級(jí)實(shí)現(xiàn),而不必購(gòu)買專用的探針臺(tái)。當(dāng)校準(zhǔn)規(guī)格存儲(chǔ)到探針臺(tái)后,操作流程與單純的DC測(cè)試一樣,只有在周期性的設(shè)備保養(yǎng)時(shí)才會(huì)變化。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論