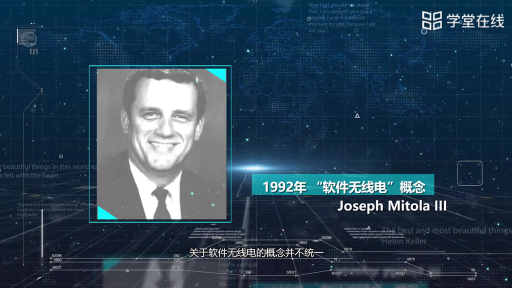

眾多的行業(yè)標(biāo)準(zhǔn)、規(guī)格尺寸、頻率和頻譜所有權(quán)都在推動(dòng)對商業(yè)無線的靈活性要求不斷提升。Xilinx?多模無線目標(biāo)設(shè)計(jì)平臺(tái)這是面向了高吞吐量、帶 有域優(yōu)化FPGAs、IP構(gòu)建塊、設(shè)計(jì)工具、參考設(shè)計(jì)和開發(fā)板的信號(hào)處理密集型系統(tǒng)的需求。單芯片數(shù)字無線裝置可以設(shè)計(jì)用于支持多種標(biāo)準(zhǔn),極大的簡化了供 貨鏈,并使原始設(shè)備制造商(OEM)能夠?qū)?a href="http://m.xsypw.cn/v/tag/1722/" target="_blank">網(wǎng)絡(luò)提供商的要求快速做出響應(yīng)。

通過高傳輸效率降低資本支出和運(yùn)營支出

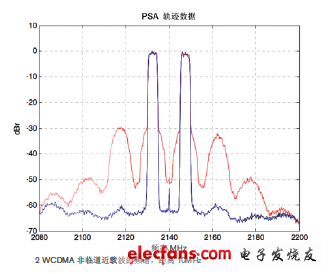

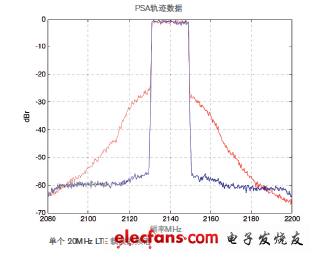

LDMOS1 功率放大器的3G無線接口的典型傳輸效率在8%到15之間。最新一代的功率放大器和Xilinx峰值因數(shù)降低(CFR)和數(shù)字預(yù)失真 (DFD)LogiCORE? IP利用先進(jìn)的數(shù)字算法、效率可以把它提高到35%到45%。這表示對于典型的10000個(gè)基站的網(wǎng)絡(luò)來說,每年的運(yùn)營支出(OpEx2)成本可以節(jié)省2 千萬美元之多。通過在功率放大器中采用更小的晶體管,還可以降低資本支出(CapEx3),而且能夠在天線上使用相同的傳輸功率額定值。

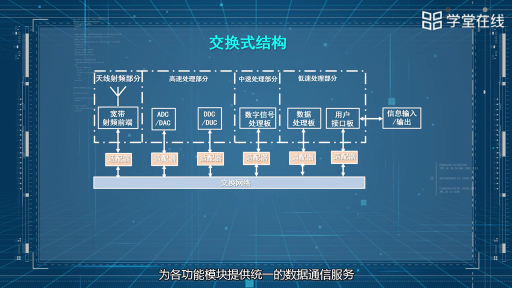

集成是降低功率和成本及提高可靠性的關(guān)鍵

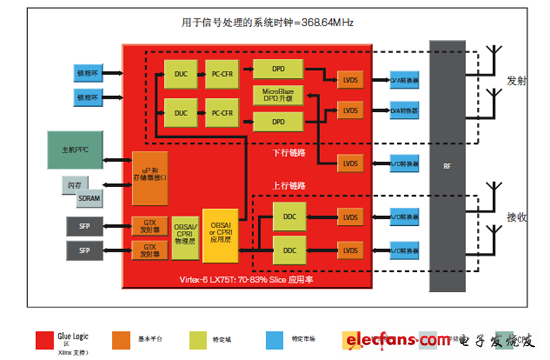

使 用單一的FPGA替換多個(gè)ASSP可以實(shí)現(xiàn)最小的數(shù)字PCB占用面積。Xilinx的FPGA把豐富的DSP與邏輯電路資源結(jié)合在了一起,在具有實(shí)現(xiàn) CPRI,OBSAI或JESD204A連接能力的千兆位級(jí)發(fā)射器(MGT)上高效的實(shí)現(xiàn)了數(shù)字上變換(DUC)、數(shù)字下變換(DDC)、CFR和DPD 算法。Xilinx FPGA的低功率高性能構(gòu)造可以提供在同級(jí)別產(chǎn)品中領(lǐng)先的功耗性能和最低的總體電路板成本。

例:使用DPD LogiCORE IP進(jìn)行2發(fā)射、2接收 (2x2) LTE-DFE參考設(shè)計(jì)

參考設(shè)計(jì)的特點(diǎn)

? DUC/DDC,用于每個(gè)天線的5、10、15及20MHz單載波和2x5、2x10和4x5MHz多載波選件

? Xilinx CFR,輸出峰值與平均功率比(PAPR)-7dB,在誤差向量幅度(EVM)《4%,鄰道泄漏比(ACLR)》70dB 時(shí)

? Xilinx DPD最多支持4個(gè)帶單MicroBlaze?處理器引擎的發(fā)射器,可以提供最高30dB的頻譜矯正性能和超過40%的Doherty功率放大器效率

? 全OBSAI主從PHY利用內(nèi)置的低功率MGT支持最高6.144Gbps的線路速度

? 可擴(kuò)展到2x4 (2T4R)和4x4 (4T4R) 天線陣列,與Virtex?-6 FPGA包遷移組合

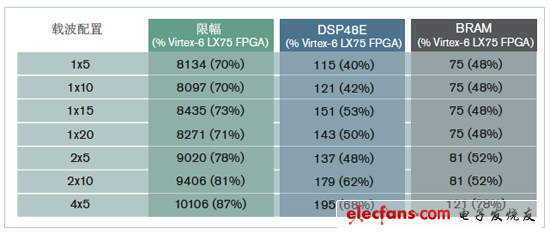

FPGA資源利用

? 包括了上圖中標(biāo)注的所有資源,包括:

o 微處理器接口

o OBSAI主從

o OBSAI簡單應(yīng)用層

o 2發(fā)射、2接收 DUC/DDC/CFR,具有以下使用Xilinx LTE-DFE參考設(shè)計(jì)實(shí)現(xiàn)的載波配置,和Xilinx DPD LogiCORE IP

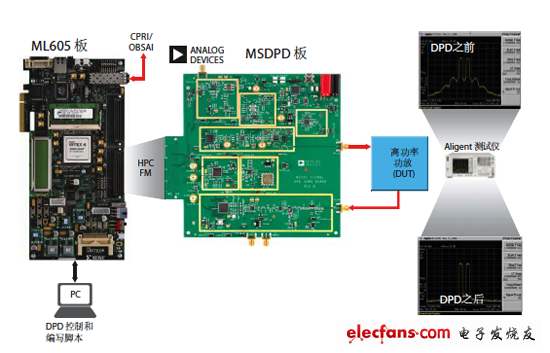

多模無線演示平臺(tái)

無線射頻子系統(tǒng)的設(shè)計(jì)能與它們所處的應(yīng)用環(huán)境息息相關(guān)。這對于復(fù)雜的算法如數(shù)字預(yù)失真尤其明顯,在該算法中,很難對諸如熱和無功晶體管存儲(chǔ)器和模擬信號(hào)鏈路的特性等模擬電路效應(yīng)進(jìn)行建模。

Xilinx 已經(jīng)在與AnalogDevices公司合作制造高性能的多模無線演示平臺(tái),它可以演示第三方功率放大器在各種頻率和任意無線接口下的DPD解決方案。 XilinxML605電路板和Analog Devices的混合信號(hào)數(shù)字預(yù)失真(MSDPD)電路板通過兩塊電路板上的 FMC 接頭連接起來。XilinxML605上實(shí)施了具有DUC、DDC、CFR和DPD功能的高級(jí)信號(hào)處理應(yīng)用,充分利用了Analog Devices公司MSDPD板上的高性能數(shù)據(jù)轉(zhuǎn)換器和 RF 信號(hào)鏈路。

特點(diǎn)

Xilinx ML605板

? Virtex-6 LX240T FPGA 使用戶可以為任何波形開發(fā)復(fù)雜的DUC/DDC、CFR和DPD算法

? 如需完整的規(guī)格,請?jiān)L問: http://www.xilinx.com/products/devkits/EK-V6-ML605-G.htm

Analog Devices的MSDPD電路板

? 支持超過 20MHz的傳輸帶寬

? 可配置在裝配體上,用于800MHz - 2.7GHz RF頻率

? 20dB RF輸出功率調(diào)整,分辨率10-bit

? +10dBm RF輸出功率

? 符合苛刻的MC-GSM性能要求 (帶AD9122)

? 數(shù)據(jù)轉(zhuǎn)換器的的占用面積與更低規(guī)格的型號(hào)兼容

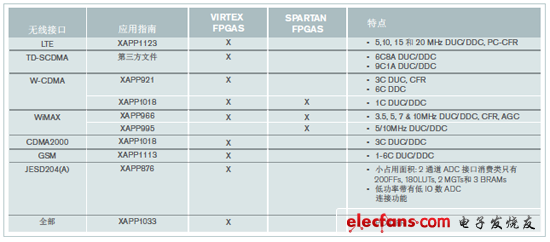

現(xiàn)有的Xilinx無線參考設(shè)計(jì)小結(jié)

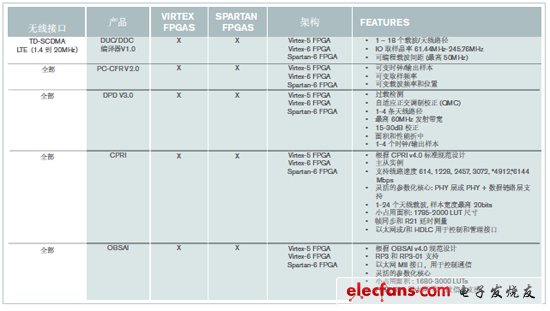

現(xiàn)有的Xilinx無線Logicore IP小結(jié)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論