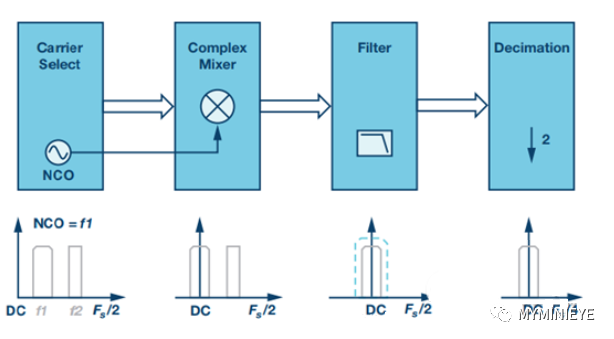

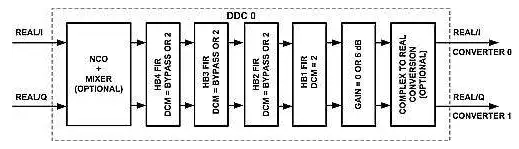

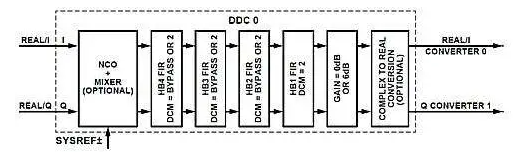

濾波器緊跟在頻率變換級后面。在所需的載波頻帶向下調諧到DC以后,濾波器就能有效降低采樣率,同時能有效抑制在調諧后的有用帶寬周圍由臨近的無用載波產生的混疊現(xiàn)象。

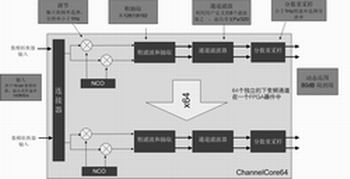

單個8抽取DDC能夠使賽靈思Artix-7 FPGA系統(tǒng)可支持的ADC數(shù)量提高至四倍。

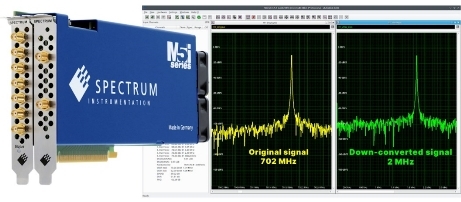

將輸入信號通過混頻降至基帶時,由于過濾了負像,因而會出現(xiàn)6 dB的信號損失。NCO還會額外產生一個小的插入損耗。因此,降頻至基帶后的輸入信號總損耗通常略高于6 dB。NCO允許將輸入頻譜調諧至DC,這樣便可由后續(xù)的濾波器模塊進行有效濾波,以防止混疊。DDC還可能包含獨立控制的數(shù)字增益級。增益級讓系統(tǒng)實現(xiàn)+6 dB或更高的增益,以在輸出位數(shù)的整個范圍內集中信號的動態(tài)范圍。

處理器間中斷

采用ADC樣本抽取后便無需向信號鏈下游發(fā)送最終會被舍棄的無用信息。由于這類數(shù)據(jù)被濾除,因此降低了ADC后端所需的輸出數(shù)據(jù)帶寬。這個減少量被I/Q輸出數(shù)據(jù)量的增加所抵消。例如,具有I和Q數(shù)據(jù)的16抽取濾波器會使寬帶輸出數(shù)據(jù)減少8倍。

數(shù)據(jù)速率的最小化能減少ADC的JESD204B輸出通道數(shù)量,進而降低系統(tǒng)布局的復雜性。ADC輸出帶寬的減小有助于設計小型化系統(tǒng),否則這是無法實現(xiàn)的。例如,受系統(tǒng)功耗和尺寸的限制,電路板只能使用一個FPGA,對于這種情況,系統(tǒng)所支持的高速串行收發(fā)器數(shù)量會在不使用DDC時限制ADC的數(shù)量。

當系統(tǒng)內只能觀察到很窄的帶寬時,ADC內的抽取有助于消除這種局限性。使用單個8抽取DDC可將ADC的輸出帶寬減少至兩個輸出數(shù)據(jù)通道,以讓賽靈思Artix®-7 FPGA系統(tǒng)支持的ADC數(shù)量提高至四倍。對于這種情況,我們利用Artix-7 FPGA 中現(xiàn)有的16GTP 收發(fā)器設計出采用DDC的八ADC結構(圖2)。這樣能更高效使用賽靈思FPGA資源,成為一組FDM通道的多通道數(shù)字接收器。

DDC濾波器是否影響SNR和SFDR?

下一個需要研究的問題是當DDC濾波器打開和關閉時,信噪比(SNR)和無雜散動態(tài)范圍(SFDR) 這兩個模擬性能如何變化。

由于轉換器的寬帶噪聲被濾除而且只能觀察到較窄的頻譜,我們應該看到信號功率與觀察到的噪聲之比更高。ADC的動態(tài)范圍在濾波器的通帶內應該更好。對寬帶頻譜進行抽取和濾波的固有優(yōu)勢在于利用DDC改進SNR。

DDC實現(xiàn)的數(shù)字濾波用來濾除較窄帶以外的噪聲。ADC的SNR計算必須包含一個考慮被濾除噪聲處理增益的濾波校正因子。使用完美數(shù)字濾波器,帶寬每減小的2的冪次方,被濾除噪聲引起的處理增益將會增加+3 dB:

理想SNR(具有處理增益)=6.02*N + 1.76 dB + 10log10(fs/(2*BW))

使用DDC的一個明顯優(yōu)勢是能夠使基波信號的諧波落在所需頻帶的外面。通過適當?shù)念l率規(guī)劃,數(shù)字濾波可以防止諧波在窄DDC帶寬內看到,從而提高系統(tǒng)的SFDR性能。

在只需要窄帶的系統(tǒng)中,DDC通過濾掉寬帶噪聲來提供ADC處理增益。這樣能提高有用帶寬內的信噪比。另一個優(yōu)勢是,通過合理的頻率規(guī)劃,通常占主導的第二和第三次諧波會落到調諧后的有用帶寬之外并被數(shù)字濾除。這能提高系統(tǒng)的SFDR。

采樣定理指出諧波或其他高階系統(tǒng)尖刺可能回折到每個奈奎斯特頻帶末尾的周圍。這對于DDC同樣適用,其第二或第三次無用諧波有可能回折到通帶內并降低SFDR。因此,為了研究這類采樣問題,應該為DDC通帶濾波器寬度和NCO調諧位置實施系統(tǒng)頻率規(guī)劃。

是否需要外部濾波器?

使用內部DDC的系統(tǒng)ADC也可以使用附加的模擬濾波器,就像沒有DDC濾波時那樣。對于寬帶系統(tǒng),DDC能夠緩和ADC前端的濾波要求。

DDC中的數(shù)字濾波能分擔一些工作,否則就要在前端放置嚴格的防止混疊模擬濾波器。不過,寬頻帶前端能實現(xiàn)多種用途,可讓DDC同時觀察多個頻帶,或者利用NCO掃描有用的頻帶以找到變化的輸入信號。

ADC能否提供多個DDC?

工程師考慮用FPGA實現(xiàn)內部數(shù)字下變頻時提出的最后一個問題是,ADC是否只提供一個DDC。答案是否定的;事實上可以觀察到多個頻帶。

電子發(fā)燒友App

電子發(fā)燒友App

評論