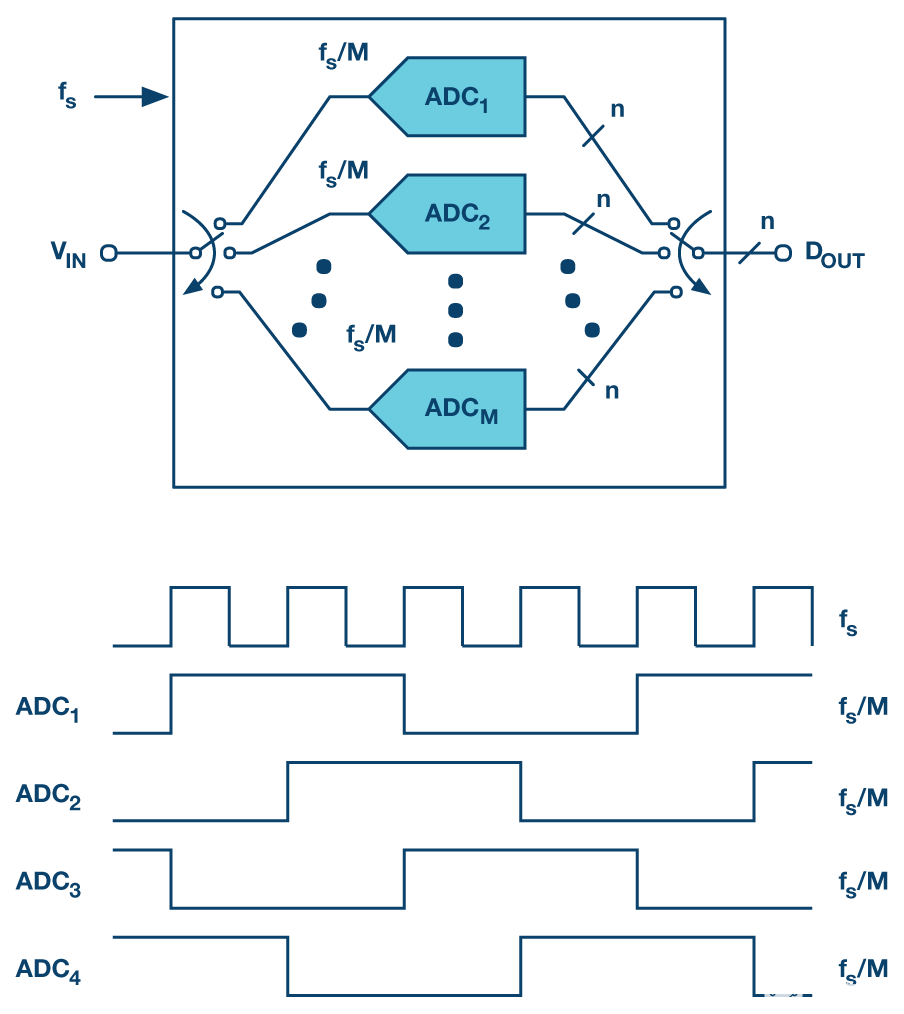

交錯(cuò)式ADC具有十分廣闊的應(yīng)用空間。在通信基礎(chǔ)設(shè)施中,存在著一種推動(dòng)因素,使ADC的采樣速率不斷提高,以便在諸如DPD(數(shù)字預(yù)失真)等線性化技術(shù)中支持多頻段、多載波無(wú)線電,同時(shí)滿足更寬的帶寬要求。

2014-04-17 17:54:17 2578

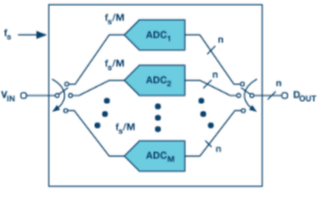

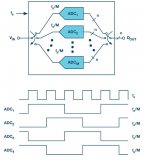

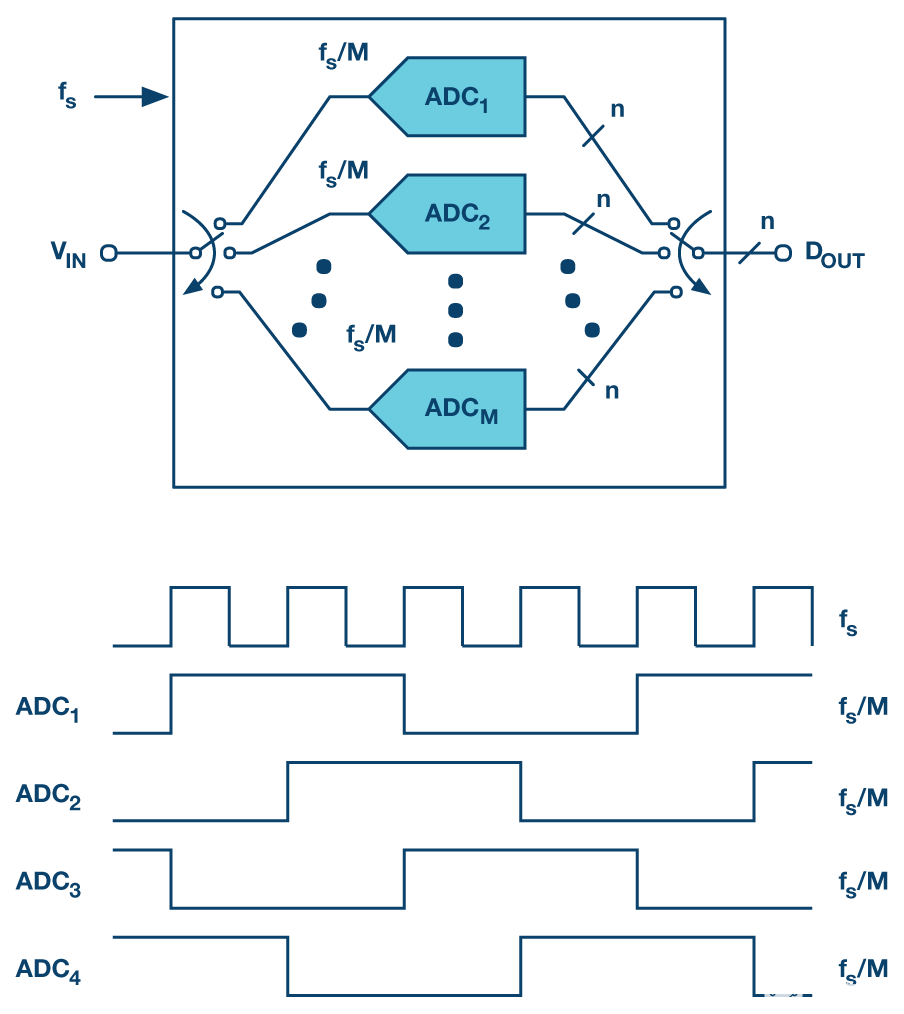

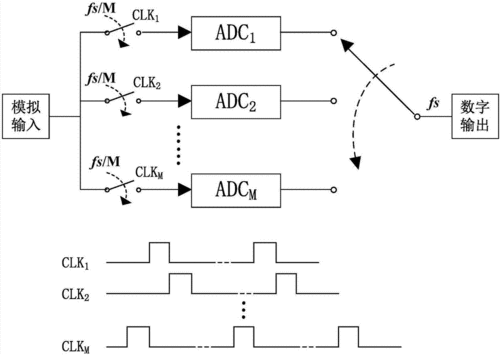

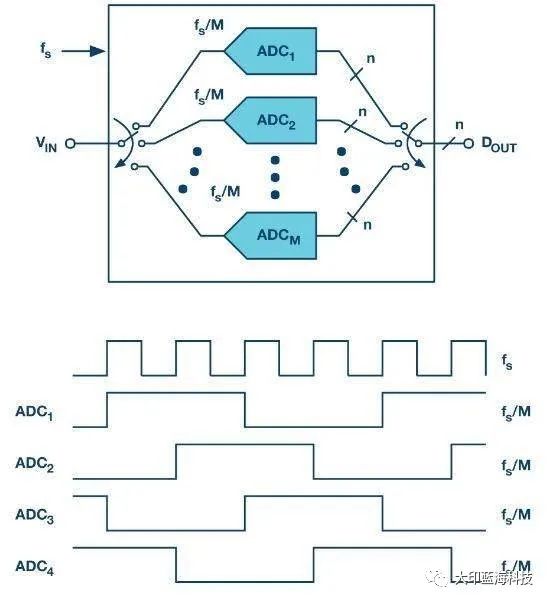

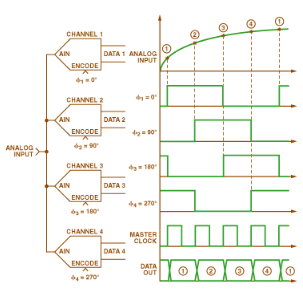

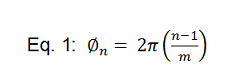

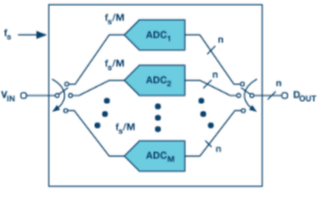

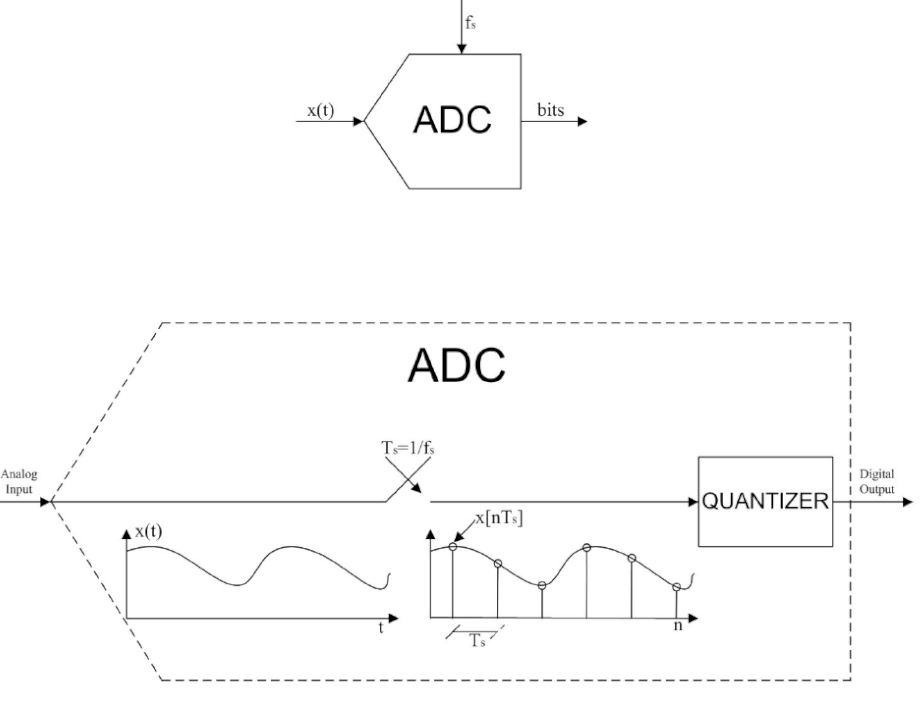

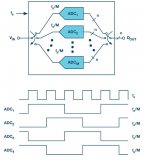

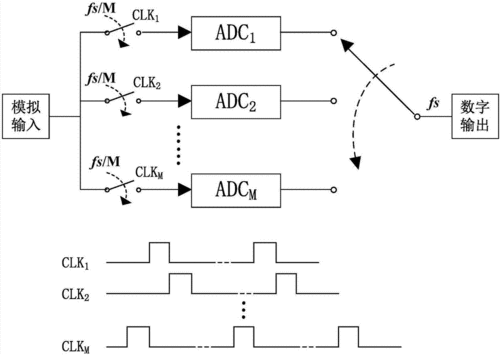

2578 圖1. M次交錯(cuò)的n位ADC陣列每一個(gè)ADC的采樣速率為fs/M,得到的時(shí)間交錯(cuò)ADC采樣速率為fs。M = 4的時(shí)鐘方案示例在該圖下半部分顯示。

2020-09-09 10:38:38 845

845

跨越當(dāng)今市場(chǎng)的許多領(lǐng)域,交織的模擬-數(shù)字轉(zhuǎn)換器( ADC的)有幾個(gè)優(yōu)點(diǎn)在許多應(yīng)用。在通信基礎(chǔ)設(shè)施中,除了數(shù)字預(yù)失真( DPD )等線性化技術(shù)對(duì)帶寬的要求更高之外,一直在不斷尋求更高采樣率的ADC

2021-02-13 10:41:00 3424

3424

在本文中,我們描述了在 M 通道時(shí)間交錯(cuò)模數(shù)轉(zhuǎn)換器 (TI-ADC) 的一般情況下,時(shí)序和增益失配對(duì)采樣信號(hào)的影響,并提出了一種適用于雙通道 TI- ADC 案例。 時(shí)序和增益失配的數(shù)字校正 作者

2021-06-14 03:45:00 3352

3352

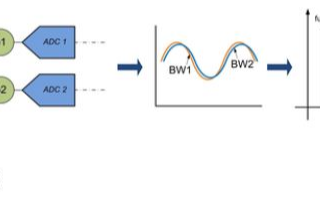

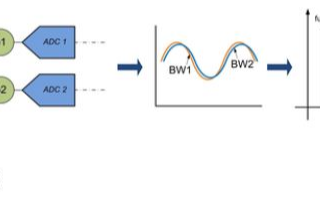

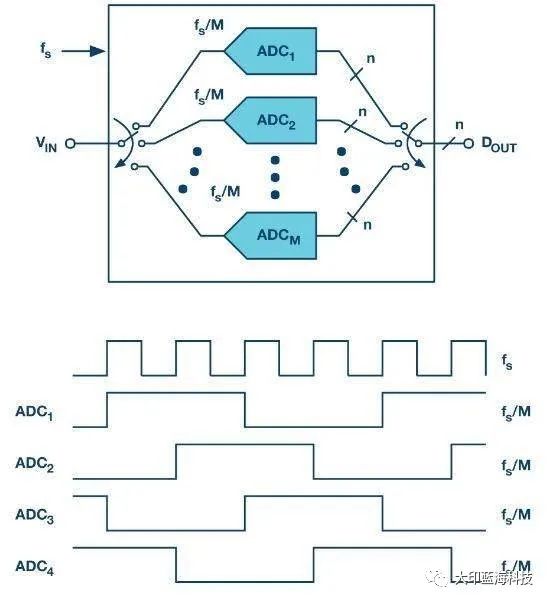

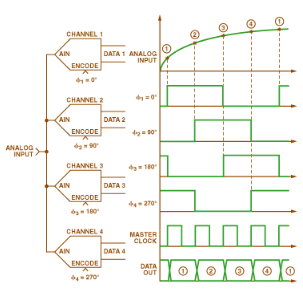

今天我們將圍繞交錯(cuò)式 ADC 轉(zhuǎn)換器展開。當(dāng) ADC 轉(zhuǎn)換器交錯(cuò)時(shí),兩個(gè)或多個(gè)具有定義的時(shí)鐘關(guān)系的 ADC 轉(zhuǎn)換器用于同時(shí)對(duì)輸入信號(hào)進(jìn)行采樣并產(chǎn)生組合輸出信號(hào),從而導(dǎo)致采樣帶寬為多個(gè)單獨(dú)的 ADC 轉(zhuǎn)換器。

2023-04-28 09:49:40 428

428

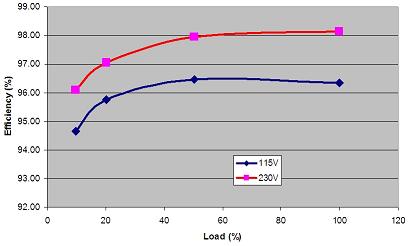

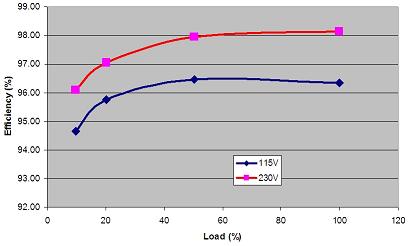

輸出端模擬調(diào)光。請(qǐng)參閱基于 UCC28060 交錯(cuò)式交流直流單級(jí)反激的 LED 驅(qū)動(dòng)器,了解設(shè)計(jì)指南主要特色隔離式準(zhǔn)諧振反激 PFC 拓?fù)渥匀?b class="flag-6" style="color: red">交錯(cuò)模式可減少輸入和輸出紋波94% 的峰值效率模擬調(diào)光此參考設(shè)計(jì)已構(gòu)建完成并通過(guò)測(cè)試,且內(nèi)含測(cè)試報(bào)告

2018-12-07 14:09:20

ADP1829是一款多功能,雙輸出,交錯(cuò)式同步PWM降壓控制器,可在3.0 V至18 V的輸入電壓范圍內(nèi)產(chǎn)生兩路獨(dú)立輸出。每個(gè)通道均可配置為提供0.6V至85%輸入電壓的輸出電壓。兩個(gè)通道的相位相差180°,可減小輸入電容上的電流應(yīng)力,并允許使用更小,更低成本的輸入電容

2020-06-09 17:25:38

適用于高帶寬,高采樣率應(yīng)用程序的新型DESCLKI??Q模式與ADC10D1x00,ADC12D1x00引腳兼容用于多芯片同步的自動(dòng)同步功能內(nèi)部端接,緩沖差分模擬輸入交錯(cuò)定時(shí)自動(dòng)和手動(dòng)偏斜調(diào)整用于系統(tǒng)調(diào)試

2021-01-08 09:15:08

適用于高帶寬,高采樣率應(yīng)用程序的新型DESCLKI??Q模式與ADC10D1x00,ADC12D1x00引腳兼容用于多芯片同步的自動(dòng)同步功能內(nèi)部端接,緩沖差分模擬輸入交錯(cuò)定時(shí)自動(dòng)和手動(dòng)偏斜調(diào)整用于系統(tǒng)調(diào)試

2021-01-08 09:15:08

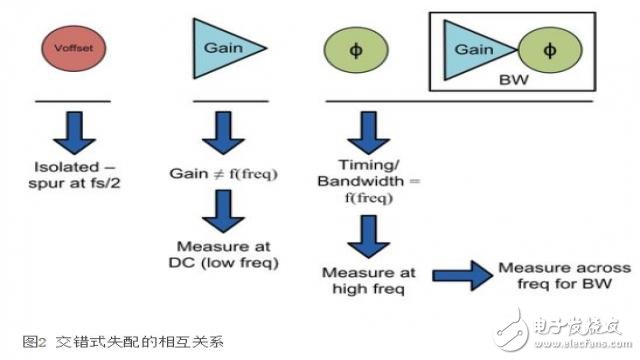

交錯(cuò)ADC得到了越來(lái)越多的工程師的廣泛關(guān)注。目前仍有諸多問(wèn)題聚焦于ADC失配的校準(zhǔn)方法。 在深入探討任何可能的校準(zhǔn)方法之前,工程師需要了解都有哪些不匹配。 對(duì)于失調(diào)不匹配,沒有必要施加一個(gè)輸入信號(hào)

2019-07-25 06:58:19

交錯(cuò)結(jié)構(gòu)的優(yōu)勢(shì)是什么交錯(cuò)ADC的時(shí)鐘要求

2021-04-06 09:00:31

交錯(cuò)式ADC之間的帶寬失配

2021-04-02 07:52:52

運(yùn)用時(shí)序交錯(cuò)式類比數(shù)位轉(zhuǎn)換器(timeinterleavedADC)在每秒高達(dá)數(shù)十億次的同步取樣類比訊號(hào)是一個(gè)技術(shù)上的挑戰(zhàn),除此之外,對(duì)於混合訊號(hào)電路的設(shè)計(jì)也需要非常謹(jǐn)慎小心。基本上,時(shí)序交錯(cuò)

2018-09-17 17:25:18

天線置入手機(jī),其性能更易受外部條件的影響,如手機(jī)接近不同材料以及用戶握持手機(jī)的方式等。在這些條件下,天線阻抗可能發(fā)生變化,導(dǎo)致天線與RF 前端 (RFFE) 之間的阻抗失配。當(dāng)天線在不同頻段通信時(shí),天線阻抗

2023-05-05 09:43:21

這篇文章提供了對(duì)范例式集成比例型三線RTD測(cè)量系統(tǒng)的分析,以便了解誤差的來(lái)源,包括勵(lì)磁電流失配產(chǎn)生的影響。

2020-08-24 07:23:03

為 ~ 35Mhz ADC 時(shí)鐘獲得 ~ 8MHz 采樣率(雙交錯(cuò) 2x4MHz,連續(xù)轉(zhuǎn)換)在我嘗試在禁用連續(xù)轉(zhuǎn)換的情況下從定時(shí)器觸發(fā) ADC 之前,這非常有效。對(duì)于 8MHz(2 x 4MHz)采樣率,我需要

2023-01-06 07:15:22

設(shè)計(jì)lna時(shí)想要查看差分輸出的增益失配和相位失配,這要怎么設(shè)置才能仿真出來(lái)?請(qǐng)給位大神指點(diǎn)。

2021-06-25 06:22:44

電壓和參考電壓上。由于ADC輸出代碼表示的是輸入電壓和參考電壓之間的關(guān)系,故最終轉(zhuǎn)換結(jié)果可換算為RTD電阻和RREF電阻的比,并非取決于參考電壓或勵(lì)磁電流的值(方程式11)。所以,如果勵(lì)磁電流完美匹配

2018-11-30 16:48:27

這篇文章將討論兩種可消除勵(lì)磁電流失配和失配漂移影響的方法。第一種方法是把內(nèi)部多路復(fù)用器用于大多數(shù)集成式解決方案的軟件方法。第二種方法是更改電路拓?fù)浣Y(jié)構(gòu)的硬件方法。

2020-08-27 07:13:57

匹配、時(shí)序不匹配和帶寬不匹配。其中最容易理解的可能是兩個(gè)ADC之間的失調(diào)不匹配。每個(gè)ADC都會(huì)有一個(gè)相關(guān)的直流失調(diào)值。當(dāng)兩個(gè)ADC交織并在兩個(gè)ADC之間來(lái)回交替采樣時(shí),每個(gè)連續(xù)采樣的直流失調(diào)會(huì)發(fā)

2020-08-05 09:54:42

PWM 波形。該設(shè)計(jì)實(shí)現(xiàn)了新型的電流共享技術(shù),以準(zhǔn)確地在相位之間實(shí)現(xiàn)電流平衡。主要特色數(shù)控式兩相交錯(cuò) LLC 諧振直流/直流轉(zhuǎn)換器無(wú)需任何額外硬件即可實(shí)現(xiàn)出色的相位間電流共享峰值效率:94.5%。對(duì)于

2018-12-26 14:42:54

,這些標(biāo)準(zhǔn)仍將需要高動(dòng)態(tài)范圍,以便充分清晰地觀察小信號(hào)。解決這些需求的一種技術(shù)是時(shí)間交織的ADC。對(duì)于高速ADC,性能,采樣率和功耗之間存在折衷。時(shí)間交錯(cuò)在不同時(shí)間使用多個(gè)ADC采樣來(lái)提高有效采樣率,同時(shí)

2017-04-26 12:04:25

介紹了采用商用1200V碳化硅(SiC)MOSFET和肖特基二極管的100KHz,10KW交錯(cuò)式硬開關(guān)升壓型DC / DC轉(zhuǎn)換器的參考設(shè)計(jì)和性能。 SiC功率半導(dǎo)體的超低開關(guān)損耗使得開關(guān)頻率在硅實(shí)現(xiàn)方面顯著增加

2019-05-30 09:07:24

內(nèi)存交錯(cuò)功能可并行閱讀大內(nèi)存芯片,減小內(nèi)存訪問(wèn)時(shí)間。內(nèi)存交錯(cuò)功能最多可并行訪問(wèn)單CPU內(nèi)存板上的 32 個(gè)內(nèi)存芯片。

2019-09-18 09:01:19

的帶寬。SMT焊盤與內(nèi)部參考銅箔之間的距離取決于SMT焊盤的寬度以及包括連接器引腳和焊錫在內(nèi)的SMT焊盤有效厚度。在PCB投產(chǎn)之前應(yīng)先進(jìn)行3D建模和仿真,確保構(gòu)建的傳輸通道具有良好的信號(hào)完整性。

2018-09-17 17:45:00

CRD-60DD12N,60 kW交錯(cuò)式升壓轉(zhuǎn)換器演示板基于1200 V,75mΩ(C3M)SiC MOSFET。該演示板由四個(gè)15 kW交錯(cuò)升壓級(jí)組成,每個(gè)級(jí)使用CGD15SG00D2隔離式柵極驅(qū)動(dòng)板

2019-04-29 09:18:26

由NCP1631板驅(qū)動(dòng)的300W交錯(cuò)式PFC級(jí)的應(yīng)用示意圖,調(diào)整為NCP1632驅(qū)動(dòng)。 NCP1632是NCP1631的升級(jí)版本。與他的父親一樣,NCP1632是用于交叉間PFC應(yīng)用的雙MOSFET

2019-05-16 09:08:22

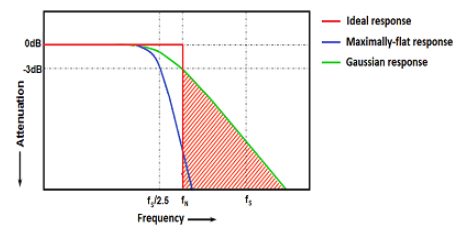

作者:Rob Reeder摘要模擬帶寬的重要性高于其他一切在越來(lái)越多的應(yīng)用中得到體現(xiàn)。隨著GSPS或RF ADC的出現(xiàn),奈奎斯特域在短短幾年內(nèi)增長(zhǎng)了10倍,達(dá)到多GHz范圍。這幫助上述應(yīng)用進(jìn)一步拓寬

2019-07-22 08:01:03

我有一個(gè)關(guān)于 STM32H7(雙核解決方案)的 ADC1/2/3 內(nèi)核的問(wèn)題。比方說(shuō),我想在 ADC 內(nèi)核和 Cortex 內(nèi)核之間拆分幾個(gè) ADC 通道。是否可以在皮質(zhì) m4 上為 ADC1 核心

2023-01-10 06:09:51

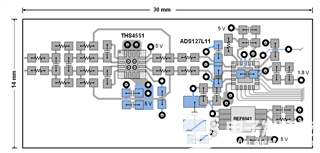

在信號(hào)鏈中運(yùn)用采樣保持放大器(THA),可以從根本上擴(kuò)展帶寬,使其遠(yuǎn)遠(yuǎn)超出 ADC 采樣帶寬,滿足苛刻高帶寬的應(yīng)用的需求。本文將證明,針對(duì) RF 市場(chǎng)開發(fā)的最新轉(zhuǎn)換器前增加一個(gè) THA,便可實(shí)現(xiàn)超過(guò)

2020-09-30 07:00:00

也對(duì)這個(gè)問(wèn)題深感頭痛。“阻抗失配”產(chǎn)生的原因是因?yàn)閷?duì)象模型與關(guān)系模型之間缺乏固有的親合力。“阻抗失配”所帶來(lái)的問(wèn)題包括:類的層次關(guān)系必須綁定為關(guān)系模式(將對(duì)象類映射為關(guān)系表),ID生成,并發(fā)訪問(wèn)以及

2019-06-04 06:47:47

的基本工作原理圖。 改善信號(hào)發(fā)生器或頻譜分析儀的失配損耗 如果負(fù)載和信號(hào)發(fā)生器之間的阻抗不匹配,就會(huì)產(chǎn)生失配誤差。在任何射頻和微波系統(tǒng)中,最大功率傳輸?shù)臈l件是阻抗匹配。但實(shí)際上,無(wú)論是信號(hào)發(fā)生器還是

2017-11-07 16:43:03

假設(shè)一對(duì)電流鏡(1:1),電流10uA,寬長(zhǎng)分別比50um/1um,finger=2和10um/1um,finger=10兩種情況。失配哪一個(gè)大?或者一樣?至少書上說(shuō),兩個(gè)面積一樣,失配一樣,真是這樣?仿真出來(lái)感覺前者好的多啊!為什么?

2021-06-24 07:14:05

控制電路來(lái)處理此問(wèn)題(如果沒有該電路,并聯(lián)各相之間的微小器件不匹配就會(huì)造成巨大的相位電流不平衡),有些方法優(yōu)于其它方法。[img][/img]圖1:雙相交錯(cuò)式雙開關(guān)正向轉(zhuǎn)換器 數(shù)字電源管理能夠執(zhí)行復(fù)雜

2011-07-14 08:52:28

有沒有帶寬介于AD637和AD8361之間的芯片?

2017-07-31 18:47:34

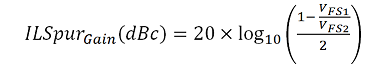

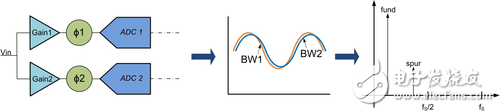

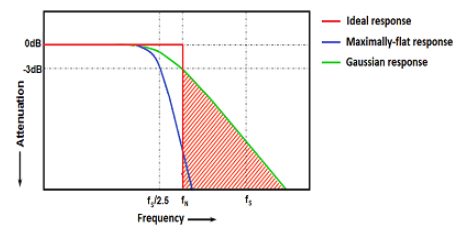

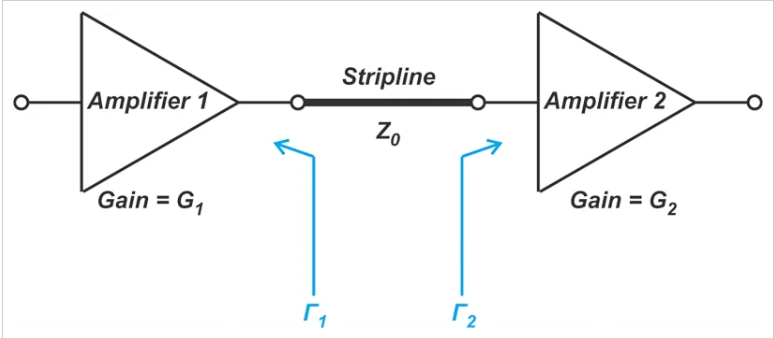

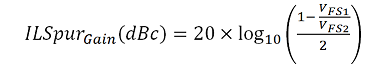

交錯(cuò)式ADC之間的帶寬失配應(yīng)該是對(duì)于設(shè)計(jì)師而言最難解決的失配問(wèn)題。 如圖所示,帶寬失配具有增益和相位/頻率分量。 這使得解決帶寬失配問(wèn)題變得更為困難,因?yàn)樗袃蓚€(gè)來(lái)自其他失配參數(shù)的分量:增益和時(shí)序失配。

2019-07-31 06:59:10

交錯(cuò) ADC。對(duì)三個(gè)通道之間的失配進(jìn)行校準(zhǔn),以便最大程度減少交錯(cuò)雜散。圖 5(a) 所示是一個(gè)輸入接近 1 GHz的輸出頻譜示例。在該頻譜中,除了約為 1 GHz的輸入音外,還可以看到通道在 500

2018-10-24 09:51:54

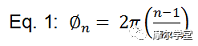

描述此參考設(shè)計(jì)提供了一個(gè)用于實(shí)現(xiàn) 12.8GSPS 采樣率的交錯(cuò)射頻采樣模數(shù)轉(zhuǎn)換器 (ADC) 的實(shí)用示例。這可通過(guò)對(duì)兩個(gè)射頻采樣 ADC 進(jìn)行時(shí)序交錯(cuò)來(lái)實(shí)現(xiàn)。交錯(cuò)需要在 ADC 之間進(jìn)行相移,此

2022-09-15 06:46:05

ADC內(nèi)核可以并行工作,從而實(shí)現(xiàn)高于單核的采樣速率。然而,每個(gè)這些內(nèi)核的輸入端之間都存在相位、失調(diào)、增益和帶寬微小差異。結(jié)果,新的交錯(cuò)偽像和圖像雜散可能進(jìn)入頻譜中,從而導(dǎo)致ADC寬帶SFDR下降。這會(huì)減小

2018-11-01 11:31:37

時(shí)間交錯(cuò)技術(shù)可使用多個(gè)相同的 ADC(文中雖然僅討論了 ADC,但所有原理同樣適用于 DAC 的時(shí)間交錯(cuò)特性),并以比每一個(gè)單獨(dú)數(shù)據(jù)轉(zhuǎn)換器工作采樣速率更高的速率來(lái)處理常規(guī)采樣數(shù)據(jù)序列。簡(jiǎn)單說(shuō)來(lái),時(shí)間

2019-07-23 06:52:17

我閱讀了有關(guān)ADC全功率帶寬的求解過(guò)程,文件中說(shuō)明全功率帶寬由瞬態(tài)公式推導(dǎo)求得,此公式的來(lái)源是什么?

2023-11-30 06:05:22

`描述TI 設(shè)計(jì):TIDA-00200 為需要 ~200W 輸出功率級(jí)別的電池充電應(yīng)用提出了一種具有最低物料清單成本的交錯(cuò)反激式拓?fù)洹T趯?shí)際電子組件之外,冷卻機(jī)制是總體設(shè)計(jì)成本的一大來(lái)源。該設(shè)計(jì)利

2015-04-29 11:36:56

描述TIDA-00200 為需要 ~200W 輸出功率級(jí)別和超精簡(jiǎn)物料清單的電池充電器應(yīng)用提供了一種交錯(cuò)反激式拓?fù)洹3藢?shí)際的電子元件外,冷卻方面的工作也占了總體設(shè)計(jì)成本的大部分。該設(shè)計(jì)利

2022-09-23 06:32:07

描述TI 設(shè)計(jì):TIDA-00200 為需要 ~200W 輸出功率級(jí)別的電池充電應(yīng)用提出了一種具有最低物料清單成本的交錯(cuò)反激式拓?fù)洹T趯?shí)際電子組件之外,冷卻機(jī)制是總體設(shè)計(jì)成本的一大來(lái)源。該設(shè)計(jì)利

2018-09-18 09:10:25

針對(duì)時(shí)域交錯(cuò)模數(shù)轉(zhuǎn)換器(TIADC)的通道失配問(wèn)題,提出一種在線校正方法。首先建立TIADC的數(shù)學(xué)模型,將增益和時(shí)間失配轉(zhuǎn)變?yōu)橥ǖ罏V波器幅度和延時(shí)參數(shù)的差異,然后利用校正后

2009-12-31 14:00:09 13

13 此參考設(shè)計(jì)提供了一個(gè)用于實(shí)現(xiàn) 12.8GSPS 采樣率的交錯(cuò)射頻采樣模數(shù)轉(zhuǎn)換器 (ADC) 的實(shí)用示例。這可通過(guò)對(duì)兩個(gè)射頻采樣 ADC 進(jìn)行時(shí)序交錯(cuò)來(lái)實(shí)現(xiàn)。交錯(cuò)需要在 ADC 之間進(jìn)行

2010-03-26 16:13:22 68

68 交錯(cuò)式PFC技術(shù)趨勢(shì)及新穎的單芯片交錯(cuò)式PFC控制器的應(yīng)用

近年來(lái),在一些對(duì)外形因數(shù)有嚴(yán)格要求的應(yīng)用中,如纖薄型液晶電視或筆記本適配器等,一種新興的功率因

2010-01-07 11:05:43 3133

3133

高速ADC提升分辨率與帶寬

ADC(模數(shù)轉(zhuǎn)換器)器件速度提升帶來(lái)功耗增加,從而提高了整體系統(tǒng)的成本。因此設(shè)計(jì)者的首要需求之一就是要降低高速ADC的功耗。ADI

2010-03-30 18:01:58 1181

1181 交錯(cuò)反激微功率光伏并網(wǎng)逆變器的設(shè)計(jì)_張錦吉

2016-12-15 19:30:58 4

4 交錯(cuò)并聯(lián)反激式準(zhǔn)單級(jí)光伏并網(wǎng)微逆變器_季曉春

2016-12-15 19:30:58 2

2 基于過(guò)零檢測(cè)的TIADC時(shí)鐘失配校準(zhǔn)算法_王曉蕾

2017-01-07 18:39:17 1

1 時(shí)間交織ADC時(shí)間失配后臺(tái)數(shù)字校準(zhǔn)算法_鄧紅輝

2017-01-08 10:30:29 1

1 交錯(cuò)結(jié)構(gòu)的優(yōu)勢(shì)可惠及多個(gè)細(xì)分市場(chǎng)。 最有用的優(yōu)勢(shì)是通過(guò)交錯(cuò)ADC更寬的奈奎斯特區(qū)增加帶寬。 同樣,我們首先舉兩個(gè)500MSPS ADC交錯(cuò)建立1000MSPS采樣速率的例子。 通過(guò)交錯(cuò)兩個(gè)ADC

2017-11-16 10:20:06 0

0 交錯(cuò)式ADC之間的帶寬失配應(yīng)該是對(duì)于設(shè)計(jì)師而言最難解決的失配問(wèn)題。 如圖1所示,帶寬失配具有增益和相位/頻率分量。 這使得解決帶寬失配問(wèn)題變得更為困難,因?yàn)樗袃蓚€(gè)來(lái)自其他失配參數(shù)的分量:增益

2017-11-16 10:51:03 1

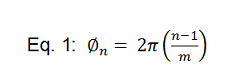

1 時(shí)間交錯(cuò)技術(shù)可使用多個(gè)相同的 ADC(文中雖然僅討論了 ADC,但所有原理同樣適用于 DAC 的時(shí)間交錯(cuò)特性),并以比每一個(gè)單獨(dú)數(shù)據(jù)轉(zhuǎn)換器工作采樣速率更高的速率來(lái)處理常規(guī)采樣數(shù)據(jù)序列。簡(jiǎn)單說(shuō)來(lái),時(shí)間交錯(cuò)(IL)由時(shí)間多路復(fù)用 M 個(gè)相同的 ADC 并聯(lián)陣列組成。

2018-01-17 14:59:51 7735

7735

目前的語(yǔ)音識(shí)別系統(tǒng)在訓(xùn)練環(huán)境與測(cè)試環(huán)境匹配的情況下具有很高的識(shí)別率,而當(dāng)環(huán)境失配時(shí),其性能將急劇下降。作者研兗發(fā)現(xiàn),帶寬失配,即訓(xùn)練語(yǔ)料和測(cè)試語(yǔ)料帶寬不-致,也是引起環(huán)境失配的主要原因之一。當(dāng)測(cè)試

2018-11-28 15:21:56 3

3 交錯(cuò)式ADC之間的帶寬失配應(yīng)該是對(duì)于設(shè)計(jì)師而言最難解決的失配問(wèn)題。 如圖1所示,帶寬失配具有增益和相位/頻率分量。這使得解決帶寬失配問(wèn)題變得更為困難,因?yàn)樗袃蓚€(gè)來(lái)自其他失配參數(shù)的分量:增益和時(shí)序失配。

2020-09-27 10:44:00 0

0 交錯(cuò)式ADC之間的帶寬失配應(yīng)該是對(duì)于設(shè)計(jì)師而言最難解決的失配問(wèn)題。 如圖1所示,帶寬失配具有增益和相位/頻率分量。 這使得解決帶寬失配問(wèn)題變得更為困難,因?yàn)樗袃蓚€(gè)來(lái)自其他失配參數(shù)的分量:增益和時(shí)序失配。

2020-09-02 09:56:51 751

751

由于有限的輸入帶寬,除非您將采樣率設(shè)置得非常低,否則ADC的帶寬通常小于奈奎斯特頻率。

2021-01-14 14:35:45 19330

19330

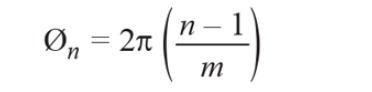

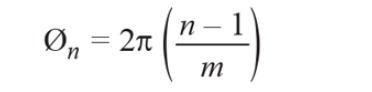

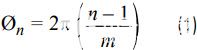

若ADC為交錯(cuò)式,則兩個(gè)或兩個(gè)以上具有固定時(shí)鐘相位差關(guān)系的ADC用來(lái)同步采樣輸入信號(hào),并產(chǎn)生組合輸出信號(hào),使得采樣帶寬為單個(gè)ADC帶寬的數(shù)倍。利用m個(gè)ADC可讓有效采樣速率增加m倍。

2021-01-04 16:20:05 1872

1872

電子發(fā)燒友網(wǎng)為你提供ADC 的時(shí)間交錯(cuò)特性討論資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-29 16:54:12 7

7 12位時(shí)間交織流水線adc的設(shè)計(jì)與通道失配分析(肇慶理士電源技術(shù)有限公司生產(chǎn)車間)-高性能的模數(shù)轉(zhuǎn)換器越來(lái)越多的應(yīng)用在國(guó)防、通信和高端家電等領(lǐng)域,是電子信息產(chǎn)業(yè)中的一項(xiàng)關(guān)鍵技術(shù)。隨著電子信息領(lǐng)域

2021-09-17 11:48:05 5

5 模數(shù)轉(zhuǎn)換器(ADC)的時(shí)間交錯(cuò)是一種根據(jù)并行應(yīng)用數(shù)個(gè)ADC來(lái)提升 整體化系統(tǒng)采樣率的方式。考驗(yàn)取決于處置各種ADC之間的失配,尤其是在較高頻率下。

2021-10-11 11:15:54 804

804 時(shí)間交錯(cuò)技術(shù)可使用多個(gè)相同的 ADC(文中雖然僅討論了 ADC,但所有原理同樣適用于 DAC 的時(shí)間交錯(cuò)特性),并以比每一個(gè)單獨(dú)數(shù)據(jù)轉(zhuǎn)換器工作采樣速率更高的速率來(lái)處理常規(guī)采樣數(shù)據(jù)序列。簡(jiǎn)單說(shuō)來(lái),時(shí)間交錯(cuò)(IL)由時(shí)間多路復(fù)用 M 個(gè)相同的 ADC 并聯(lián)陣列組成。

2022-03-10 10:35:38 2508

2508

連續(xù)時(shí)間線性均衡 (CTLE) 的值來(lái)減少 ADC 面積和功耗。由于采用了交錯(cuò)式 ADC(如閃存),因此 ADC 面積和功率隨 ADC 通道的數(shù)量而變化。

2022-07-28 08:03:10 1083

1083 電子發(fā)燒友網(wǎng)站提供《ADC in隔板用于ADC in和I/O板之間.zip》資料免費(fèi)下載

2022-08-16 10:05:30 1

1 本文介紹了一種 12 位 10GS/s 交錯(cuò) (IL) 流水線模數(shù)轉(zhuǎn)換器 (ADC)。該 ADC 采用 4 GHz 輸入信號(hào)實(shí)現(xiàn) 55 dB 的信噪比和失真比 (SNDR) 和 66 dB 的無(wú)雜散動(dòng)態(tài)范圍 (SFDR),采用 28 nm CMOS 技術(shù)制造,功耗為 2.9 W。

2022-12-15 16:32:33 1538

1538

當(dāng)ADC交錯(cuò)時(shí),使用兩個(gè)或多個(gè)具有定義時(shí)鐘關(guān)系的ADC同時(shí)對(duì)輸入信號(hào)進(jìn)行采樣,并產(chǎn)生組合輸出信號(hào),從而在單個(gè)ADC的某個(gè)倍數(shù)處產(chǎn)生采樣帶寬。利用m個(gè)ADC可將有效采樣速率提高m倍。為了簡(jiǎn)單易懂,我們將重點(diǎn)介紹兩個(gè)ADC的情況。

2022-12-21 11:46:07 1046

1046

詳解平衡系統(tǒng)的ADC尺寸、功耗、分辨率和帶寬

2022-12-22 17:56:12 1590

1590

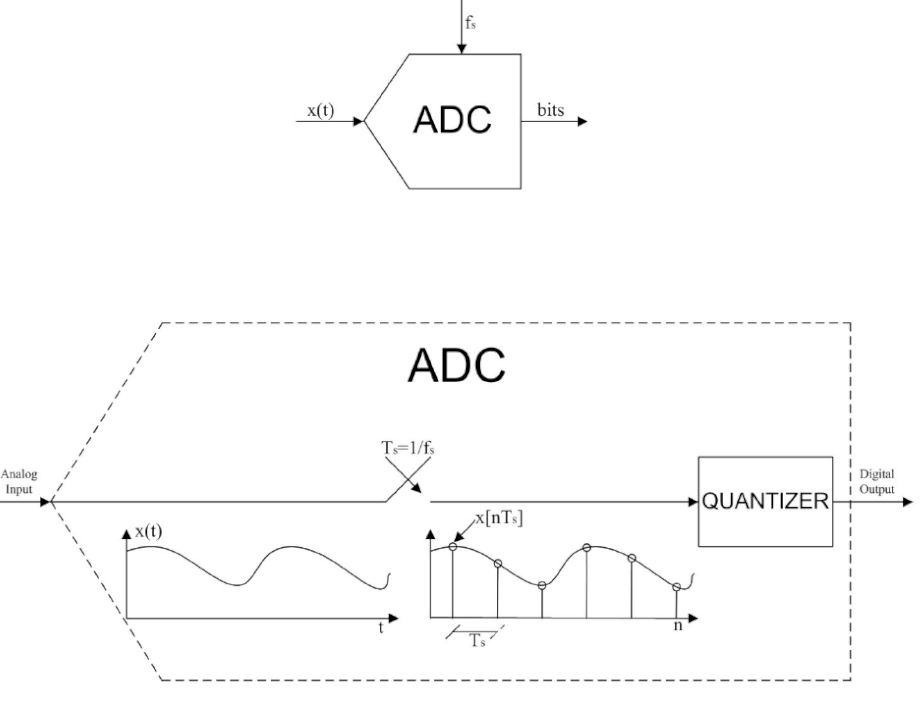

時(shí)間交錯(cuò)是一種允許使用多個(gè)相同的模數(shù)轉(zhuǎn)換器的技術(shù)[1](ADC)以比每個(gè)單獨(dú)數(shù)據(jù)轉(zhuǎn)換器的工作采樣速率更快的速率處理常規(guī)采樣數(shù)據(jù)系列。簡(jiǎn)單來(lái)說(shuō),時(shí)間交錯(cuò)(IL)包括對(duì)M個(gè)相同ADC的并行陣列進(jìn)行

2023-01-08 16:33:51 818

818

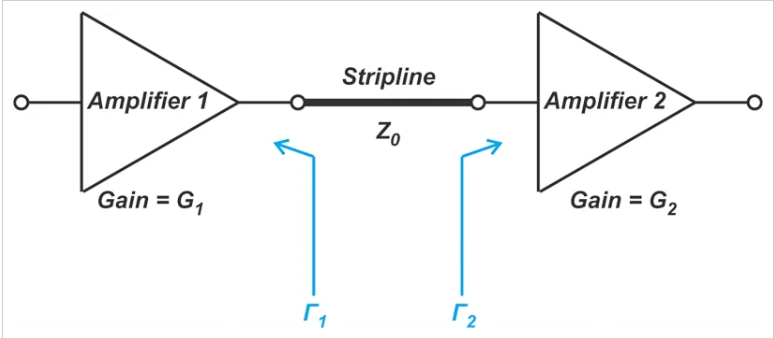

使用失配損耗方程,了解失配損耗對(duì)射頻功率測(cè)量和級(jí)聯(lián)放大器增益的影響。

2023-02-19 10:06:28 976

976 交錯(cuò)多個(gè)模數(shù)轉(zhuǎn)換器(ADC)通常是為了提高轉(zhuǎn)換器的有效采樣速率,特別是當(dāng)沒有或只有少數(shù)現(xiàn)成的ADC可以滿足此類應(yīng)用所需的采樣、線性度和交流要求時(shí)。然而,時(shí)間交錯(cuò)數(shù)據(jù)轉(zhuǎn)換器并非易事,因?yàn)榧词故褂猛耆€性的元件,增益/失調(diào)失配和時(shí)序誤差也會(huì)導(dǎo)致輸出頻譜中出現(xiàn)不希望的雜散。

2023-02-24 17:16:21 597

597

了解失配損耗對(duì)有損線路的影響、通過(guò)固定衰減器減少失配損耗的方法以及該誤差的統(tǒng)計(jì)模型。

2023-02-27 14:17:48 723

723

FFE 阻抗通常是恒定的 50Ω,但天線阻抗會(huì)根據(jù)頻段和使用條件而變化。當(dāng)存在阻抗失配時(shí),在 RFFE 和天線之間傳輸?shù)?RF 功率會(huì)減少。

2023-03-14 14:22:43 795

795 今天我們將圍繞交錯(cuò)式 ADC 轉(zhuǎn)換器展開。當(dāng) ADC 轉(zhuǎn)換器交錯(cuò)時(shí),兩個(gè)或多個(gè)具有定義的時(shí)鐘關(guān)系的 ADC 轉(zhuǎn)換器用于同時(shí)對(duì)輸入信號(hào)進(jìn)行采樣并產(chǎn)生組合輸出信號(hào),從而導(dǎo)致采樣帶寬為多個(gè)單獨(dú)的 ADC 轉(zhuǎn)換器。

2023-05-11 15:19:36 929

929

在當(dāng)今的許多細(xì)分市場(chǎng),交錯(cuò)式模數(shù)轉(zhuǎn)換器(ADC)在許多應(yīng)用中都具有多項(xiàng)優(yōu)勢(shì)。在通信基礎(chǔ)設(shè)施中,存在著一種推動(dòng)因素,使ADC的采樣速率不斷提高,以便支持多頻段、多載波無(wú)線電

2023-06-02 10:37:07 368

368

隨著電子信息技術(shù)的快速發(fā)展,模數(shù)轉(zhuǎn)換器 (ADC) 的應(yīng)用領(lǐng)域不斷拓展,而各個(gè)應(yīng)用系統(tǒng)對(duì)于ADC的要求也不斷提高。

2023-06-02 10:40:43 658

658

前面使用simplis分別介紹了交錯(cuò)CRM BOOST 過(guò)零檢測(cè)與起振信號(hào)、ON TIME控制、變頻交錯(cuò)等電路,詳見。

2023-06-23 10:36:00 567

567

通過(guò)以雙倍采樣率多路復(fù)用(例如)一對(duì)轉(zhuǎn)換器的輸出來(lái)對(duì)多個(gè)模數(shù)轉(zhuǎn)換器進(jìn)行時(shí)間交錯(cuò),現(xiàn)在已經(jīng)是一個(gè)成熟的概念——布萊克和霍奇斯于 1980 年首次提出。1, 2在設(shè)計(jì) 7 位、4MHz 模數(shù)轉(zhuǎn)換器 (ADC) 時(shí),他們確定時(shí)間交錯(cuò)解決方案需要的芯片面積比同類的 2 MHz 模數(shù)轉(zhuǎn)換器n閃存轉(zhuǎn)換器設(shè)計(jì)。

2023-06-17 15:37:39 582

582

交錯(cuò)式ADC轉(zhuǎn)換器絕對(duì)是推動(dòng)更高效接口的一部分。交錯(cuò)式ADC轉(zhuǎn)換器為系統(tǒng)設(shè)計(jì)人員提供了多種優(yōu)勢(shì)。然而,隨著轉(zhuǎn)換器帶寬的增加,需要在FPGA或ASIC中處理大量數(shù)據(jù)。必須有一些有效的方法來(lái)處理轉(zhuǎn)換器

2023-06-30 16:56:35 437

437

現(xiàn)在事情變得越來(lái)越有趣。我們一直在研究交錯(cuò)雜散的位置,并查看了偏移失配產(chǎn)生的雜散水平。通過(guò)進(jìn)行一些計(jì)算,我們能夠看到兩個(gè)交錯(cuò)ADC之間的失調(diào)失配會(huì)產(chǎn)生多大的雜散。就像我們?cè)诓榭瘩R刺的位置時(shí)所做的那樣

2023-06-30 17:18:17 786

786

使用ADC時(shí)需要重點(diǎn)關(guān)注的參數(shù)。采樣率和帶寬之間的關(guān)系是非常重要的,下面將詳細(xì)分析采樣率和帶寬之間的關(guān)系。 一、 ADC采樣率和帶寬的定義 首先,我們需要了解ADC采樣率和帶寬的定義。采樣率是指ADC每秒鐘可以采集并轉(zhuǎn)換模擬信號(hào)的次數(shù)。例如,如果ADC的采樣率為10kHz,則每秒可以將模

2023-09-12 10:51:12 6009

6009 怎么解決失配損耗對(duì)有損線路的影響? 有損線路是指在傳輸信號(hào)時(shí)會(huì)有信號(hào)衰減和失真現(xiàn)象出現(xiàn)的線路,由于其衰減和失真的特性,有時(shí)候會(huì)導(dǎo)致失配損耗的出現(xiàn),從而對(duì)傳輸信號(hào)帶來(lái)不良影響。 失配損耗是指將兩條電纜

2023-10-30 10:56:46 161

161 如何處理同軸阻抗失配?如何避免阻抗失配這種風(fēng)險(xiǎn)呢? 同軸阻抗失配是電子通信領(lǐng)域中一種常見的問(wèn)題,當(dāng)同軸電纜的輸出端口的阻抗與接收端口不匹配時(shí),就會(huì)發(fā)生阻抗失配。這種失配會(huì)導(dǎo)致信號(hào)反射、傳輸效率降低

2023-11-28 14:18:27 390

390 一文讀懂寬帶、帶寬、網(wǎng)速之間的區(qū)別與關(guān)系? 寬帶、帶寬和網(wǎng)速是在網(wǎng)絡(luò)領(lǐng)域中經(jīng)常使用的術(shù)語(yǔ),它們之間有一定的區(qū)別和關(guān)系。在深入理解寬帶、帶寬和網(wǎng)速之間的關(guān)系之前,讓我們先了解一下它們的定義。 寬帶

2024-01-31 09:11:30 304

304

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論