本文就ADSS光纜的結(jié)構(gòu)設(shè)計(jì)與光纜的性能和光纜在施工過(guò)程中的常見(jiàn)問(wèn)題的關(guān)系,闡述了針對(duì)不同地區(qū)、不同施工條件、不同環(huán)境下的ADSS光纜結(jié)構(gòu)設(shè)計(jì)的區(qū)別。并對(duì)一些常見(jiàn)施工故障進(jìn)行了簡(jiǎn)單分析。

2014-02-17 11:13:24 2267

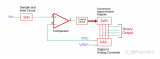

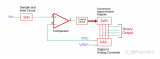

2267 SAR ADC 是逐次逼近 ADC 的簡(jiǎn)稱(successive approximation register),SAR ADC 的主要優(yōu)點(diǎn)是低功耗、小尺寸、高精度,分辨率和速度適中,采樣延時(shí)短,是一種經(jīng)濟(jì)型的 ADC 實(shí)現(xiàn)方案,故在MCU/SOC 中廣泛采用。

2023-09-08 09:57:47 6227

6227

+125°C應(yīng)用?精密SAR ADC驅(qū)動(dòng)器?精密參考電壓緩沖器?可編程邏輯控制器?測(cè)試和測(cè)量設(shè)備?電力敏感數(shù)據(jù)采集系統(tǒng)說(shuō)明OPAx625系列運(yùn)算放大器是出色的16位和18位SAR ADC驅(qū)動(dòng)器,具有高精度

2020-10-13 15:04:40

本帖最后由 hardele 于 2018-7-17 10:02 編輯

HC32L13X 系列是一款旨在延長(zhǎng)便攜式測(cè)量統(tǒng)的 電池使用壽命超低功耗、寬電壓工作范圍MCU。集成12位1M sps

2018-07-16 13:58:27

HC32L13X 系列是一款旨在延長(zhǎng)便攜式測(cè)量統(tǒng)的 電池使用壽命超低功耗、寬電壓工作范圍MCU。集成12位1M sps高精度SARADC以及集成了比較器,運(yùn)放,內(nèi)置高性能PWM定時(shí)器,LCD顯示

2018-08-13 15:49:32

中國(guó)陜西西安10k-20k誠(chéng)聘消費(fèi)類電子結(jié)構(gòu)設(shè)計(jì)大牛!!!微信;*** 郵箱:anyangyang@coolpad.com

2017-06-09 16:51:36

描述 此 TI 驗(yàn)證設(shè)計(jì)是一種使用 18 位 SAR ADC ADS8881 的高性能數(shù)據(jù)采集系統(tǒng) (DAQ),吞吐量為 1MSPS。此設(shè)計(jì)已經(jīng)過(guò)優(yōu)化,可為 10 KHz 滿標(biāo)量程輸入正弦波提供具有

2022-09-14 10:34:37

,保證行車安全。通過(guò)對(duì)標(biāo)準(zhǔn)動(dòng)車組 tNetrol-NAMC1-10-IC 型加速度傳感器工作環(huán)境進(jìn)行分析,闡述了其結(jié)構(gòu)設(shè)計(jì)的思想和方法,對(duì)結(jié)構(gòu)強(qiáng)度方面進(jìn)行了有限元仿真分析,并結(jié)合長(zhǎng)壽命隨機(jī)振動(dòng)試驗(yàn)結(jié)果驗(yàn)證結(jié)構(gòu)設(shè)計(jì)的合理性和仿真結(jié)果的準(zhǔn)確性。

2023-09-18 07:09:30

(LDO)作為其電源方案的一部分,利用它來(lái)為精密ADC產(chǎn)生低噪聲電源軌。然而,LDO的功率輸出效率非常低下,大部分功率常常作為熱量損失掉。本文討論為精密逐次逼近型(SAR) ADC實(shí)現(xiàn)更高效率電源解決方案

2018-10-19 10:22:08

AD5546是一款精密16位,乘法,低功耗,電流輸出,并行輸入數(shù)模轉(zhuǎn)換器。它采用2.7 V至5.5 V單電源供電,具有±10 V乘法參考電壓,可實(shí)現(xiàn)四象限輸出

2019-10-29 08:40:14

基于AD7793 24位Σ-Δ模數(shù)轉(zhuǎn)換器(ADC)的熱電偶溫度測(cè)量系統(tǒng)。 AD7793是一款低功耗,低噪聲,完整的模擬前端,適用于高精度測(cè)量應(yīng)用。該器件包括可編程增益放大器(PGA),內(nèi)部基準(zhǔn),內(nèi)部時(shí)鐘和激勵(lì)電流,從而大大簡(jiǎn)化了熱電偶系統(tǒng)設(shè)計(jì)

2019-08-23 08:34:55

EVAL-AD7851CB,AD7851評(píng)估板,14位A / D轉(zhuǎn)換器。 AD7851是一款高速,低功耗ADC,采用+ 5V單電源供電

2019-06-26 14:02:56

AD9481-PCB,AD9481評(píng)估板是一款8位,單芯片模數(shù)轉(zhuǎn)換器(ADC),針對(duì)高速和低功耗進(jìn)行了優(yōu)化。該產(chǎn)品體積小,易于使用,轉(zhuǎn)換速率為250 MSPS,在整個(gè)工作范圍內(nèi)具有出色的線性度和動(dòng)態(tài)

2019-11-07 06:25:57

的平臺(tái),給老司機(jī)交流的平臺(tái)。所有文章來(lái)源于項(xiàng)目實(shí)戰(zhàn),屬于原創(chuàng)。一、設(shè)計(jì)思路本文以BUCK降壓拓?fù)錇槔M(jìn)行講解,其它拓?fù)?b class="flag-6" style="color: red">結(jié)構(gòu)設(shè)計(jì)思路大同小異,BUCK降壓拓?fù)淙缦聢D:1、功率環(huán)路盡量小。基于電磁場(chǎng)...

2021-11-11 06:13:30

產(chǎn)品成本高低,是產(chǎn)品設(shè)計(jì)的主要內(nèi)容。下面就三防手持機(jī)結(jié)構(gòu)設(shè)計(jì)簡(jiǎn)述一下: 材料選擇:正確、合理地選取材料,并通過(guò)對(duì)材料輔以一定的工藝處理措施,以提高材料的耐環(huán)境變化能力。如確保外殼結(jié)構(gòu)不易變形,應(yīng)采用

2016-01-19 16:08:00

日前,德州儀器(TI)宣布推出兩款具備優(yōu)異的測(cè)量可重復(fù)性與高分辨率的+/-10V、16位模數(shù)轉(zhuǎn)換器(ADC)—ADS8519與ADS8513。這兩款產(chǎn)品將低功耗逐次逼近寄存器(SAR)ADC與采樣

2019-07-01 06:59:01

。 4. 避免假顯示:傳統(tǒng)光源(如白熾燈、鹵素?zé)簦榱说玫?b class="flag-6" style="color: red">一個(gè)較好的配光,需要配置反光杯,而LED交通信號(hào)燈采用直射光,沒(méi)有如上情況,因此亮度及射程都顯著的提高。 5.結(jié)構(gòu)設(shè)計(jì):超薄結(jié)構(gòu)設(shè)計(jì),外型美觀、工藝精細(xì)。容易組裝、拆卸、維修。使用PC外殼或不銹鋼外殼,強(qiáng)度高,壽命長(zhǎng)。紅綠燈

2011-11-08 14:59:41

設(shè)計(jì)一種能夠提供不打任何性能折扣的 ADC 驅(qū)動(dòng)拓?fù)?b class="flag-6" style="color: red">結(jié)構(gòu)是頗具挑戰(zhàn)性,特別是在圍繞一款諸如 1Msps LTC®2393-16 等超低噪聲 SAR ADC 進(jìn)行設(shè)計(jì)的時(shí)候。不管是單端

2010-12-26 15:31:07

利用由 THS4281 和 OPA333 構(gòu)成的復(fù)合緩沖器在最低功耗下實(shí)現(xiàn)所需的性能。請(qǐng)參閱更多 TI 高精度設(shè)計(jì)主要特色18 位,1Msps 取樣率DC,10kHz AC已針對(duì)低功耗和低噪聲進(jìn)行優(yōu)化

2018-07-13 14:19:05

DC2289A-B,用于LTC2368-24的演示板,具有數(shù)字濾波器的24位,1Msps低功耗SAR ADC。 LTC2368-24是低功耗,低噪聲,高速,24位SAR ADC,集成數(shù)字平均濾波器

2019-06-12 09:31:56

分享一款不錯(cuò)的一種基于FPGA高性能H.264變換量化結(jié)構(gòu)設(shè)計(jì)

2021-05-08 07:56:42

CPLD的核心可編程結(jié)構(gòu)介紹基于SRAM編程技術(shù)的PLD電路結(jié)構(gòu)設(shè)計(jì)

2021-04-08 06:51:29

變壓器結(jié)構(gòu)設(shè)計(jì)手冊(cè)內(nèi)容有:計(jì)算程序,進(jìn)品硅鋼板的牌號(hào)及其特性,導(dǎo)線尺寸截面積,鐵心各級(jí)尺寸表,三相單框鐵心,夾件,木墊塊,鐵心及夾件用零件,鐵心,鐵心裝置零件表,鐵軛沖槽,鐵心用單件,夾件絕緣等內(nèi)容.變壓器結(jié)構(gòu)設(shè)計(jì)手冊(cè)

2008-12-13 01:33:09

市面上的低功耗藍(lán)牙模塊性能比拼,總有一款你想要的

2021-05-14 06:02:29

μC/OS-II的堆棧結(jié)構(gòu)如何改進(jìn)μC/OS-II內(nèi)核的堆棧結(jié)構(gòu)設(shè)計(jì)?

2021-04-27 07:09:57

對(duì)精密16位數(shù)模轉(zhuǎn)換應(yīng)用,如何提供一款低功耗、小尺寸的解決方案?該方案的電路功能與優(yōu)勢(shì)是什么?如何進(jìn)行電源電流測(cè)量?

2021-04-07 06:37:17

為了解決傳統(tǒng)S/H電路失真大和靜態(tài)工作點(diǎn)不穩(wěn)定的問(wèn)題,采用0.25 μm BiCMOS工藝,設(shè)計(jì)了一款高速率、高精度的10位全差分BiCMOS S/H電路。文中改進(jìn)型自舉開(kāi)關(guān)電路和雙通道開(kāi)關(guān)電容共模反饋電路(CMFB)設(shè)計(jì)具有創(chuàng)新性。

2021-04-21 06:24:21

很好了,但卻沒(méi)有回答如何顯著降低運(yùn)算放大器功耗的問(wèn)題。那么我們應(yīng)該如何做呢?ADS7881 是一款 12 位 ADC,電壓輸入范圍介于 0V 至 +2.5V 之間。我選用 OPA836 作為放大器

2018-09-21 15:16:44

的建立,便攜式消費(fèi)性電子產(chǎn)品與無(wú)線功能需求越來(lái)越高、設(shè)計(jì)越來(lái)越復(fù)雜,要提高性能的同時(shí)又要兼顧低功耗,需要有一款高性能低功耗的主控MCU來(lái)作為平臺(tái)。另一方面,工業(yè)上的智能化也在展開(kāi),如遠(yuǎn)程監(jiān)控、數(shù)字化

2021-11-02 09:31:41

嵌入式系統(tǒng)軟件結(jié)構(gòu)設(shè)計(jì)

2016-09-26 13:57:25

崗位職責(zé):1、 負(fù)責(zé)公司旗下消費(fèi)電子類新產(chǎn)品開(kāi)發(fā)方案的討論和評(píng)審;2、 配合外觀設(shè)計(jì)師和電子工程師完成內(nèi)部元件排布和產(chǎn)品設(shè)計(jì);3、 完成項(xiàng)目整機(jī)結(jié)構(gòu)、零部件的詳細(xì)設(shè)計(jì);包括:建模、結(jié)構(gòu)設(shè)計(jì)、加工工藝

2016-10-08 18:14:14

成正比,而分辨率取決于寄存器的長(zhǎng)度。SAR ADC 以中低功率要求實(shí)現(xiàn)了良好的分辨率。例如,MaximIntegrated 的 MAX11665AUT-T 便是一款低成本、低功耗的 SAR ADC

2018-09-30 13:39:22

也許不需要驅(qū)動(dòng)器。讓我們來(lái)看一看SAR ADC的采樣過(guò)程和模擬輸入結(jié)構(gòu)來(lái)了解驅(qū)動(dòng)器的要求。SAR ADC的模擬輸入是一個(gè)采樣開(kāi)關(guān)、一個(gè)電阻器和采樣電容器的組合。圖1顯示針對(duì)一個(gè)SAR ADC的模擬輸入

2018-09-12 11:26:39

手機(jī)結(jié)構(gòu)設(shè)計(jì)心得

2012-11-07 09:59:50

有時(shí)間的朋友可以聯(lián)絡(luò)一下,我需要找一位音箱結(jié)構(gòu)設(shè)計(jì)師,謝謝QQ 750672359

2013-09-26 13:31:09

呈現(xiàn)效果,真正將選擇視角的主動(dòng)權(quán)還給用戶。完美幻境以“科技無(wú)極限”為主旨,專注于虛擬現(xiàn)實(shí)領(lǐng)域的科技創(chuàng)新,會(huì)始終堅(jiān)持以最尖端的科技、性能最佳的產(chǎn)品為用戶提供更加極致的科技體驗(yàn)。崗位職責(zé)能夠獨(dú)立完成產(chǎn)品結(jié)構(gòu)設(shè)計(jì)

2015-09-25 15:46:01

結(jié)構(gòu)設(shè)計(jì)師發(fā)布日期2014-01-24工作地點(diǎn)廣東-中山市學(xué)歷要求不限工作經(jīng)驗(yàn)不限招聘人數(shù)1待遇水平面議年齡要求性別要求不限有效期2014-02-04職位描述1、熟悉產(chǎn)品設(shè)計(jì)流程及結(jié)構(gòu)設(shè)計(jì),能合理

2014-01-24 13:43:52

LT5926是一款由 LT32A01 的 32 位 MCU 與 2.4GHz 藍(lán)芽無(wú)線收發(fā)器,所集成的低成本、低功耗、高集成度整合芯片。藍(lán)芽部分集成了發(fā)射器、接收器、頻率綜合器,與 GFSK

2018-05-20 23:57:10

LT5926是一款由 LT32A01 的 32 位 MCU 與 2.4GHz 藍(lán)芽無(wú)線收發(fā)器,所集成的低成本、低功耗、高集成度整合芯片。藍(lán)芽部分集成了發(fā)射器、接收器、頻率綜合器,與 GFSK

2018-06-25 08:28:30

[tr=transparent]LT5926是一款由 LT32A01 的 32 位 MCU 與 2.4GHz 藍(lán)芽無(wú)線收發(fā)器,所集成的低成本、低功耗、高集成度整合芯片。藍(lán)芽部分集成了發(fā)射器、接收器

2018-05-13 22:14:18

MS616F512是一款低功耗16位RISC的MCU,可完美替代進(jìn)口的MSP430F448。MS616F512 具有五種低功耗模式,可以大大延長(zhǎng)便攜式設(shè)備中電池壽命。數(shù)字振蕩器(DCO)可以在6μs

2021-07-16 11:20:31

操作系統(tǒng)結(jié)構(gòu)設(shè)計(jì) 操作系統(tǒng)有多種實(shí)現(xiàn)方法與設(shè)計(jì)思路,下面僅選取最有代表性的三種做一簡(jiǎn)單的敘述。 1.整體式系統(tǒng)結(jié)構(gòu)設(shè)計(jì) 這是最常用的一種組織方式,它常被譽(yù)為“大雜燴”,也可說(shuō),整體式系統(tǒng)結(jié)構(gòu)

2011-09-13 10:10:56

有誰(shuí)接觸過(guò)在低功耗方面不錯(cuò)的處理器嗎?推薦一款

2013-03-13 16:15:24

找一款12V轉(zhuǎn)5V的電壓芯片,空載情況下,盡可能的電流小,因?yàn)槭怯秒姵刈鲭娫矗?b class="flag-6" style="color: red">低功耗,我現(xiàn)在用的LM2842,靜態(tài)功耗為1.5mA。大家能不能推薦一款這樣的芯片,靜態(tài)電流最好比1.5mA還小。

2019-05-21 00:40:36

求一款低功耗電源管理IC,LDO跟DC-DC都可以,技術(shù)參數(shù)要求如下:輸入3.6V;輸出2.8V;當(dāng)輸出端什么都不接處于空載狀態(tài)時(shí),該IC消耗電流為1uA。且該IC滿載電流不能低于300mA,可在

2016-12-07 18:27:09

各位前輩好,求推薦一款低功耗高精度差分運(yùn)放ic,輸入共模電壓在mV量級(jí),供電電壓允許5V以下,所需增益大約4V/V。用在干電池供電的板子上希望功耗低一些。萌新先謝謝了!

2019-12-20 03:30:27

因本人所做項(xiàng)目是用電池供電,需要一款低功耗的LDO,封裝為sot23,要求超低功耗,靜態(tài)電流,10ua以下,低噪聲,低壓差,最大輸出電流大于300ma。求各位推薦下,謝謝了!

2017-08-14 22:20:28

` 產(chǎn)品結(jié)構(gòu)設(shè)計(jì)是根據(jù)產(chǎn)品功能而進(jìn)行的內(nèi)部結(jié)構(gòu)的設(shè)計(jì),是機(jī)械設(shè)計(jì)的主要內(nèi)容之一。產(chǎn)品結(jié)構(gòu)設(shè)計(jì)內(nèi)容有零件的分件、部件的固定方式、產(chǎn)品使用和功能的實(shí)現(xiàn)方式、產(chǎn)品使用材料和表面處理工藝等。要求產(chǎn)品結(jié)構(gòu)設(shè)計(jì)

2016-02-25 17:24:27

我司現(xiàn)招收硬件工程師、結(jié)構(gòu)設(shè)計(jì)各2名,詳情如下,公司:湖南博宏信息技術(shù)有限公司工作地點(diǎn):廣州番禺公司主營(yíng)產(chǎn)品:終端機(jī)、讀卡器、平板等硬件工程師職責(zé):1.負(fù)責(zé)終端機(jī)的配件選型,包括配件的組裝、調(diào)試等

2014-10-13 10:22:28

蝶式五軌滑蓋結(jié)構(gòu)設(shè)計(jì)與磁動(dòng)力滑蓋結(jié)構(gòu)設(shè)計(jì)的不同之處在哪?

2021-07-28 06:57:34

上實(shí)現(xiàn)。在這一層作出的功耗優(yōu)化包括:1器件選擇,利用自動(dòng)調(diào)節(jié)門(mén)的尺寸來(lái)實(shí)現(xiàn)低功耗設(shè)計(jì)。2通過(guò)邏輯優(yōu)化減少開(kāi)關(guān)活動(dòng)性,減少毛刺。或者對(duì)開(kāi)關(guān)活動(dòng)性高的節(jié)點(diǎn)、連線合理配置。3合理的布局布線,減少線間電容.。4

2013-05-16 20:00:33

想請(qǐng)大家?guī)兔ν扑]一款電源開(kāi)關(guān)芯片,12V的電壓, 我以前用的是英飛凌的BTS443,因?yàn)檫@個(gè)芯片靜態(tài)電流太大,我想換一款低功耗的,麻煩大家推薦一下,萬(wàn)分的感謝!

2019-02-26 06:36:12

幫忙推薦一款適用于海上地震勘探的24位低功耗ADC ,感謝!!!

2019-01-15 11:21:04

軟件結(jié)構(gòu)設(shè)計(jì),,

2016-09-26 13:55:28

ASIC、FPGA和DSP的應(yīng)用領(lǐng)域呈現(xiàn)相互覆蓋的趨勢(shì),使設(shè)計(jì)人員必須在軟件無(wú)線電結(jié)構(gòu)設(shè)計(jì)中重新考慮器件選擇策略問(wèn)題。本文從可編程性、集成度、開(kāi)發(fā)周期、性能和功率五個(gè)方面論述了選擇ASIC、FPGA

2019-07-26 06:09:25

,但一般比Δ-ΣADC快。 SAR ADC的功耗與采樣率成線性關(guān)系。例如,如果SAR ADC在1Msps時(shí)的功耗為5mW,那么1ksps時(shí)的功耗一般為5μW。因此,SAR ADC非常靈活,客戶庫(kù)存一款

2018-08-28 14:41:33

。 CS5555 是一款高精度、低功耗 Sigma-Delta 模數(shù)轉(zhuǎn)換芯片,內(nèi)置 1 路 Sigma-Delta ADC。ADC 采用三階 Sigma-Delta 調(diào)制器,通過(guò)低雜訊儀用放大器結(jié)構(gòu)實(shí)現(xiàn) PGA

2021-10-14 16:17:39

是一款高精度、低功耗 Sigma-Delta 模數(shù)轉(zhuǎn)換芯片,內(nèi)置 1 路 Sigma-Delta ADC。ADC 采用三階Sigma-Delta 調(diào)制器,通過(guò)低雜訊儀用放大器結(jié)構(gòu)實(shí)現(xiàn) PGA 放大,放大

2021-10-14 14:45:44

XM24L 是一款高精度、低功耗 Sigma-Delta 模數(shù)轉(zhuǎn)換芯片,內(nèi)置一路 Sigma-Delta ADC,一路差分輸入通道和一路溫度感測(cè)器感,ADC 采用兩階 sigma delta 調(diào)制器

2021-10-14 14:30:49

通過(guò)對(duì)輥型設(shè)備的結(jié)構(gòu)設(shè)計(jì)和改進(jìn),重點(diǎn)闡述兩種輥型方法,以滿足客車不同部位蒙皮成型的要求。關(guān)鍵詞:客車蒙皮;輥型設(shè)備;結(jié)構(gòu)設(shè)計(jì);工藝改進(jìn)Abstract :Through designing and improv

2009-07-25 15:25:36 11

11 結(jié)構(gòu)設(shè)計(jì)方面資料

2010-08-09 17:02:35 0

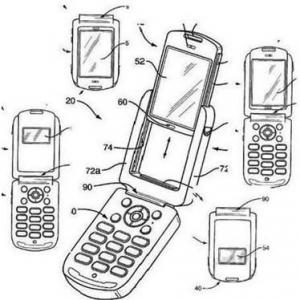

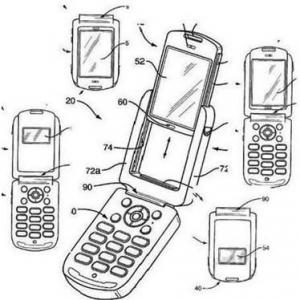

0 手機(jī)結(jié)構(gòu)設(shè)計(jì)手冊(cè)

翻蓋部分零部件明細(xì)圖

設(shè)計(jì)進(jìn)行的步驟

零部件詳細(xì)設(shè)計(jì)介紹

2010-09-13 16:00:07 0

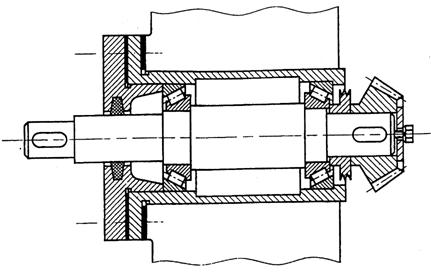

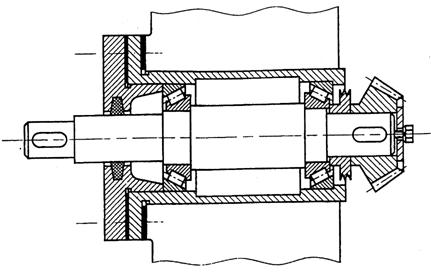

0 實(shí)驗(yàn)六 軸系結(jié)構(gòu)設(shè)計(jì)實(shí)驗(yàn)一、實(shí)驗(yàn)?zāi)康模?熟悉并掌握軸系結(jié)構(gòu)設(shè)計(jì)中有關(guān)軸的結(jié)構(gòu)設(shè)計(jì)、滾動(dòng)軸承組合設(shè)計(jì)的基本方法。

二、實(shí)

2009-03-13 19:04:06 56282

56282

手機(jī)結(jié)構(gòu)設(shè)計(jì)專利精選

2009-06-18 10:23:25 2309

2309

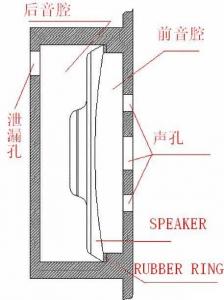

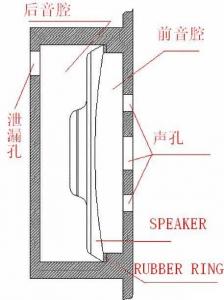

手機(jī)音腔的結(jié)構(gòu)設(shè)計(jì)

先說(shuō)單speaker,現(xiàn)在用的最多的了!不過(guò)從發(fā)展趨勢(shì)來(lái)看為追求好的音效雙speaker

2009-06-18 10:31:30 4135

4135

手機(jī)結(jié)構(gòu)設(shè)計(jì)的基本準(zhǔn)則

總原則:結(jié)構(gòu)設(shè)計(jì)力求合理,模具制作簡(jiǎn)單,裝配方便,省時(shí)省料。1. 在滿足設(shè)計(jì)要求的前提下,

2009-06-18 10:37:49 1140

1140 HFC網(wǎng)絡(luò)典型結(jié)構(gòu)設(shè)計(jì)和注意問(wèn)題

2011-11-08 17:27:28 35

35 輪輻轉(zhuǎn)子的結(jié)構(gòu)設(shè)計(jì)_馮艷琴

2017-01-02 16:30:30 0

0 半替代護(hù)環(huán)的結(jié)構(gòu)設(shè)計(jì)_張國(guó)喜

2017-01-07 16:52:06 0

0 低壓低功耗運(yùn)算放大器結(jié)構(gòu)設(shè)計(jì)

2017-03-05 15:00:06 0

0 慣性閉鎖開(kāi)關(guān)的結(jié)構(gòu)設(shè)計(jì)與分析_許馬會(huì)

2017-03-19 19:04:39 0

0 本文主要介紹了面向散熱仿真分析的大功率光伏逆變器的結(jié)構(gòu)設(shè)計(jì)所涉及到的技術(shù)分析。

2017-10-10 10:38:18 24

24 3D3S 鋼結(jié)構(gòu)設(shè)計(jì) 工具書(shū)

2017-10-20 10:13:53 0

0 本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)據(jù)庫(kù)概念結(jié)構(gòu)是如何設(shè)計(jì)的概念結(jié)構(gòu)設(shè)計(jì)資料概述主要內(nèi)容包括了:1 概念結(jié)構(gòu)2 概念結(jié)構(gòu)設(shè)計(jì)的方法與步驟3 數(shù)據(jù)抽象與局部視圖設(shè)計(jì)4 視圖的集成

2018-10-26 11:49:13 22

22 為大家介紹一款24位高性能,超低功耗,SAR型ADC——AD7767.

2019-07-29 06:17:00 3679

3679 產(chǎn)品設(shè)計(jì)中所涉及的產(chǎn)品結(jié)構(gòu)設(shè)計(jì),主要是產(chǎn)品的外部殼體結(jié)構(gòu)設(shè)計(jì)。目前殼體材料主要是金屬材料通過(guò)鈑金沖壓工藝成型和塑料通過(guò)注塑工藝成型。常見(jiàn)產(chǎn)品的結(jié)構(gòu)設(shè)計(jì)主要有鈑金結(jié)構(gòu)的設(shè)計(jì)、塑料產(chǎn)品的結(jié)構(gòu)設(shè)計(jì)

2021-05-26 14:21:27 1911

1911 產(chǎn)品結(jié)構(gòu)設(shè)計(jì)在工業(yè)設(shè)計(jì)中扮演著很重要的角色。一個(gè)產(chǎn)品的橫空出世必須結(jié)構(gòu)的合理,搭配各式的產(chǎn)品零部件,從而實(shí)現(xiàn)產(chǎn)品的各項(xiàng)功能,最終得以進(jìn)行生產(chǎn)制造,這是產(chǎn)品結(jié)構(gòu)設(shè)計(jì)的價(jià)值體現(xiàn)。 在工業(yè)設(shè)計(jì)中所

2021-05-31 15:23:11 902

902 ±10V真雙極SAR ADC

2021-04-22 08:53:55 14

14 電子發(fā)燒友網(wǎng)為你提供在功耗敏感型應(yīng)用中利用高效率 超低功耗開(kāi)關(guān)穩(wěn)壓器為精密SAR ADC供電資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-29 08:44:45 8

8 DSP中MAC的微系統(tǒng)結(jié)構(gòu)設(shè)計(jì)(高頻開(kāi)關(guān)電源技術(shù)指標(biāo))-該文檔為DSP中MAC的微系統(tǒng)結(jié)構(gòu)設(shè)計(jì)總結(jié)文檔,是一份不錯(cuò)的參考資料,感興趣的可以下載看看,

2021-09-22 13:24:39 3

3 一款交直流一體充電樁的結(jié)構(gòu)設(shè)計(jì)(電源技術(shù)期刊的審稿流程)-一款交直流一體充電樁的結(jié)構(gòu)設(shè)計(jì)

2021-09-24 17:26:13 27

27 pogopin彈簧針的內(nèi)部結(jié)構(gòu)設(shè)計(jì)常見(jiàn)有反鉆孔、斜剖面、增加圓珠等結(jié)構(gòu),每種結(jié)構(gòu)應(yīng)用不同。

2022-01-14 12:11:53 1271

1271 《抑制開(kāi)關(guān)磁阻電機(jī)振動(dòng)的結(jié)構(gòu)設(shè)計(jì)研究》pdf

2022-01-23 10:49:04 3

3 《通信電纜結(jié)構(gòu)設(shè)計(jì)》pdf

2022-02-08 14:50:53 0

0 O型圈密封結(jié)構(gòu)設(shè)計(jì)

2022-02-10 15:56:20 16

16 在一個(gè)SoC的系統(tǒng)結(jié)構(gòu)設(shè)計(jì)中,除了硬件結(jié)構(gòu)以外,軟件結(jié)構(gòu)的設(shè)計(jì)對(duì)整個(gè)SoC的性能有很大的影響。

2023-09-25 15:14:31 548

548 隨著高速電路的不斷涌現(xiàn),PCB板的復(fù)雜度也越來(lái)越高,為了避免電氣因素的干擾,信號(hào)層和電源層必須分離,所以就牽涉到多層PCB的設(shè)計(jì),即疊層結(jié)構(gòu)設(shè)計(jì)。——PCB疊層結(jié)構(gòu)設(shè)計(jì)10大通用原則——多層板常用的疊層結(jié)構(gòu)講解——多層板制造:如何做好疊層與阻抗匹配?

2022-09-30 12:03:38 107

107 FPC的結(jié)構(gòu)設(shè)計(jì)

2023-03-01 15:37:41 0

0 電子發(fā)燒友網(wǎng)站提供《異步FIFO結(jié)構(gòu)設(shè)計(jì).pdf》資料免費(fèi)下載

2024-02-06 09:06:27 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論