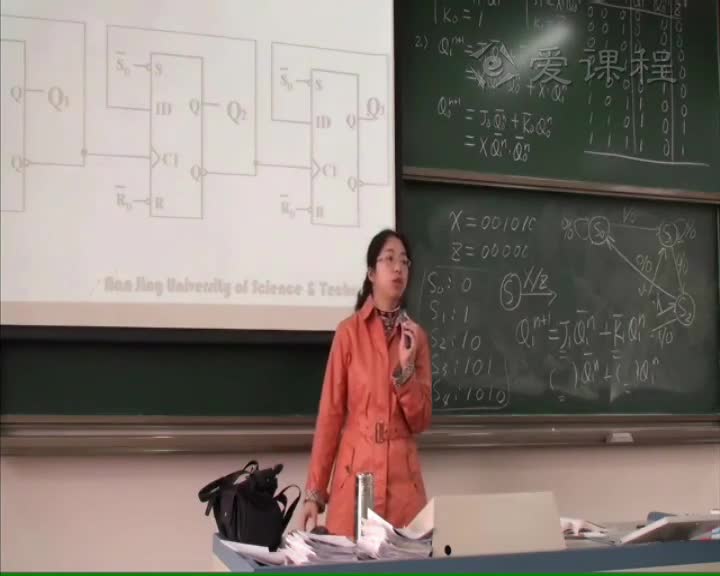

在數字電路中,凡是任一時刻的穩(wěn)定輸出不僅決定于該時刻的輸入,而且還和電路原來狀態(tài)有關者都叫時序邏輯電路。時序邏輯電路結構示意圖如圖2-41所示。時序邏輯電路的狀態(tài)是靠具有存儲功能的觸發(fā)器所組成的存儲電路來記憶和表征的。

2018-01-31 09:27:23 53525

53525

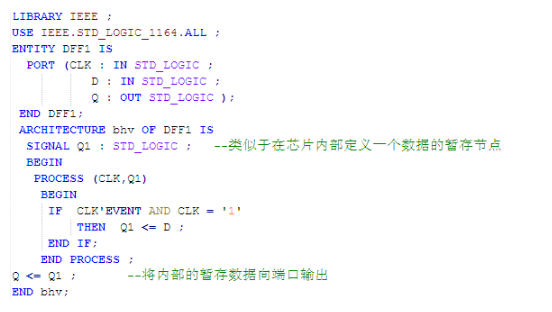

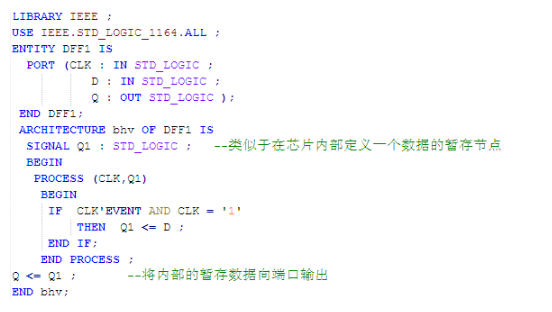

用VHDL文本設計觸發(fā)器,觸發(fā)器的類型可任選一種。給出程序設計、仿真分析、硬件測試及詳細實驗過程。

2020-08-21 17:53:34 1522

1522

了解嗎? (1)純組合邏輯電路的缺點在哪? (3)純組合邏輯電路完成不了什么功能? (2)為什么需要時鐘和寄存器呢? 帶著這三個疑問我們來認識一下時序邏輯電路。 二. 同步時序邏輯電路的作用 1. 時序邏輯電路對于組合邏輯的毛刺具有容忍度,

2020-12-25 14:39:28 4147

4147

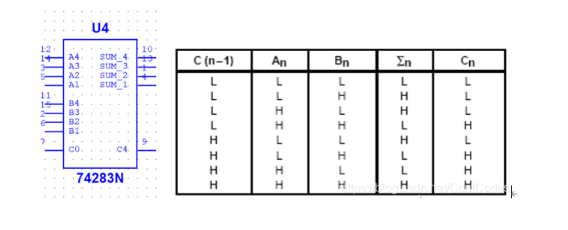

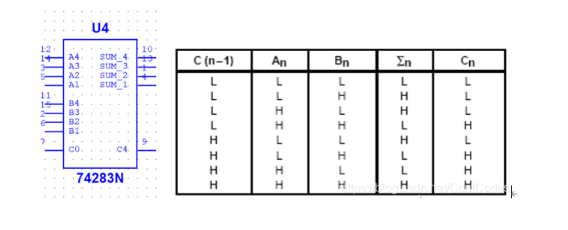

用兩片加法器芯片74283配合適當的門電路完成兩個BCD8421碼的加法運算。(輸入兩個以BCD8421碼表示的十進制數,輸出也是以BCD8421碼表示的和,并用數碼管顯示出來。)

2020-10-20 13:57:55 13027

13027

時序邏輯電路的精華——計數器

2022-12-29 09:23:56 1011

1011 時序邏輯電路的特點

2019-10-08 05:34:53

時序邏輯電路的設計實驗1 進一步強化EDA仿真軟件的使用;2 掌握利用MSI

2009-03-19 15:10:18

時序邏輯電路設計6.1 基本D觸發(fā)器的設計6.2 JK觸發(fā)器6.3 帶異步復位/置位端的使能T觸發(fā)器6.4 基本計數器的設計6.5 同步清零的計數器6.6 同步清零的可逆計數器6.7 同步預置數的計數器

2009-03-20 10:04:53

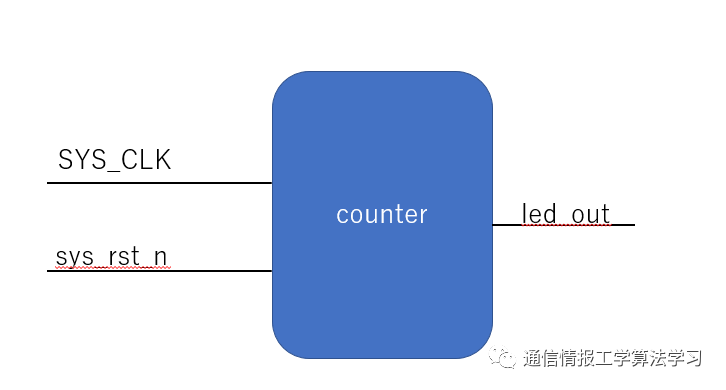

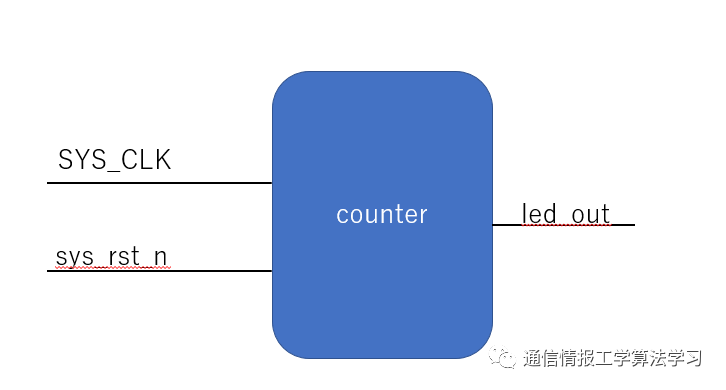

時序邏輯電路設計之計數器實驗目的:以計數器為例學會簡單的時序邏輯電路設計實驗平臺:芯航線FPGA核心板實驗原理: 時序邏輯電路是指電路任何時刻的穩(wěn)態(tài)輸出不僅取決于當前的輸入,還與前一時刻輸入形成

2019-01-24 06:35:16

夏宇聞老師(數字系統(tǒng)設計)十六章復雜時序邏輯電路設計關于i2c電路的設計,很好的練習了verilog 中task以及嵌套時序邏輯電路case的設計,而且加深了對i2c的理解和對eeprom的功能

2015-01-26 19:13:11

了博主jiangyi_love 的一篇文章,轉載過來,我們大家共同學習。在工程應用中,雙向電路是設計者不得不面對的問題.在實際應用中,數據總線往往是雙向的.如何正確處理數據總線是進行時序邏輯電路設計

2012-04-01 18:18:14

fpga時序邏輯電路的分析和設計 時序邏輯電路的結構及特點時序邏輯電路——任何一個時刻的輸出狀態(tài)不僅取決于當時的輸入信號,還與電路的原狀態(tài)有關。[hide][/hide]

2012-06-20 11:18:44

本帖最后由 芯航線跑堂 于 2016-12-25 01:52 編輯

時序邏輯電路設計之計數器實驗目的:以計數器為例學會簡單的時序邏輯電路設計實驗平臺:芯航線FPGA核心板實驗原理:時序邏輯電路

2016-12-21 19:15:54

為什么FPGA可以用來實現組合邏輯電路和時序邏輯電路呢?

2023-04-23 11:53:26

Verilog程序模塊的結構是由哪些部分組成的?如何去實現時序邏輯電路和組合邏輯電路的設計呢?

2021-11-03 06:35:57

和連線的特性做了簡要介紹之后,深入分析了數字設計的核心——反相器,并逐步將這些知識延伸到組合邏輯電路、時序邏輯電路、控制器、運算電路以及存儲器這些復雜數字電路與系統(tǒng)的設計中。為了反映數字集成電路設計進入

2009-02-12 09:51:07

筆試時也很常見。[例1] 一個簡單的狀態(tài)機設計--序列檢測器序列檢測器是時序數字電路設計中經典的教學范例,下面我們將用Verilog HDL語言來描述、仿真、并實現它。序列檢測器的邏輯功能描述:序列

2021-08-18 07:00:00

設計時序邏輯電路時,如何解決電路不能自啟動的問題?

是如何解決電路不能自啟動,不是‘不能自啟動’的定義

2023-05-10 14:44:22

多輸入時序電路的基本原理是什么?基于數據選擇器和D觸發(fā)器的多輸入時序邏輯電路設計

2021-04-29 07:04:38

組合邏輯電路的基本模塊是什么?時序邏輯電路怎樣進行工作的?

2021-09-18 09:19:42

1 進一步強化EDA仿真軟件的使用;2 掌握利用MSI、可編程器件設計時序邏輯電路的特點、方法;3 掌握時序邏輯電路的調試方法;4&

2009-03-18 20:06:31 47

47 時序邏輯電路的輸出不但和當前輸入有關,還與系統(tǒng)的原先狀態(tài)有關,即時序電路的當前輸出由輸入變量與電路原先的狀態(tài)共同決定。為達到這一目的,時序邏輯電路從某一狀態(tài)

2009-03-18 22:13:04 71

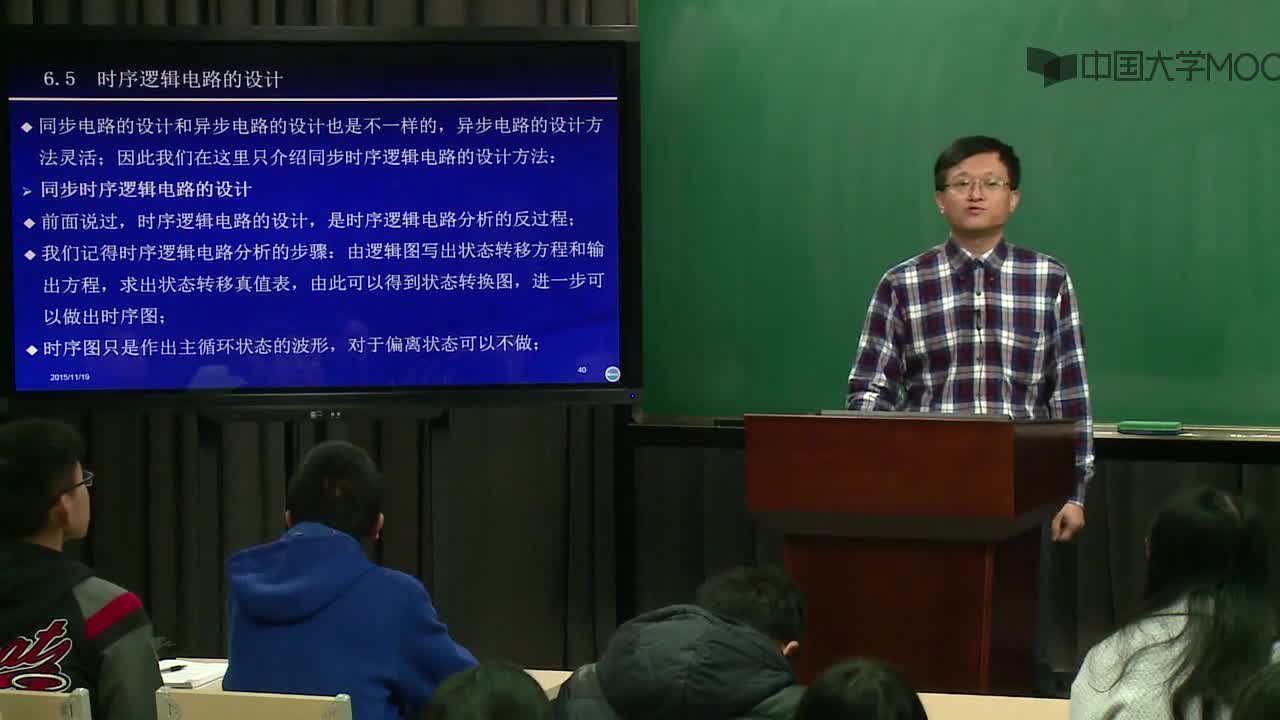

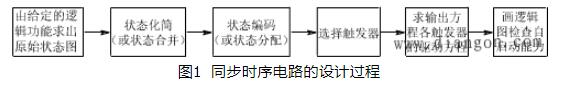

71 同步時序邏輯電路:本章系統(tǒng)的講授同步時序邏輯電路的工作原理、分析方法和設計方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

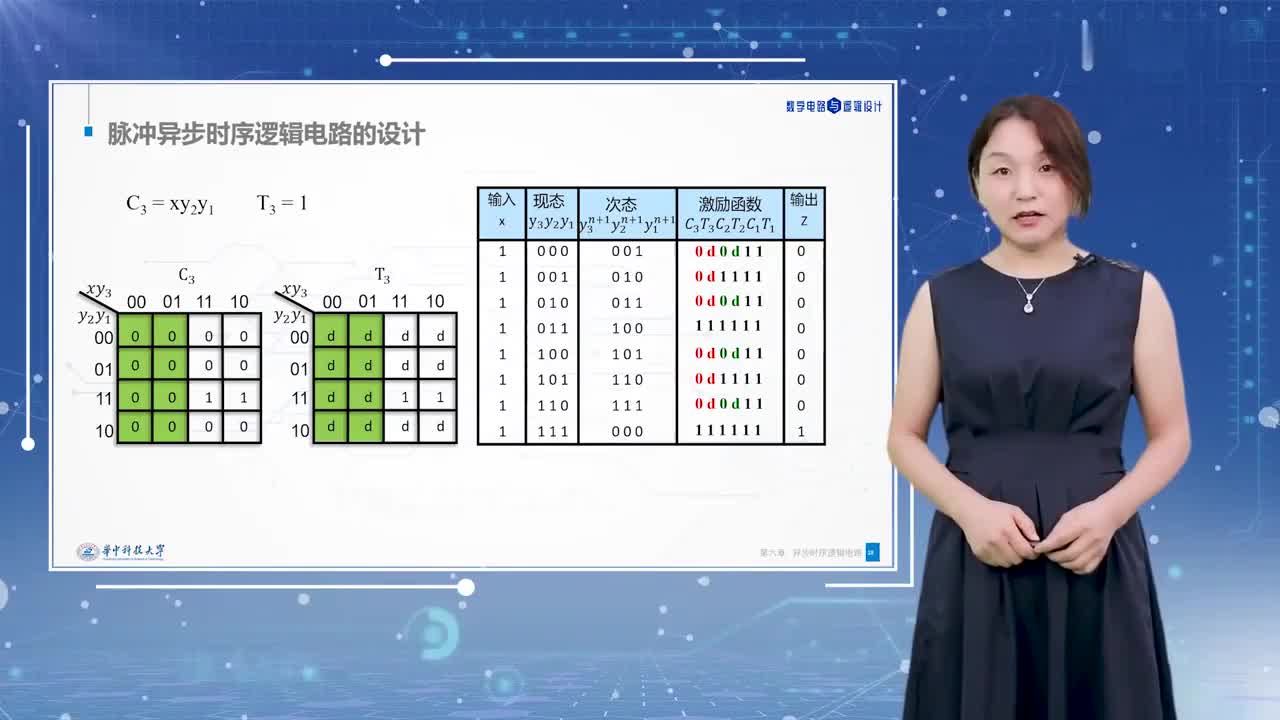

0 異步時序邏輯電路:本章主要從同步時序邏輯電路與異步時序邏輯電路狀態(tài)改變方式不同的特殊性出發(fā), 系統(tǒng)的介紹異步時序邏輯電路的電路結構、工作原理、分析方法和設計方法。

2009-09-01 09:12:34 0

0 提出了從狀態(tài)轉換圖中直接求得觸發(fā)器的置位和復位函數,從而確定觸發(fā)器的驅動方程這樣一種設計同步時序邏輯電路的新方法.設計原理簡單,易于理解,適合于所有同步時序

2010-02-28 19:23:02 15

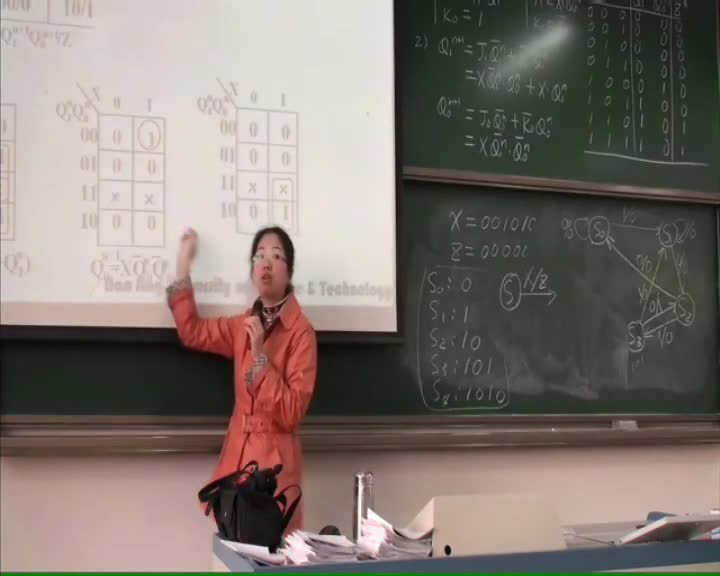

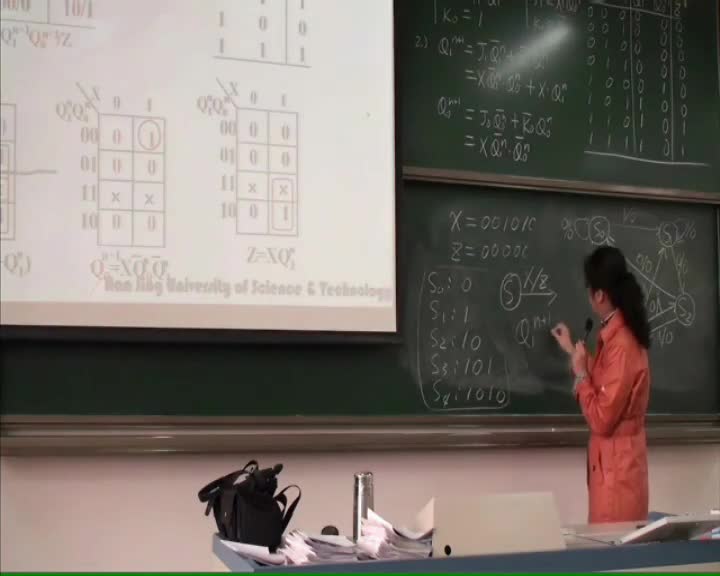

15 摘要:通過實際例子,闡述了次態(tài)卡諾圖在分析和設計時序邏輯電路中的使用方法。該方法的使用可以使時序邏輯電路的分析和設計得到一定的簡化,過程中思路清晰,狀態(tài)轉換直

2010-04-28 10:03:10 21

21 摘要:本文對數字邏輯電路關于同步時序邏輯電路設計的關鍵步驟中,引入代數理論輔助設計作了一些探討,并用實例表明這樣的努力使設計過程得到了大大的簡化。關鍵詞:同

2010-04-29 09:35:20 12

12 講述組合邏輯電路設計基礎

2010-05-06 10:29:15 0

0 數字邏輯電路設計課程

數字邏輯電路的設計包括兩個方面:基本邏輯功能電路設計和邏輯電路系統(tǒng)設計。關于基本邏輯功能電路設計一般在《數字電路技術基礎

2010-05-24 16:05:50 0

0 數字邏輯電路按邏輯功能和電路組成的特點可分為組合邏輯電路和時序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 數字邏輯電路可分為組合邏輯電路和時序邏輯電路兩大類。組合邏輯電路在任一時刻的穩(wěn)定輸出只取決于當前的輸入,而與過去的輸入無關。在結構上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 數字電路分為組合邏輯電路(簡稱組合電路)和時序邏輯電路(簡稱時序電路)兩類。在第三章中討論的電路為組合電路。組合電路的結構模型如圖4.1所示,它的輸出函數表達式為

2010-08-13 15:23:02 24

24 在討論時序邏輯電路的分析與設計之前,讓我們先回顧一下在第四章中介紹過的時序電路結構框圖和一些相關術語。時序電路的結構框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 數字集成電路,根據原理可分為兩大類,既組合邏輯電路和時序邏輯電路。

組合邏輯電路的組成是邏輯門電路。電路的輸出狀態(tài)僅由同一時刻的輸入狀態(tài)決定,與電路的原

2010-08-18 15:05:23 55

55 實驗十六 時序邏輯電路? 實驗(1) 計數器?一、實驗目的?⒈ 熟悉計數器的設計方法及工作原理。?⒉ 了解同步計數器與異步計數器的區(qū)別。?⒊ 應用

2008-09-24 22:17:08 3210

3210

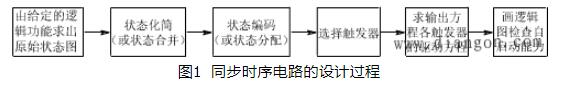

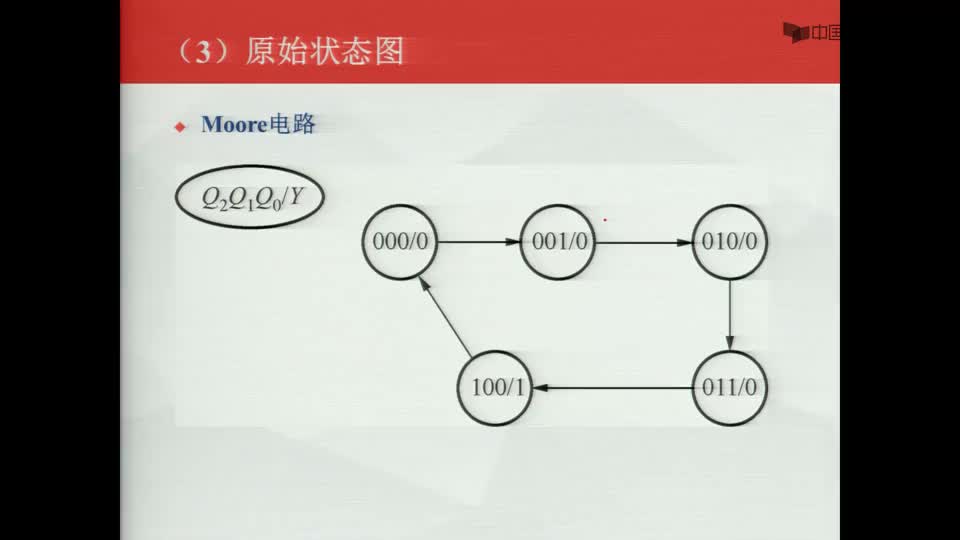

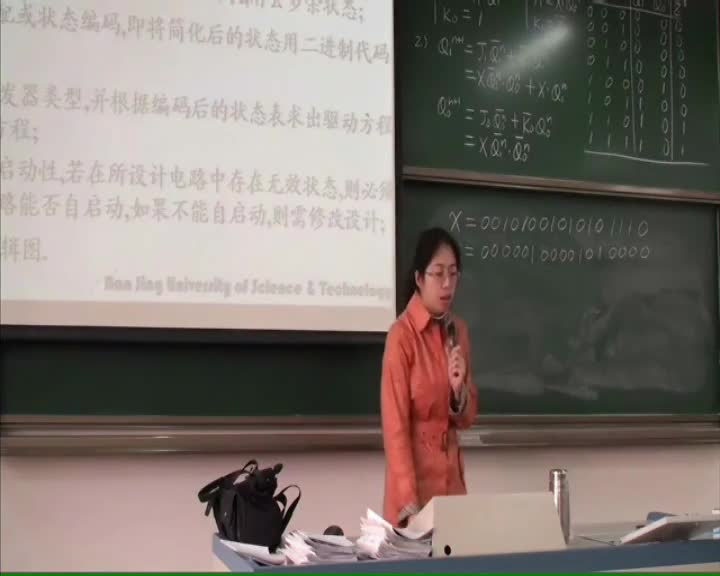

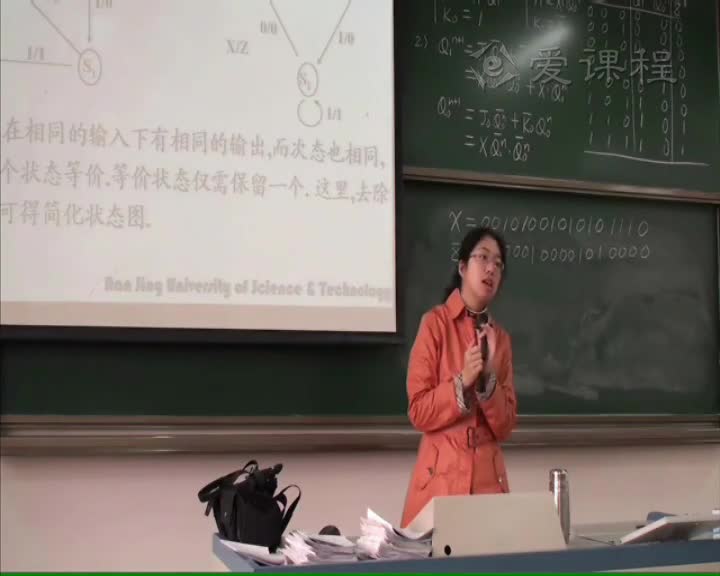

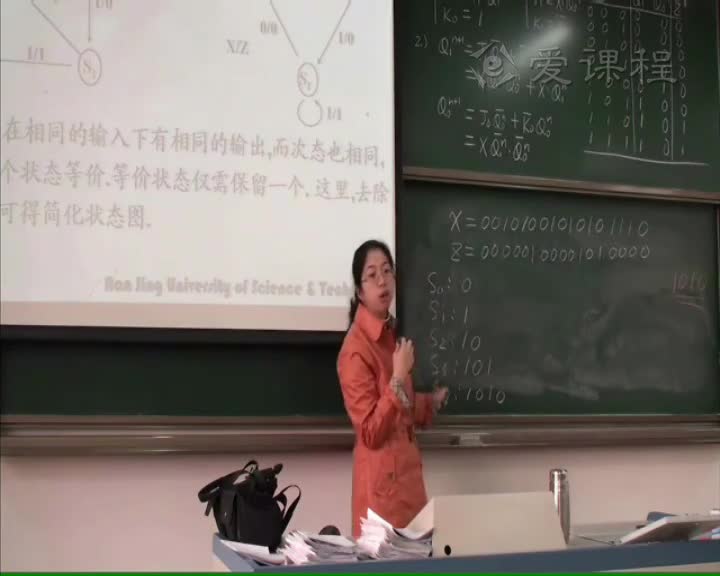

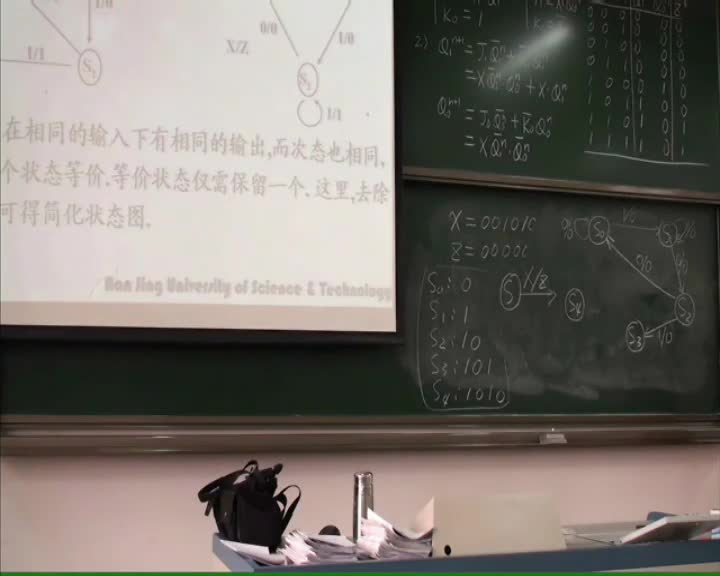

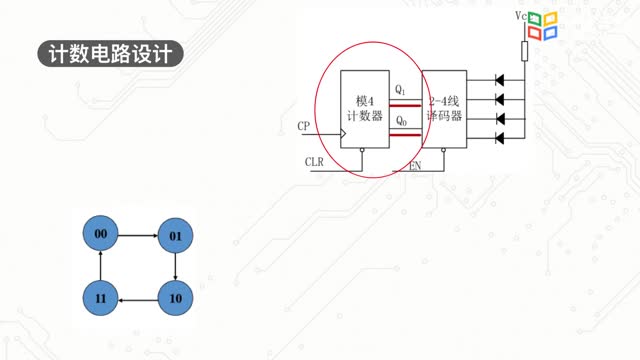

第二十七講 同步時序邏輯電路的設計

7.5 同步時序邏輯電路的設計用SSI觸發(fā)器16進制以內7.5.1 同步時序邏輯電路的設計方法

2009-03-30 16:31:56 3438

3438

時序邏輯電路的分析方法

1. 時序邏輯電路的特點 在時序邏輯電路中,任意時刻的輸出信號不僅取決于當時的輸入信

2009-04-07 23:18:11 8146

8146

時序邏輯電路分析實例

例1 分析圖所示電路的邏輯功能。設起始狀態(tài)是

2009-04-07 23:20:25 4398

4398

時序邏輯電路的特點

在第三章所討論的組合邏輯電路中,任一時刻的輸出信號僅僅取決于該時刻的輸入信號,而與電路原來

2009-09-30 18:19:22 9900

9900

在SSI時序邏輯電路設計中,遵循的設計準則是:在保證所設計的時序邏輯電路具有正確功能的前提下,觸發(fā)器的激勵函數應最小化,從而簡化電路結構。用卡諾圖法或公式法

2010-08-13 09:22:23 2860

2860

在工程應用中,雙向電路是設計者不得不面對的問題.在實際應用中,數據總線往往是雙向的.如何正確處理數據總線是進行時序邏輯電路設計的基礎.在程序設計過程中,關鍵技術在于:實體部

2011-11-11 10:27:13 2830

2830 通過介紹Multisim軟件的功能和特點,結合格雷瑪計數器的設計實例,敘述了在Multisim軟件平臺進行時序邏輯電路的設計原理及構成方法,并利用軟件對設計進行仿真。

2012-02-10 16:43:10 133

133 電子發(fā)燒友網核心提示 :RS 232接口是現在最常用的一種通信接口。隨著FPGA技術的高速發(fā)展,一些常見的接口電路的時序電路可以通過FPGA實現,通過這種設計可減少電路系統(tǒng)元件的數量

2012-11-27 10:28:11 5937

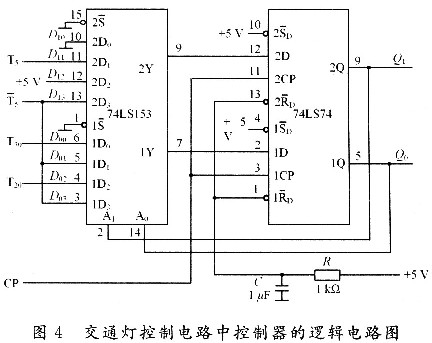

5937 定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計定時控制器邏輯電路設計

2015-12-17 18:18:50 0

0 電子專業(yè)單片機相關知識學習教材資料之時序邏輯電路的分析與設計

2016-09-02 14:30:26 0

0 時序邏輯電路其任一時刻的輸出不僅取決于該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發(fā)器、計數器、寄存器等。由于時序邏輯電路具有存儲或記憶的功能,檢修起來就比較復雜。

2018-04-09 16:00:00 5673

5673

組合邏輯電路和時序邏輯電路都是數字電路,組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關。而時序邏輯電路在邏輯功能上的特點是任意時刻的輸出不僅取決于當時的輸入信號,而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關。

2018-01-30 17:26:04 91327

91327

分析時序邏輯電路也就是找出該時序邏輯電路的邏輯功能,即找出時序邏輯電路的狀態(tài)和輸出變量在輸入變量和時鐘信號作用下的變化規(guī)律。上面講過的時序邏輯電路的驅動方程、狀態(tài)方程和輸出方程就全面地描述了時序邏輯電路的邏輯功能。

2018-01-30 18:55:32 123040

123040

本文開始介紹了時序邏輯電路的特點和時序邏輯電路的三種邏輯器件,其次介紹了時序邏輯電路的組成與時序邏輯電路檢修方法,最后介紹了時序邏輯電路的應用舉例。

2018-03-01 10:53:38 106881

106881

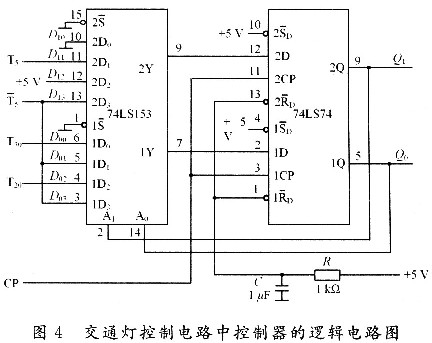

實驗包括了:組合邏輯電路設計,時序邏輯電路設計,異步計數器的設計,全加器的設計,七段數碼管顯示電路的設計,信號發(fā)生器設計,四人搶答器設計,有限狀態(tài)機的設計,交通燈控制器設計,數字鐘設計,出租車計費器設計,頻率計的設計還有管腳PIN的資料

2018-09-12 08:00:00 22

22 本文檔的主要內容詳細介紹的是數字電路基礎教程之時序邏輯電路的詳細資料概述。內容包括了:1.時序邏輯電路分析2.若干常用時序邏輯電路3.時序邏輯電路設計

2018-10-17 08:00:00 0

0 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-02-26 15:22:20 30485

30485 時序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時序邏輯電路有觸發(fā)器、 寄存器和計數器等。

2019-02-26 15:25:01 49628

49628 組合邏輯電路是任意時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態(tài)無關。而時序邏輯電路不僅僅取決于當前的輸入信號,而且還取決于電路原來的狀態(tài),或者說,還與以前的輸入有關。

2019-02-26 15:32:30 62616

62616 選定觸發(fā)器的類型后,根據狀態(tài)轉換圖(或狀態(tài)轉換表)和選定的狀態(tài)編碼,觸發(fā)器的類型,寫出電路的狀態(tài)方程、驅動方程和輸出方程。

2019-05-20 17:07:26 24424

24424

一 實驗目的 掌握Mealy型時序電路設計方法。驗證所設計電路的邏輯功能。體會狀態(tài)分配對電路復雜性的影響

2019-06-25 08:00:00 1

1 本文檔的主要內容詳細介紹的是模擬電路教程之時序邏輯電路的課件資料免費下載包括了:1 概述,2 時序邏輯電路的分析方法,3 若干常用的時序邏輯電路,4 時序邏輯電路的設計方法。

2020-06-22 08:00:00 13

13 筆試時也很常見。 [例1] 一個簡單的狀態(tài)機設計--序列檢測器 序列檢測器是時序數字電路設計中經典的教學范例,下面我們將用Verilog HDL語言來描述、仿真、并實現它。 序列檢測器的邏輯功能描述

2021-08-10 16:33:55 6561

6561

筆試時也很常見。[例1] 一個簡單的狀態(tài)機設計--序列檢測器序列檢測器是時序數字電路設計中經典的教學范例,下面我們將用Verilog HDL語言來描述、仿真、并實現它。序列檢測器的邏輯功能...

2021-12-17 18:28:40 15

15 從今天開始新的一章-Circuits,包括基本邏輯電路、時序電路、組合電路等。

2022-10-10 15:39:01 875

875 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2023-03-14 17:06:50 4816

4816

本文旨在總結近期復習的數字電路D觸發(fā)器(邊沿觸發(fā))的內容。

2023-05-22 16:54:29 9071

9071

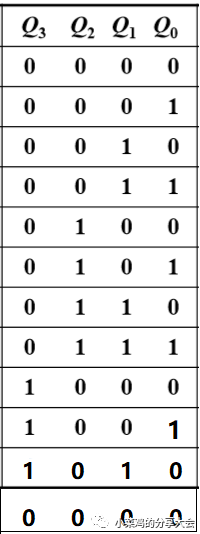

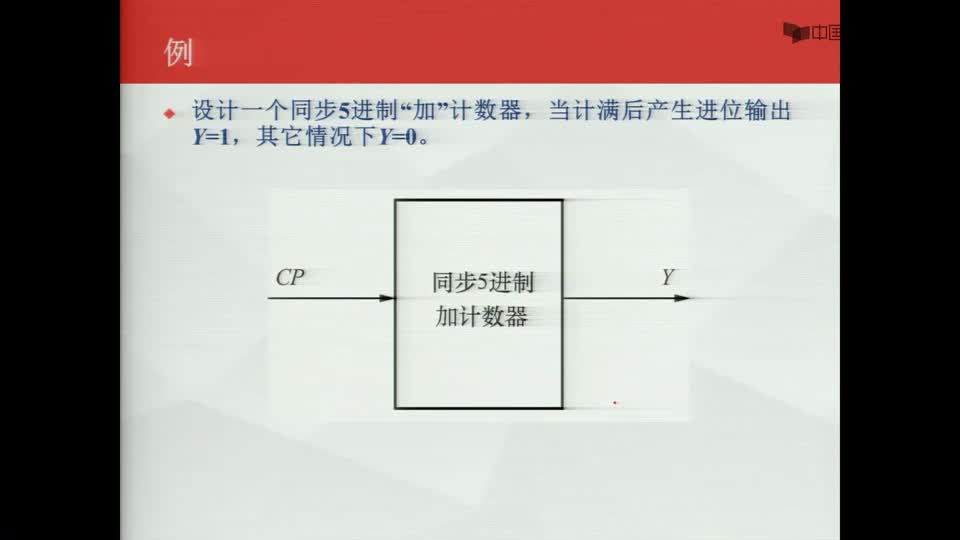

前面已經學習了時序邏輯電路中的基本單元:觸發(fā)器,這次就用其來整點活,實現計數器的設計,計數器可以說是任何和時序有關的設計都會用到他。

2023-05-22 16:54:50 2503

2503

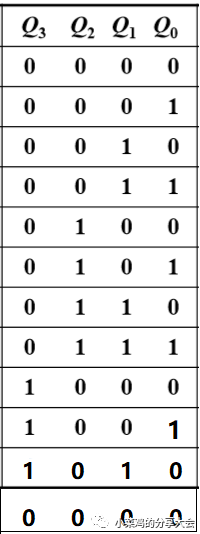

時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關問題進行討論,重點介紹時序邏輯電路的核心部分——計數器。

2023-05-22 17:01:29 1882

1882

上文介紹了同步計數器的設計原則以及各注意事項,本文承接上文繼續(xù)介紹異步計數器以及三種常用的集成計數器的相關內容。

2023-05-22 17:07:57 2823

2823

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發(fā)器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發(fā)器功能,尤其是各種觸發(fā)器的特征方程與觸發(fā)模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 1983

1983

?時序邏輯電路分為同步時序邏輯電路和異步時序邏輯電路兩大類。

2023-06-21 14:35:58 2539

2539

時序邏輯電路是一種能夠存儲信息并根據時鐘信號按照特定順序執(zhí)行操作的電路。它是計算機硬件中非常重要的一部分,用于實現存儲器、時序控制器等功能。與之相對的是組合邏輯電路,它根據輸入信號的組合情況,立即

2024-02-06 11:18:34 499

499

電子發(fā)燒友App

電子發(fā)燒友App

評論