?

本文所研究的電子系統認證芯片是基于硬加密技術采用專用集成電路(ASIC)設計的方法來實現的。由于ASIC上有特殊算法,PCB和一些硬件可能被復制,但是無法復制ASIC的加密數據,保密性更強。該芯片采用RSA加密算法,它是非對稱密鑰密碼體制的代表,其安全性在于找到兩個大素數p和q比較容易;但目前沒有有效的方法從p和q的乘積N中分解出p和q。有專家建議,普通公司使用1 024位的密鑰就可以保證資料的安全性,因此該系統認證芯片采用密鑰為1 024位的RSA加密算法。

該電子系統認證芯片采用SMIC 0.18μm 6層金屬工藝,在SoC Eneounter平臺上進行物理設計。為了了解整個芯片的布線擁塞程度和功耗的大概情況,進行正式設計之前,對該芯片進行預設計;通過預設計的結果分析芯片的布線擁塞情況,并對布局布線后的功耗進行預估。在分析預設計的基礎上,針對預設計中存在的問題對芯片進行詳細的電源規劃,為整個芯片設計出一個合理的供電網絡,使最終的設計實現面積優化,并且滿足功耗、時序等要求。

1 功耗預估

預設計采用75%的利用率,對該電子系統認證芯片進行了粗略的布圖規劃,僅設計了寬度為10 μm的電源環。為了使芯片功耗的分析結果更接近實際,對該芯片進行了布局、時鐘樹綜合和詳細布線等步驟。在時序收斂的前提下,進行功耗分析,工作電壓VDD為1.8 V,得到芯片的總功耗為115.41 mW,包括開關功耗(Switehing Power)、內部功耗(Internal Power)和泄露功耗(Leakage Power)。但是芯片中存在IRDrop違規(即芯片中的電壓降超過了5%VDD),如圖1所示,左上角的對話框中列出了存在IR Drop違規的地方,具體位置在版圖中的深色區域。一般情況下,5%的電壓降會增大10%~15%的線延遲,會產生時序違規,使芯片處于不正常的工作狀態,因此,需要在后續設計中進行詳細的電源規劃。

?

采用75%的利用率進行詳細布線后發現,版圖中的布線擁塞情況并不嚴重,Meta15和Meta16的布線資源均比較寬裕。一些研究表明,芯片成本與芯片面積的4次方成正比。為了降低成本,應盡可能減小芯片面積。經過反復嘗試之后,確定芯片的利用率為80%,芯片內核(Core)面積約為2.474 mm2,總面積約為3.5 mm2,比預設計時減小了約0.12 mm2。

2 電源規劃

在該電子系統認證芯片的預設計階段,存在IRDrop的違規,因此必須通過電源規劃來設計芯片的供電網絡,以消除IR Drop違規。電源規劃的總體步驟包括全局電源網絡的連接、電源/地Pad規劃、電源環的設計和電源條的設計。

2.1 連接全局電源

全局電源網絡的連接是指把相應的端口和網絡連接到合適的電源和接地網絡上,從而使整個芯片供電網絡的設計以及后續的步驟可以順利完成。可以通過選擇“Floorplan”菜單列表中的“Connect Global Net”選項進行連接,也可以通過在終端中輸入命令“global-NetCon-nect”進行連接。

2.2 電源/地Pad規劃

2.2.1 確定供電Pad的數量

根據功耗分析所得芯片內核正常工作的功耗值,根據式(1)可以計算出所需給內核供電的電源/地Pad的最小數量m。

?

式中:PAVG為芯片內核正常工作時的平均功耗;VPAD和IPAD分別是為內核供電的I/O Pad正常條件下供電電壓和所能提供的最大電流,這里的VPAD即為芯片內核的工作電壓VDD;k為調整因子,根據芯片的實際情況,最小取1~2,最大可取5~10。

在SMIC的0.18μm I/O單元說明文檔中,給出了電源/地單元結構中的最小金屬寬度。PLVDD*和PLVSS*系列的最小金屬寬度為70 μm。根據所給出的最小金屬寬度,可以計算出相應的I/O Pad可以提供多少電流,如式(2)所示:

?

式中:Cd是由工藝決定的電流密度上限。一般情況下,Metall到Meta15均為1.0 mA/μm,在銅工藝情況下,頂層金屬Meta16在110℃為1.6 mA/μm。因此可得設計中所應用的I/O單元可以提供70 mA的電流。

以75%的利用率中預跑后端設計的結果可得,芯片功耗為115.41mW,工作電壓為1.8V,代入式(1)可得,該電子系統認證芯片所需的內核供電Pad的數量為1對,給I/O單元供電的Pad數量也為1對,并且將兩者的地Pad短接,以使整個I/O單元的電源環有更好的ESD保護性能。

2.2.2 供電Pad位置的確定

供電Pad在芯片中可以起到很好的隔離干擾和降低噪聲的作用,在供電Pad的擺放上,可以考慮以下因素:

(1)將電源/地Pad放置在同時跳變的信號Pad中進行隔離,防止信號相互干擾;

(2)最好能在時鐘信號Pad的兩端用地Pad隔離,從而屏蔽信號跳變對時鐘信號的干擾;

(3)為了保證整個芯片內核電源網絡的供電均勻,減少電壓降和電遷移,將電源/地Pad均勻分布在芯片的四周;

(4)由于復位信號Pad容易受噪聲影響,可以利用電源/地Pad來減低噪聲;

(5)Pad的排布還需要考慮最終芯片的封裝,其排列要便于封裝時引線,盡量避免封裝時產生焊接線交叉,并要符合封裝的設計規則(如最小Pad間距、最大的拐角和最大的金線長度等)。

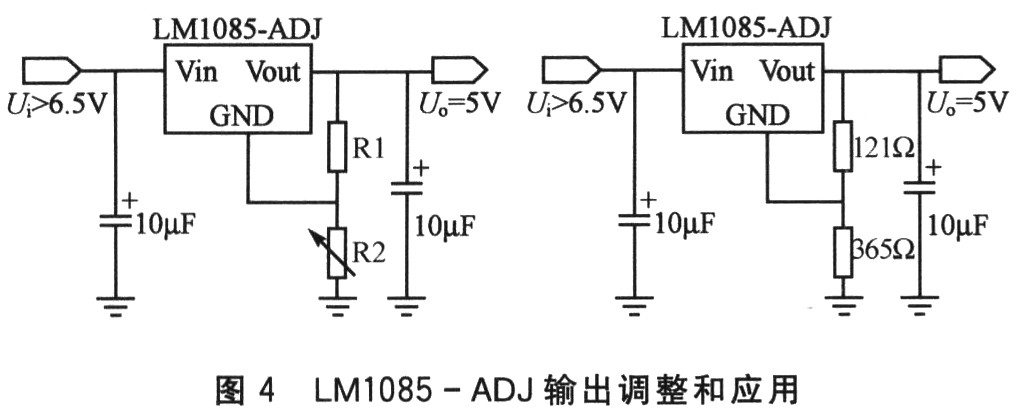

2.3 電源環的設計

在電源規劃階段,電源環指的是Core Ring,即給芯片內核供電的電源環。它是連接供電I/O Pad和標準單元的橋梁,通過Core Ring就可以實現供電I/O Pad為標準單元以及硬核供電。

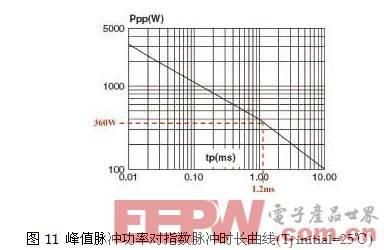

電源環的總寬度是根據整個芯片的供電峰值電流以及廠家設計規則中所允許的電流密度來決定的,可由式(3)估算出所需電源環的總寬度Wring:

?

式中:Ip為芯片的峰值電流;Cd為廠家工藝庫所給出的電流密度的上限,與式(2)中的定義是一樣的;k為調整因子,根據芯片的供電I/O單元分布決定。

由于Core Ring是四邊的,每邊承擔1/4的電流,因此電源環總寬度除以4就是每邊Core Ring的總寬度。在電源環的設計中,單個電源環的寬度不可超過廠家所規定的寬線規則,以避免打孔。單個電源環寬度w的計算如下所示:

?

式中:n為電源環的對數。

由式(3)可得所需電源環的總寬度為64.117μm。為了有效減小電源環所占據的芯片面積,該設計采用雙層電源環的設計,橫向采用Met-a13,Meta15;縱向采用Meta14,Meta16,因此n為2,由式(4)可得w為8.015 μm。為了給整個芯片的功耗預留一定的冗余量,并且金屬線的寬度足夠寬,可以降低由于電遷移導致的電路失效,從反復實踐中得出,單個電源環的寬度取15 μm,可以滿足該芯片電遷移和電壓降的要求,設計好的電源環如圖2所示。

?

最后,根據文檔中提供的Rom核工作所需的最大電流值,設計Block Ring為Rom供電。

2.4 電源條的設計

為了解決芯片預設計時內部IR Drop違規的問題,通過設計電源條(Power Stripe)來減小芯片內部的電壓降。電源條分為橫向和縱向,縱向電源條寬度設為WV,橫向電源條寬度設為WH,縱向電源條的間距設為SV,橫向電源條的間距設為SH。一般來說,由于在橫向有很多標準單元的電源/地線,因此需要的橫向電源條線比縱向電源條線要少很多。

對于WV,WH和SV,SH的設定,有以下幾個經驗規則:

(1)WV一般取垂直布線間距(Pitch)的整數倍,其目的是充分利用布線通道。取值不能太大,一般情況下不超過最小二輸入與非門寬度的4倍。

每一層金屬的Pitch在物理庫中都有相應的定義。SMIC的0.18μm工藝庫中所定義的Meta11~Meta16的Pitch如表1所示。

?

SMIC的0.18μm工藝庫中最小二輸入與非門的寬度為1.98μm。因此,若采用Meta12或Meta14作為縱向電源條,WV取0.66~7.92μm之間0.66的整數倍值;若采用Meta16作為縱向電源條,則WV取0.95~7.92μm之間0.95的整數倍值。

(2)WH的取值一般是標準單元高度的整數倍,通常選擇1倍或2倍;也可以將電源條線的寬度設為整數。SMIC 0.18μm工藝庫中標準單元的高度為5.04μm,則橫向電源條的寬度取5.04μm或10.08μm。

(3)在電源條金屬層的選擇上,根據LEF的規定,縱向選擇偶數層,橫向選擇奇數層。由于高層金屬具有較小的寄生電阻,用高層金屬走線可以有效地減小電壓降。

(4)確定電源條線的寬度后,需要計算其間距SV,SH。可根據文獻中提出的方法進行計算。

如圖3所示的電源網格,在估算出Core內部橫/縱向供電金屬條寬基礎上,可以求出功耗為P的總電流JTOTAL=P/VDD。

?

?

假設圖3中A點有5%的電壓降,那么位于A點其有效電阻分別為:

?

?

式中:RVW和RHW分別是豎直方向和水平方向的參考方塊電阻。

假設N為縱向電源條線的對數,M為橫向電源條線的對數,則其值分別為:

?

最后,若所設計的縱向電源條和橫向電源條是均勻分布在芯片內核,則縱向電源網格的間距SV和橫向電源網格的間距SH分別為:

?

首先對縱向電源條進行設計。由于電源條位于芯片內部,將占據一定的布線資源,而布線器一般是優先選用底層金屬開始布線,因此頂層金屬的布線資源比較寬裕。并且,頂層金屬比其他層金屬要厚一些,電氣性能也要好一些,多使用頂層金屬對減小IR Drop有著很大的幫助。因此選用Meta16作為縱向電源條。根據實際情況,縱向電源條的寬度WV取為7.6 μm。芯片內核區域的寬度W為1 578.085μm,高度H為1 567.44μm,因此由上述公式可得該系統認證芯片所需電源條的總對數N為5.749,取N=6,即在芯片內核區域均勻放置6對寬度為7.6μm的Meta16電源條,每對電源條之間的間距為225.44μm。

接著進行橫向電源條的設計。選用高層金屬Meta15作為橫向電源條,寬度取為5.04μm,由上述公式可得,所需橫向電源條的總寬度為87.424 μm。但是,實際上并不需要這么多電源條,因為標準單元的電源/地都通過Metal1連接到芯片內核的兩端,并且與縱向電源條相連。該設計共有標準單元行(Row)312行,每行有1對0.4μm的橫向電源條,相當于有312×0.4=124.8μm的電源條,大于所需的橫向電源條總寬度,已經足夠供應整個芯片,使水平方向的電壓降小于VDD×5%=0.09 V。

為了使水平方向的電壓降更小,設計了3對寬度為5.04 μm的Metal5層橫向電源條,均勻分布在芯片內核區域。電源條的設計結果如圖4所示。

?

經過后續物理設計后,在滿足時序收斂的前提下,最終詳細布線后電源網絡VDD功耗分析的結果如表2所示,可看出,電源規劃的設計很好地改善芯片內部的IR Drop,最終芯片內部不存在IR Drop的違規,滿足了功耗要求,如圖5所示。

?

3 結語

本文主要討論了基于RSA算法的電子系統認證芯片的電源規劃。基于SMIC 0.18μm工藝,首先對該芯片進行預設計,通過對預設計進行功耗預估和布線擁塞程度的分析結果,在正式設計時提高了芯片利用率,減小了芯片的面積;并且通過詳細的電源規劃(包括雙層電源環和電源條的設計等)消除了預設計時存在的電壓降違規,使該電子系統認證芯片最終滿足功耗要求和時序收斂。

電子發燒友App

電子發燒友App

評論