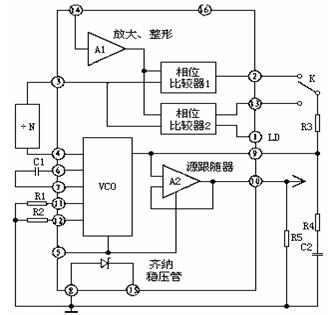

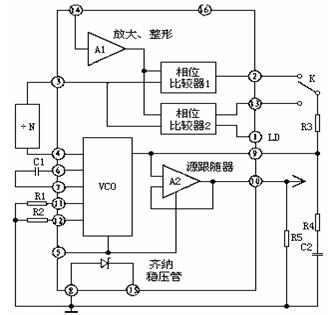

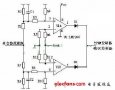

現在常使用集成電路的鎖相環CD4046,是通用的CMOS鎖相環集成電路,其特點是電源電壓范圍寬(為3V-18V),輸入阻抗高(約

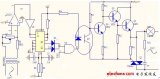

1腳相位輸出端,環路入鎖時為高電平,環路失鎖時為低電平。2腳相位比較器Ⅰ的輸出端。3腳比較信號輸入端。13腳相位比較器Ⅱ的輸出端。14腳信號輸入端。對相位比較器Ⅱ而言,當14腳的輸入信號比3腳的比較信號頻率低時,輸出為邏輯“

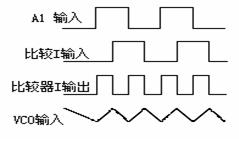

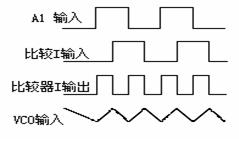

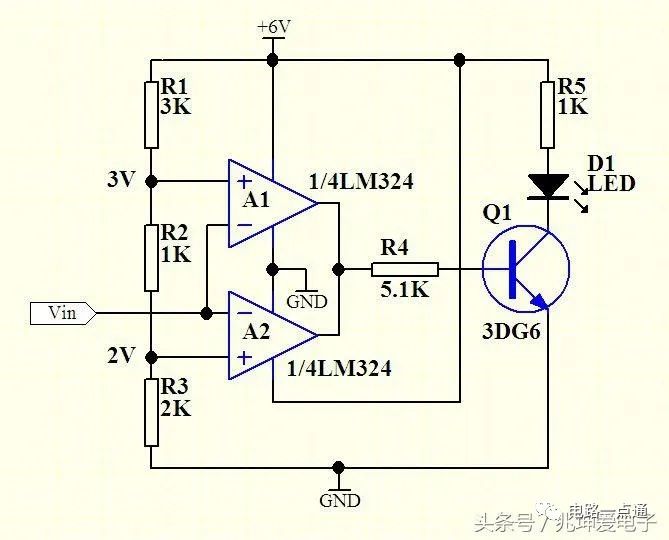

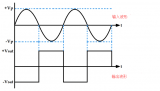

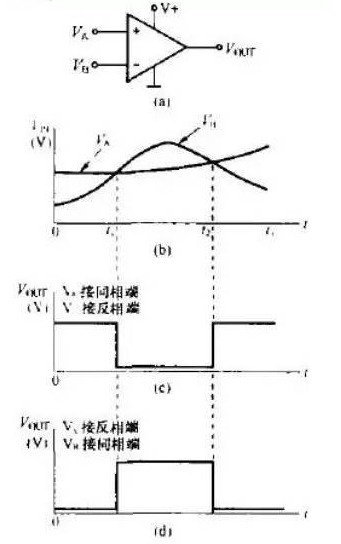

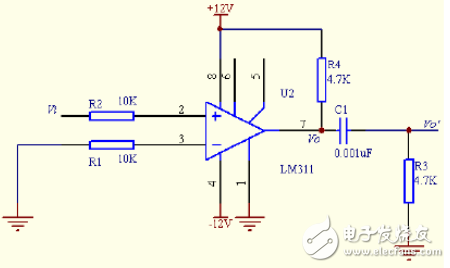

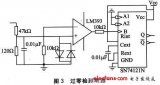

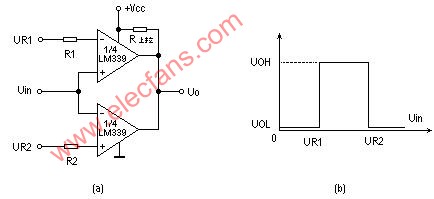

圖2.13 比較器輸出波形圖

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

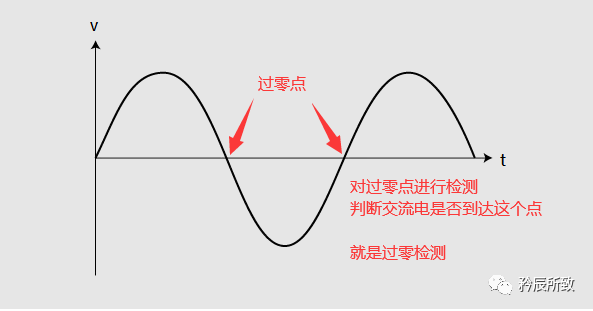

電子發燒友網>電子技術應用>電子技術>電路圖>信號處理電子電路圖>過零比較和相位比較電路原理圖

現在常使用集成電路的鎖相環CD4046,是通用的CMOS鎖相環集成電路,其特點是電源電壓范圍寬(為3V-18V),輸入阻抗高(約

1腳相位輸出端,環路入鎖時為高電平,環路失鎖時為低電平。2腳相位比較器Ⅰ的輸出端。3腳比較信號輸入端。13腳相位比較器Ⅱ的輸出端。14腳信號輸入端。對相位比較器Ⅱ而言,當14腳的輸入信號比3腳的比較信號頻率低時,輸出為邏輯“

圖2.13 比較器輸出波形圖

相關推薦

1144

1144

1494

1494

2187

2187

1140

1140 66

66 18

18 32

32 9221

9221

119615

119615

120303

120303

95936

95936

68374

68374

87506

87506

36037

36037

8956

8956

6508

6508

20525

20525

12875

12875

21744

21744

10828

10828

8444

8444

15089

15089

評論