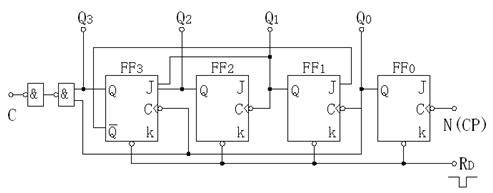

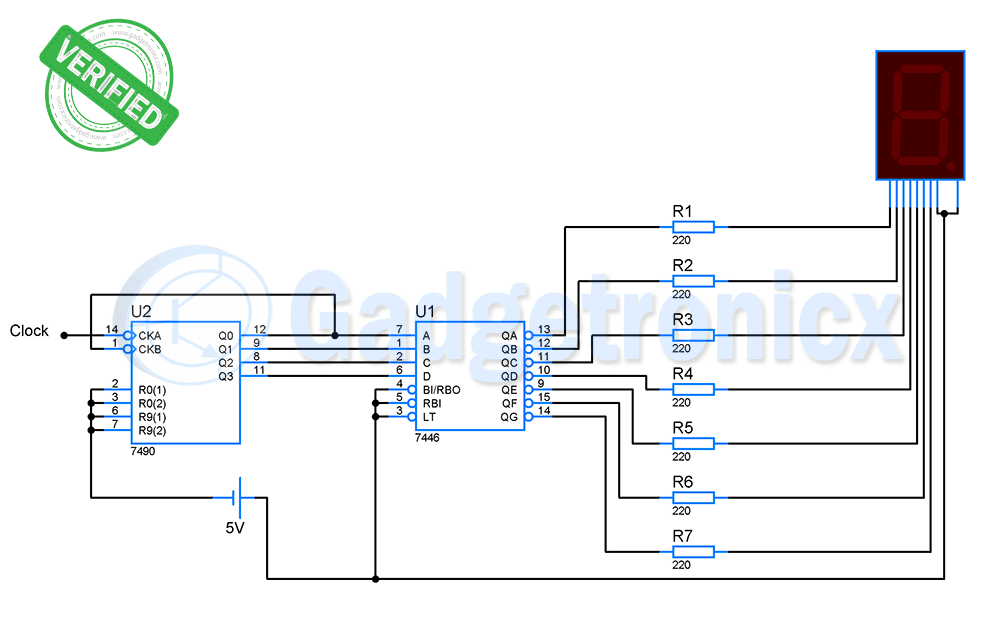

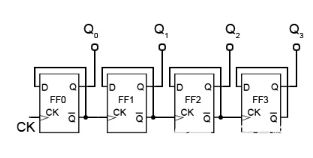

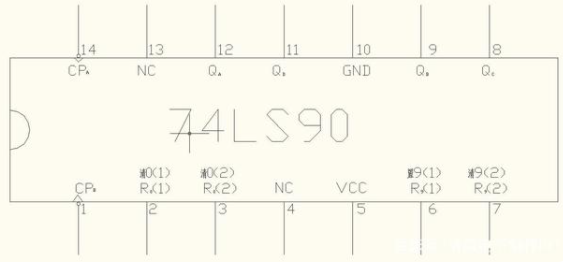

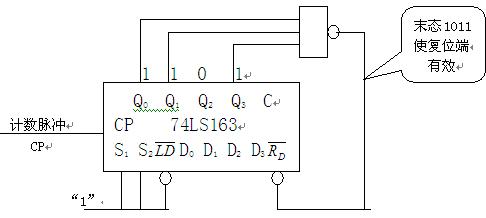

異步十進制遞增計數(shù)器

電子發(fā)燒友App

電子發(fā)燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)>電子技術應用>電子技術>電路圖>數(shù)字電路圖>異步十進制遞增計數(shù)器

相關推薦

435

435

11617

11617

0

0 0

0 2

2 11019

11019

3105

3105

868

868

17

17 73502

73502

34099

34099

12686

12686 6705

6705

6

6 2650

2650 2050

2050 54071

54071

53651

53651

44957

44957

106188

106188

25181

25181

16924

16924

145644

145644

182091

182091

52599

52599

110315

110315

534630

534630

148134

148134

224996

224996

60783

60783

81

81 28

28 24

24 15

15 133

133 3245

3245

330

330 12142

12142 23684

23684 29984

29984 1357

1357

10744

10744

7414

7414 1940

1940

33045

33045

5412

5412

9919

9919

3143

3143

3559

3559 3605

3605

評論