在8月13日舉辦的2020架構(gòu)日上,英特爾發(fā)布了長(zhǎng)達(dá)233頁(yè)的技術(shù)更新,覆蓋制程、封裝、架構(gòu)、軟件等“六大技術(shù)支柱”的方方面面。作為摩爾定律的提出者,英特爾一方面圍繞晶體管密度和性能,推動(dòng)摩爾定律在10nm以下的發(fā)展;另一方面,英特爾正在從晶體管“Reliance(依賴(lài))”走向晶體管“Resilient(彈性)”,通過(guò)“六大技術(shù)支柱”,推動(dòng)計(jì)算性能在當(dāng)前和“后摩爾時(shí)代”的持續(xù)增長(zhǎng),并形成了面向異構(gòu)計(jì)算時(shí)代的整體交付能力,以更有效地應(yīng)對(duì)智能時(shí)代的計(jì)算挑戰(zhàn)。

制程工藝并未止步

2007年,英特爾提出了“Tick Tock”發(fā)展模式,通過(guò)制程演進(jìn)與微架構(gòu)更新,輪換推動(dòng)處理器性能提升。在2016年,英特爾將“Tick Tock”調(diào)整為“PAO”,通過(guò)制程、微架構(gòu)、優(yōu)化三種方式輪流推動(dòng)處理器性能的升級(jí)。

在架構(gòu)日上,英特爾發(fā)布了Superfin技術(shù)。作為FinFet的增強(qiáng)版本,Superfin屬于“O”的范疇,是針對(duì)10nm的晶體管強(qiáng)化工藝。雖然沒(méi)有用“10nm+”來(lái)命名,但Superfin對(duì)于10nm工藝的提升超過(guò)15%,包括更高的驅(qū)動(dòng)電流、通道遷移率,以及更好的芯片互聯(lián)性等。

英特爾院士Ruth Brain表示,Superfin實(shí)現(xiàn)了英特爾史上最強(qiáng)大的單節(jié)點(diǎn)內(nèi)性能增強(qiáng),其提升程度可媲美全節(jié)點(diǎn)轉(zhuǎn)換。

在10nm Superfin之后,英特爾還將推出10nm 增強(qiáng)型Superfin技術(shù),進(jìn)一步提升芯片性能和互聯(lián)能力,并針對(duì)數(shù)據(jù)中心場(chǎng)景進(jìn)行進(jìn)一步的優(yōu)化。

10nm Superfin的性能將達(dá)到何種程度,也引起了業(yè)內(nèi)的廣泛討論。隨著制程進(jìn)入14nm以?xún)?nèi),摩爾定律的實(shí)現(xiàn)越來(lái)越難,逐漸逼近物理極限。即便晶體管密度提升幅度不足一倍,也冠以新的制程節(jié)點(diǎn),已經(jīng)成為許多代工廠商的選擇,這也讓節(jié)點(diǎn)命名越來(lái)越具備市場(chǎng)行為的色彩。

但是,在10nm及以下,英特爾仍在遵循摩爾定律的硬性指標(biāo)。其10nm節(jié)點(diǎn)的晶體管密度達(dá)到100.8MTr/mm2,即每平方毫米內(nèi)包含超過(guò)1億個(gè)晶體管,是14nm節(jié)點(diǎn)的2.7倍。在晶體管密度、鰭片間距、柵極間距等指標(biāo)上,英特爾10nm已經(jīng)超過(guò)了臺(tái)積電、三星的7nm制程。

如果Superfin的性能,能堪比全節(jié)點(diǎn)的轉(zhuǎn)換,那么在10nm指標(biāo)能夠?qū)?biāo)友商7nm的基礎(chǔ)上,Superfin能否對(duì)標(biāo)友商7nm工藝的增強(qiáng)版甚至更先進(jìn)的工藝節(jié)點(diǎn),不免令人浮想聯(lián)翩。當(dāng)然,制程工藝的先進(jìn)性必須在產(chǎn)品中得到驗(yàn)證。英特爾的下一代處理器Tiger Lake,將成為首個(gè)采用10nm Superfin的處理器。目前該處理器已經(jīng)投產(chǎn),預(yù)計(jì)OEM采用Tiger Lake設(shè)計(jì)的產(chǎn)品將在今年之內(nèi)上市。而10nm增強(qiáng)型技術(shù),也將在下一代至強(qiáng)可擴(kuò)展處理器Sapphire Rapids得到驗(yàn)證。

從晶體管Reliance走向晶體管Resilient

無(wú)論是增加晶體管數(shù)量還是提升晶體管性能,都屬于制程工藝的范疇,代表著英特爾繼續(xù)追隨摩爾定律的決心。與此同時(shí),隨著制程微縮逼近極限,如何在“后摩爾時(shí)代”延續(xù)計(jì)算能力的指數(shù)級(jí)增長(zhǎng),成為半導(dǎo)體產(chǎn)業(yè)的重要課題。

在架構(gòu)日上,英特爾首席架構(gòu)師Raja KoduriRaja提到了“Transistor Resilient(晶體管彈性)”的概念。簡(jiǎn)單來(lái)說(shuō),這是與完全依賴(lài)晶體管相對(duì)的產(chǎn)品開(kāi)發(fā)策略,通過(guò)架構(gòu)、封裝、軟件等技術(shù)的“組合拳”,實(shí)現(xiàn)產(chǎn)品性能的提升。

架構(gòu)是硬件設(shè)計(jì)的基礎(chǔ),對(duì)處理器的性能和功耗表現(xiàn)起到?jīng)Q定性作用。本次架構(gòu)日,英特爾發(fā)布了下一代微架構(gòu)“Willow Cove”。為滿(mǎn)足下游客戶(hù)的多樣化需求,Willow Cove提供了更大的動(dòng)態(tài)范圍。相比上一代架構(gòu)Sunny Cove,Willow Cove可以用更低的電壓達(dá)到同樣的主頻,在提高電壓的情況下,可以達(dá)到5GHz左右的最高主頻,滿(mǎn)足創(chuàng)意工作者、游戲愛(ài)好者對(duì)生產(chǎn)力的不同需求。

同樣在架構(gòu)日亮相的,還有英特爾的GPU架構(gòu)Xe,這也是繼1998年推出的i740之后,英特爾再度進(jìn)軍獨(dú)顯市場(chǎng)。Xe提供LP、HP、HPG、HPC四種微架構(gòu)。LP針對(duì)PC和移動(dòng)計(jì)算平臺(tái)等功耗敏感場(chǎng)景,擁有96組EU單元,與Willow Cove類(lèi)似,LP可以通過(guò)加高電壓獲得1.8GHz甚至更高的主頻,提供更強(qiáng)的輸出功率。目前,基于LP架構(gòu)的獨(dú)顯產(chǎn)品“DG1”已經(jīng)實(shí)現(xiàn)量產(chǎn)。HP版本面向數(shù)據(jù)中心級(jí)、機(jī)架級(jí)場(chǎng)景所需的媒體性能,基于英特爾EMIB技術(shù),HP能夠在單封裝中提供千萬(wàn)億浮點(diǎn)運(yùn)算規(guī)模的AI性能和機(jī)架級(jí)的媒體性能,首款產(chǎn)品已經(jīng)向數(shù)據(jù)中心客戶(hù)出樣。HPG面向游戲領(lǐng)域,基于GDDR6的新內(nèi)存子系統(tǒng)提高性?xún)r(jià)比,并具備當(dāng)前熱門(mén)的光線(xiàn)跟蹤能力。HPC架構(gòu)則針對(duì)高性能計(jì)算領(lǐng)域,滿(mǎn)足大規(guī)模的集成部署需要。

硬件能力的釋放,必須基于軟件的通信和調(diào)度。在Xe的設(shè)計(jì)理念中,英特爾強(qiáng)調(diào)了“軟件優(yōu)先”的原則,提升了GPU的編譯和驅(qū)動(dòng)效率,實(shí)現(xiàn)了GPU根據(jù)用戶(hù)配置進(jìn)行性能優(yōu)化以及可變頻率著色、即時(shí)游戲調(diào)整、感知自適應(yīng)游戲銳化等功能,讓GPU能夠更好地滿(mǎn)足3D、媒體、顯示、計(jì)算等不同工作負(fù)載的計(jì)算需求。

先進(jìn)封裝向來(lái)被視為摩爾定律的“救星”,在不依賴(lài)工藝縮小的前提下,先進(jìn)封裝可以繼續(xù)提升芯片的系統(tǒng)集成度。芯片的連接觸電密度、單比特功耗、擴(kuò)展性,是英特爾發(fā)展先進(jìn)制程的主要指標(biāo)。目前,英特爾已經(jīng)形成了2.5D封裝EMIB、3D封裝Foveros,以及混合2D和3D封裝的Co-EMIB等先進(jìn)封裝方案。在架構(gòu)日,英特爾發(fā)布了“混合結(jié)合”技術(shù),能夠加速實(shí)現(xiàn)10微米及以下的凸點(diǎn)間距,較Fovreros 25-50微米的凸點(diǎn)間距有明顯提升,并優(yōu)化了互連密度、帶寬和功率表現(xiàn),進(jìn)一步提升芯片系統(tǒng)的計(jì)算效能。

基于異構(gòu)整合提升交付能力

新冠肺炎疫情是攪動(dòng)全球經(jīng)濟(jì)的黑天鵝。疫情的沖擊導(dǎo)致全球消費(fèi)者信心下降,手機(jī)等消費(fèi)終端出貨量出現(xiàn)回落。與此同時(shí),遠(yuǎn)程服務(wù)和“宅經(jīng)濟(jì)”異軍突起,服務(wù)器成為疫情之下驅(qū)動(dòng)半導(dǎo)體增長(zhǎng)的重要?jiǎng)幽堋?/p>

半導(dǎo)體作為精密產(chǎn)業(yè),生產(chǎn)周期較長(zhǎng)。面對(duì)疫情帶來(lái)的市場(chǎng)需求變化,半導(dǎo)體企業(yè)能否利用技術(shù)積累和產(chǎn)業(yè)鏈合作生態(tài),保持快速交付的能力,實(shí)現(xiàn)“化危為機(jī)”,成為企業(yè)運(yùn)營(yíng)能力的試金石。從財(cái)報(bào)來(lái)看,英特爾抓住了市場(chǎng)變化帶來(lái)的機(jī)遇。當(dāng)季,英特爾以PC為中心的傳統(tǒng)強(qiáng)勢(shì)業(yè)務(wù)同比增長(zhǎng)7%,數(shù)據(jù)中心業(yè)務(wù)則強(qiáng)勢(shì)增長(zhǎng)43%,營(yíng)收和凈利潤(rùn)均實(shí)現(xiàn)超過(guò)超過(guò)20%的增長(zhǎng)。

在架構(gòu)日上,英特爾展現(xiàn)了基于分解設(shè)計(jì)和軟件平臺(tái)的異構(gòu)集成,進(jìn)一步提升不同產(chǎn)品交付能力的策略。

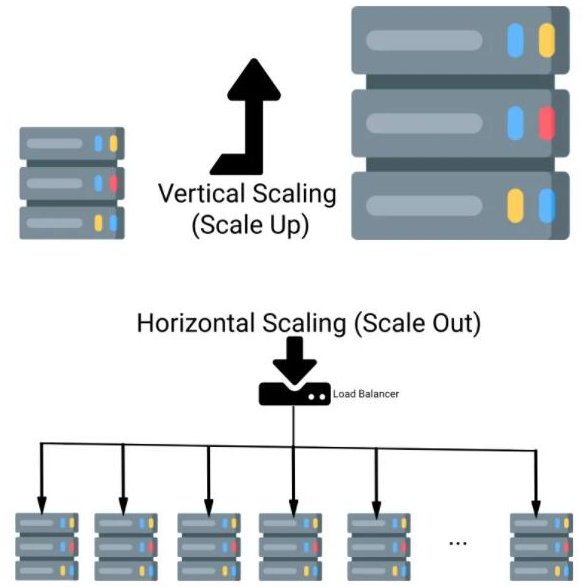

所謂異構(gòu)計(jì)算,是將多種架構(gòu)、功能的芯片封裝在一個(gè)SoC,以處理或加速不同工作負(fù)載的硬件集成方式。如果像拼搭積木一樣,將生產(chǎn)好的芯片、裸片封裝在一起,形成系統(tǒng)級(jí)芯片,將顯著提升硬件產(chǎn)品的交付速度,滿(mǎn)足AI、IOT等場(chǎng)景對(duì)于芯片的多樣化、差異化需求。

通過(guò)分解設(shè)計(jì),英特爾將異構(gòu)計(jì)算芯片化繁為簡(jiǎn),分解為不同的部分,分別進(jìn)行整合和驗(yàn)證。由于不是一次性整合所有芯片,而是按照CPU、GPU、IO等計(jì)算功能分別去做,預(yù)生產(chǎn)的芯片、已經(jīng)成熟的IP無(wú)需再次進(jìn)行工藝驗(yàn)證,可直接復(fù)用。從而縮短了開(kāi)發(fā)和驗(yàn)證時(shí)間,降低了差錯(cuò)率,也增強(qiáng)了系統(tǒng)級(jí)芯片的靈活性,可以更加便捷地進(jìn)行功能擴(kuò)展。

在異構(gòu)計(jì)算時(shí)代,利用軟件系統(tǒng)隱藏硬件復(fù)雜性,讓異構(gòu)計(jì)算平臺(tái)以“黑盒”的方式被客戶(hù)獲取并使用,對(duì)于產(chǎn)品的開(kāi)發(fā)和交付尤為重要。oneAPI是英特爾生態(tài)構(gòu)建的野心之作,提供了跨平臺(tái)的工具鏈、編譯器、調(diào)試工具和遷移工具等,以及統(tǒng)一的開(kāi)發(fā)環(huán)境,這意味著用戶(hù)不必為了不同的芯片架構(gòu)重新學(xué)習(xí)編程知識(shí),從而降低了異構(gòu)計(jì)算的開(kāi)發(fā)難度。oneAPI Gold版本將于今年晚些時(shí)候推出,為開(kāi)發(fā)人員提供在標(biāo)量、矢量、距陣和空間體系結(jié)構(gòu)上保證產(chǎn)品級(jí)別的質(zhì)量和性能的解決方案。英特爾于7月發(fā)布的第八版的oneAPI Beta,為分布式數(shù)據(jù)分析帶來(lái)了新的功能和提升,包括渲染性能、性能分析以及視頻和線(xiàn)程文庫(kù)。

基于更加靈活的硬件集成方式和強(qiáng)調(diào)易用性的軟件平臺(tái),英特爾可以更有效地打通芯片級(jí)、系統(tǒng)級(jí)、軟件級(jí)異構(gòu)能力,提供定制化的產(chǎn)品方案和更短的交付周期。從底層的制程和封裝,到中層的架構(gòu)、存儲(chǔ)、互連、軟件,到最頂層的安全,“六大技術(shù)支柱”都將在英特爾的異構(gòu)計(jì)算戰(zhàn)略中發(fā)揮作用,共同應(yīng)對(duì)智能時(shí)代數(shù)據(jù)量指數(shù)級(jí)增長(zhǎng)和數(shù)據(jù)形態(tài)更加多元的算力挑戰(zhàn)。

? ? ? ?責(zé)任編輯:tzh

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論